# NTP3000 1 CHIP 2.1 CHANNEL FULL DIGITAL AMPLIFIER

#### **Features**

- Stereo (30W × 2)

- 2.1 channel (15W × 2 + 30W)

- Wide Supply Voltage Range (7V~30V)

- Floating Point Operation

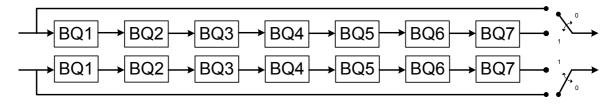

- 18 Programmable Biquad Filters

- Speaker Compensation

- DC cut, LPF, HPF

- Parametric Equalizer

- PWM Output for External Subwoofer

- 3D Surround

- 7 Band Graphic Equalizer

- 100 dB Dynamic Range

- Adaptive Loudness Compensator based on Psycho Acoustics

kHz. It delivers 2x30W in stereo mode or 2x15W + 1x30W in 2.1 channel mode without heat sink.

Combining use of built-in mixer and biquad filters can make additional preprocessing like bass management, loudness control, loudspeaker response compensation and preset parametric equalizers possible.

All the functions of NTP3000 are set by I<sup>2</sup>C register configuration.

### **Applications**

- Plasma TV, LCD TV

- Docking Station

- Mini-Component Audio

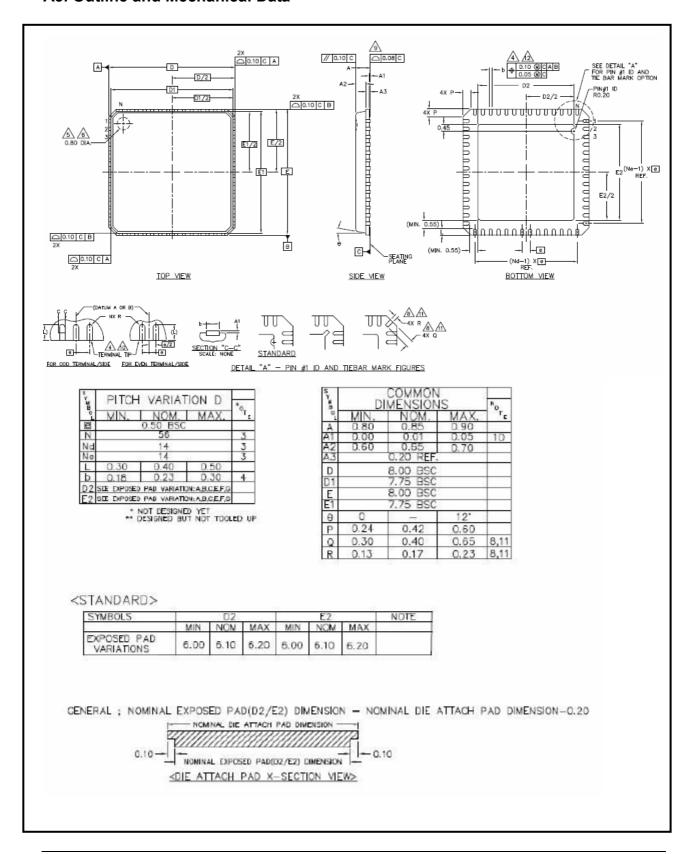

### Package |

56 pin MLF 8mm by 8mm

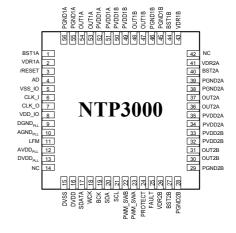

Figure 1 NTP3000 Pin Assignment

### Description

NTP3000 is a single chip full digital audio amplifier including power stage for stereo or 2.1 channel amplifier system. NTP3000 is integrated with versatile digital audio signal processing functions, high-fidelity fully digital PWM modulator and two high-power full bridge MOSFET stages.

NTP3000 receives 2-channel serial audio data with sampling frequency from 8 kHz to 192

NeoFidelity, Inc. #1009, Ace Twin Tower 2, 212-30, Guro-dong, Guro-gu, Seoul 152-766 Korea, Phone +82-2-6675-1100, Fax +82-2-6675-1109, Email <a href="mailto:info@neofidelity.com">info@neofidelity.com</a>, Web <a href="https://www.neofidelity.com">www.neofidelity.com</a></a> Copyright © NeoFidelity, Inc. 2005 All rights Reserved. June, 2005

#### Disclaimer

NeoFidelity, Inc. reserves the right to make changes without notice in the product described in this datasheet

including circuits, software and ICs, described herein for the purpose of improvement of design and performance. NeoFidelity, Inc. assumes no responsibilities and liabilities for the use of the product, conveys no license under any patent or copyright, and makes no warranties that the product is free from patent or copyright infringement, unless otherwise specified.

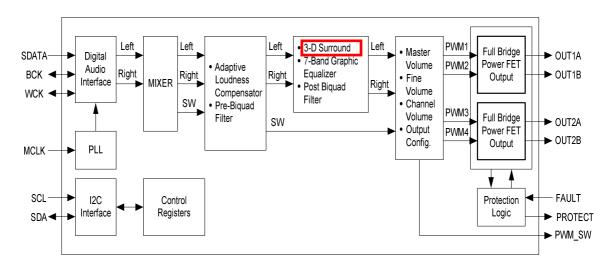

### 1. BLOCK DIAGRAM

Figure 2 NTP3000 Block Diagram

### 2. PIN DESCRIPTIONS

|        | DIV.                |                    |                                                               |  |  |

|--------|---------------------|--------------------|---------------------------------------------------------------|--|--|

| PIN    | NAME                | TYPE <sup>1)</sup> | DESCRIPTION                                                   |  |  |

| 1      | BST1A               | P                  | Bootstrap supply, external capacitor to OUT1A is required     |  |  |

| 2      | VDR1A               | Р                  | Gate drive voltage regulator decoupling pin, capacitor to GND |  |  |

| 3      | /RESET              | I                  | Active Low to reset NTP3000, Schmitt trigger input            |  |  |

| 4      | AD                  | I                  | I2C device Address selection                                  |  |  |

| 5      | VSS_IO              | -                  | Ground                                                        |  |  |

| 6      | CLK_I               | I                  | System master clock input                                     |  |  |

| 7      | CLK_O               | 0                  | System master clock output                                    |  |  |

| 8      | VDD_IO              | Р                  | voltage supply for I/O, 3.3V                                  |  |  |

| 9      | DGND <sub>PLL</sub> | -                  | Ground                                                        |  |  |

| 10     | AGND <sub>PLL</sub> | -                  | Ground                                                        |  |  |

| 11     | LFM                 | I                  | External loop filter                                          |  |  |

| 12     | AVDD <sub>PLL</sub> | Р                  | voltage supply for PLL analog circuit, 1.8V                   |  |  |

| 13     | DVDD <sub>PLL</sub> | Р                  | voltage supply for PLL digital circuit, 1.8V                  |  |  |

| 14     | VSS                 | _                  | Ground                                                        |  |  |

| 15     | DVSS                | -                  | Ground                                                        |  |  |

| 16     | DVDD                | Р                  | voltage supply for core logic, 1.8V                           |  |  |

| 17     | SDATA <sup>2)</sup> | ı                  | I <sup>2</sup> S serial data input                            |  |  |

| 18     | WCK <sup>2)</sup>   | I/O                | I <sup>2</sup> S word clock                                   |  |  |

| 19     | BCK <sup>2)</sup>   | I/O                | I <sup>2</sup> S bit clock                                    |  |  |

| 20     | SDA <sup>2)</sup>   | I/O                | I <sup>2</sup> C data                                         |  |  |

| 21     | SCL <sup>2)</sup>   | I                  | I <sup>2</sup> C clock                                        |  |  |

| 22     | PWM_SWB             | 0                  | PWM output for external subwoofer, negative                   |  |  |

| 23     | PWM_SWA             | 0                  | PWM output for external subwoofer, positive                   |  |  |

| 24     | PROTECT             | 0                  | External power stage on/off control to protect                |  |  |

| 25     | FAULT               | I                  | input from external power stage                               |  |  |

| 26     | VDR2B               | Р                  | Gate drive voltage regulator decoupling pin, capacitor to GND |  |  |

| 27     | BST2B               | Р                  | Bootstrap supply, external capacitor to OUT1A is required     |  |  |

| 28, 29 | PGND2B              | _                  | Ground                                                        |  |  |

| 30, 31 | OUT2B  | 0 | Power stage PWM output 2B                                     |

|--------|--------|---|---------------------------------------------------------------|

| 32, 33 | PVDD2B | Р | Voltage supply for power stage                                |

| 34, 35 | PVDD2A | Р | Voltage supply for power stage                                |

| 36, 37 | OUT2A  | 0 | Power stage PWM output 2A                                     |

| 38, 39 | PGND2A | - | Ground                                                        |

| 40     | BST2A  | Р | Bootstrap supply, external capacitor to OUT2A is required     |

| 41     | VDR2A  | Р | Gate drive voltage regulator decoupling pin, capacitor to GND |

| 42     | NC     | - | No connection                                                 |

| 43     | VDR1B  | Р | Gate drive voltage regulator decoupling pin, capacitor to GND |

| 44     | BST1B  | Р | Bootstrap supply, external capacitor to OUT2A is required     |

| 45, 46 | PGND1B | - | Ground                                                        |

| 47, 48 | OUT1B  | 0 | Power stage PWM output 1B                                     |

| 49, 50 | PVDD1B | Р | Voltage supply for power stage                                |

| 51, 52 | PVDD1A | Р | Voltage supply for power stage                                |

| 53, 54 | OUT1A  | 0 | Power stage PWM output 1A                                     |

| 55, 56 | PGND1A | - | Ground                                                        |

- 1) P = Power, I = Input, O = Output, I/O = Input/Output

- 2) 5V tolerant. Normal I/O pins are 3.3V tolerant if not specified.

- 3) TEST0 Pin should be connect Ground Pin.

### 3. CHRACTERISTICS AND SPECIFICATIONS

### 3.1. Absolute Maximum ratings

| Parameter            | Reference | Rating        | Unit     |

|----------------------|-----------|---------------|----------|

| DVDD voltage         | DVSS      | -0.5 ~ 2.5    | V        |

| VDD_IO voltage       | VSS_IO    | -0.5 ~ 4.4    | V        |

| Logic Input voltage  | VSS_IO    | -0.5 ~ 5.5    | V        |

| Logic output voltage | VSS_IO    | -0.5 ~ 4.4    | <b>V</b> |

| PVDDXX voltage       | PGNDXX    | 32            | <b>V</b> |

| OUTXX voltage        | PGNDXX    | -0.3 ~ PVDDXX | <b>V</b> |

| BSTXX voltage        | PGNDXX    | 40            | <b>V</b> |

| VDRXX voltage        | PGNDXX    | 8             | V        |

| Storage Temperature  | Tstg      | -65 ~ 150     | °C       |

### 3.2. Recommended Operating Conditions

| Parameter                     | Reference | Rating      | Unit |

|-------------------------------|-----------|-------------|------|

| DVDD voltage                  | DVSS      | 1.62 ~ 1.98 | V    |

| VDD_IO voltage                | VSS_IO    | 2.97 ~ 3.63 | V    |

| PVDDXX voltage                | PGNDXX    | 7 ~ 30      | V    |

| VDRXX voltage                 | PGNDXX    | 6           | V    |

| Peak output current           | -         | 8           | А    |

| Ambient Operating temperature | Tamb      | -10 ~ 85    | °C   |

#### 3.3. DC Electrical Characteristics

| Parameter                                 | Symbol          | Condition | Min  | Тур  | Max  | Unit |

|-------------------------------------------|-----------------|-----------|------|------|------|------|

| Input High Voltage                        | $V_{ih}$        | =         | 2.0  |      | 5.5  | V    |

| Input Low Voltage                         | V <sub>il</sub> | =         | -0.3 |      | 0.8  | V    |

| Threshold point                           | V <sub>t</sub>  | =         | 1.45 | 1.58 | 1.74 | V    |

| Schmitt trig. Low to High threshold point | $V_{t+}$        | -         | 1.44 | 1.50 | 1.56 | V    |

| Schmitt trig. High to                     | $V_{t-}$        | -         | 0.89 | 0.94 | 0.99 | V    |

| Low threshold point                 |                 |                            |     |      |      |    |

|-------------------------------------|-----------------|----------------------------|-----|------|------|----|

| Input Leakage Current               | I <sub>I</sub>  | -                          |     |      | ±10  | uA |

| Tri-State output<br>Leakage Current | l <sub>oz</sub> | -                          |     |      | ±10  | uA |

| Pull-up Resistor                    | $R_{pu}$        | -                          | 39k | 65k  | 116k | Ω  |

| Pull-down Resistor                  | $R_{pd}$        | -                          | 40k | 56k  | 108k | Ω  |

| Output Low Voltage                  | V <sub>ol</sub> | I <sub>ol</sub> =2,4,24mA  |     |      | 0.4  | ٧  |

| Output High Voltage                 | $V_{oh}$        | I <sub>oh</sub> =2,4,24mA  | 2.4 |      |      | V  |

| Output Low Current                  | l <sub>ol</sub> | V <sub>ol</sub> =0.4V, 4mA | 4.7 | 8.0  | 10   | mA |

| Output High Current                 | l <sub>oh</sub> | V <sub>oh</sub> =2.4V, 4mA | 5.6 | 11.9 | 19   | mA |

| OUT On Resistance                   | $R_{dson}$      | PVDDXX=7.5V                |     | 0.1  |      | Ω  |

| OUT Current Limit                   |                 | Sourcing and Sinking       |     | 8    |      | Α  |

| Thermal Shutdown Temperature        |                 |                            |     | 160  |      | °C |

#### 3.4. Performance Specification

| Parameter    | Condition                 | Min | Тур     | Max | Unit |

|--------------|---------------------------|-----|---------|-----|------|

| SNR          | AES17, A-weighting filter |     | 100     |     | dB   |

| THD+N        | 1W, 1kHz                  |     | 0.01    |     | %    |

| Output Power | Unclip                    |     | 2x30    |     | W    |

| Output Power | Unclip                    |     | 2x15+30 |     | W    |

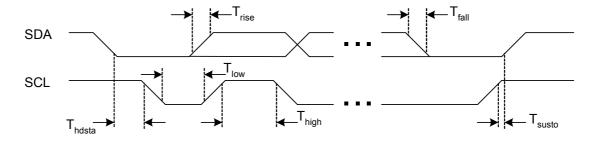

#### 3.5. Switching Characteristics – I<sup>2</sup>C Control Port

| Parameter                        | Symbol             | Min  | Max  | Unit |

|----------------------------------|--------------------|------|------|------|

| SCL Clock Frequency              | f <sub>scl</sub>   | -    | 400  | kHz  |

| Hold time for START Condition    | T <sub>hdsta</sub> | 4000 | -    | ns   |

| Low period of the SCL clock      | $T_low$            | 4700 | -    | ns   |

| High period of the SCL clock     | $T_{high}$         | 4000 | -    | ns   |

| Rise time of SDA and SCL signals | T <sub>rise</sub>  | ı    | 1000 | ns   |

| Fall time of SDA and SCL signals | $T_{fall}$         | ı    | 300  | ns   |

| Setup time for STOP Condition    | T <sub>susto</sub> | 4000 | -    | ns   |

Figure 3 I<sup>2</sup>C Mode timing

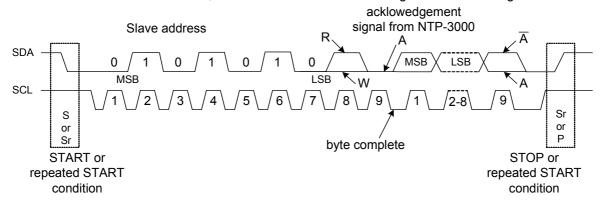

### 4. I2C Control of NTP3000

All the functions of NTP3000 are controlled by register setting through built-in I<sup>2</sup>C host interface.

#### 4.1. Start Condition and Stop Condition

I<sup>2</sup>C bus of NTP3000 is composed of serial clock line (SCL) and serial data line (SDA). SDA can be changed only when SCL is in low state with exceptions of start condition or stop condition. START condition means that master is to start transferring data to slave. To make START condition, transit SDA state from high to low when SCL is high. STOP condition means that master is to finish transferring data to slave. To make STOP condition, transit SDA state from low to high when SCL is high.

Figure 4 START Condition and STOP Condition

#### 4.2. I2C Address

The I2C Address of NTP3000 is composed of 7-bit except for Acknowledge bit with 7<sup>th</sup> bit depending on AD pin input (**Table 1**). If AD is low or pulled down, the Address is 0x54 and if AD is high or pulled up it is 0x56.

| AD | I2C Address |

|----|-------------|

| 0  | 0x54        |

| 1  | 0x56        |

Table 1 I2C Address

#### 4.3. Write or Read

A bit after 7-bit slave Address means to WRITE (0) or to READ (1).

#### 4.3.1. Writing to NTP3000

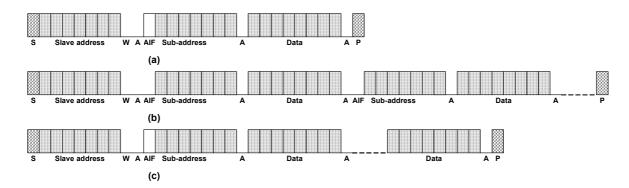

I2C data can be written on NTP3000 by using modified I<sup>2</sup>C write operation. **Figure 5** (a) shows writing 1-byte register data procedure. Followed by START condition, master notices the data transfer mode to NTP3000 by sending slave Address with WRITE operation bit (W). NTP3000 sends acknowledgement bit (ACK) to master when it receives the slave Address correctly and is ready for response. After checking the ACK, master sends NTP3000 the sub-Address which means the register Address of NTP3000. The sub-Address is composed of 7-bit register Address and 1-bit Auto Increment Flag (AIF). When NTP3000 receives the sub-Address correctly, NTP3000 sends ACK to master. After checking the ACK, master sends data which means the register value to NTP3000. Master checks ACK and 1-byte register data writing procedure is finished by initiating the STOP condition.

#### Notice)

If the sub-Address is floating point coefficient register (0x40  $\sim$  0x5F), 4-byte register data should be written.

AIF is used for writing multi-byte to NTP3000. Multi-byte register data writing procedure is shown in **Figure 5** (b), (c).

Figure 5 Write Mode Sequence

If AIF=0, sub-Address and data can be repeatedly written after master sends NTP3000 the slave Address with write operation bit (W) and checks ACK from NTP3000.

If AIF=1, data can be repeatedly written with auto-incremented Address.

#### 4.3.2. Read Operation from NTP3000

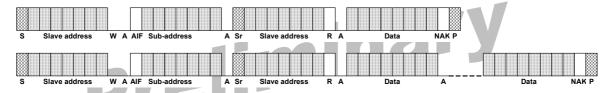

Master can read data from NTP3000 by using combined format. **Figure 6** shows all the possible procedures of read operation in NTP3000.

Figure 6 Read Mode Sequence

Followed by START condition, master notices the data transfer mode by sending the slave Address with write operation bit (W). After checking ACK, master sends NTP3000 the sub-Address with AIF=1 and checks ACK from NTP3000. To change the operation from writing to reading, master sends the START condition without STOP condition as repeated start condition (Sr). Followed by Sr, master resends the slave Address with reading operation bit (R) and checks ACK. Then master can read 1-byte or multibytes from NTP3000. To finish the reading operation, master sends NAK data and STOP condition after reading the last byte.

#### 4.3.3. Downloading biquad filter coefficients and loudness gain

There are 33 programmable biquad filters. To download the filter coefficients of each biquad, the biquad filter page flag should be set appropriate value.

The number of registers is shown in Table 2.

|                                                                             | 0x40 ~ 0x44 | 0x45 ~ 0x49 | 0x4A ~ 0x4E | 0x4F ~ 0x53 | 0x54 ~ 0x58 |

|-----------------------------------------------------------------------------|-------------|-------------|-------------|-------------|-------------|

| Post Biquad of CH1<br>(0x3F = 0x01 case)                                    | BQ1         | BQ2         | BQ3         | BQ4         | BQ5         |

| Post Biquad of CH2<br>(0x3F = 0x02 case)                                    | BQ1         | BQ2         | BQ3         | BQ4         | BQ5         |

| GEQ of CH1<br>(GEQC flags of 0x06<br>register = 0b11 &<br>0x3F = 0x04 case) | BQ1         | BQ2         | BQ3         | BQ4         | BQ5         |

| GEQ of CH2<br>(GEQC flags of 0x06<br>register = 0b11 &<br>0x3F = 0x08 case) | BQ1        | BQ2        | BQ3          | BQ4          | BQ5        |

|-----------------------------------------------------------------------------|------------|------------|--------------|--------------|------------|

| 3D filter<br>(0x3F = 0x10 case)                                             | BQ1 of CH1 | BQ2 of CH1 | BQ1 of CH2   | BQ2 of CH2   | Х          |

| Various1                                                                    | BQ of ALC  | BQ1 of Ch1 | BQ2 of Ch1   | BQ1 of Ch2   | BQ2 of Ch2 |

| (0x3F = 0x20 case)                                                          |            | Pre-biquad | Pre-biquad   | Pre-biquad   | Pre-biquad |

| Various2                                                                    | BQ1 of Ch3 | BQ2 of Ch3 | BQ8 in Post- | BQ9 in Post- | Х          |

| (0x3F = 0x40 case)                                                          | Pre-biquad | Pre-biquad | Biquad       | Biquad       |            |

**Table 2 Biquad filters**

When the filter coefficients to download are same for, e.g. post biquad of ch1 and ch2 then set the register 0x3F as 0x3.

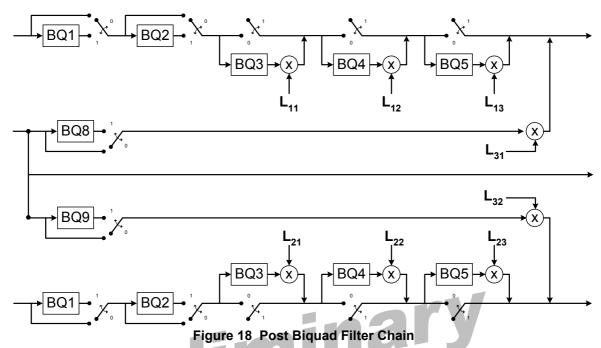

There are 8 loudness gains in post-biquad chain. To download loudness gain of each biquad, page flag register 0x3F should be set as in the case of downloading the filter coefficients.

|                                         | 0x59 | 0x5A | 0x5B |

|-----------------------------------------|------|------|------|

| loudness gains of CH1(0x3F = 0x01 case) | L11  | L12  | L13  |

| loudness gains of CH2(0x3F = 0x02 case) | L21  | L22  | L23  |

| loudness gains of CH3(0x3F = 0x80 case) | L31  | L32  | Х    |

Table 3 Loudness gain

### 5. Clock, Reset & Control

#### 5.1. System Clock

The internal system clock of NTP3000 is generated from external master clock by PLL. NTP3000 supports external master clock frequency from 8.192 MHz to 24.576MHz. For proper operation, PLL should be set correctly according to master frequency (Table ).

#### 5.2. Reset

When hardware RESET pin is set to low state, NTP3000 is brought into the reset state to bring up the actions as follow.

- 1) Each control register resets to the default value.

- 2) All the internal registers, multipliers, adders, counters, and etc. are cleared to zero.

- 3) All of the output pins keep low state as long as the RESET is active.

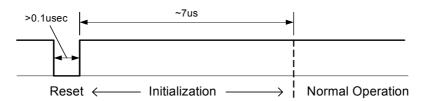

It takes about  $7\mu s$  after reset pin is remained low for more than 0.1usec to finish the above operations as shown in Figure 7.

Figure 7 Reset timing

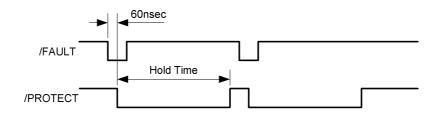

### 5.3. Fault and protect Control

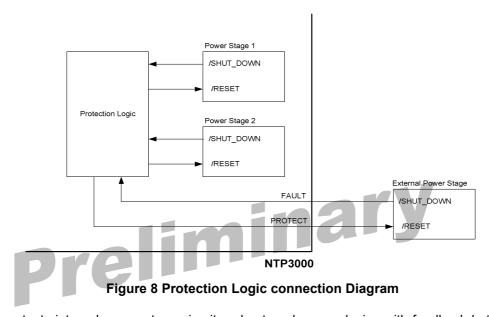

NTP3000 protects internal power stage circuit and external power device with feedback between power stage and protection logic as shown in Figure 8. When a power stage falls in protection condition, it shuts down by itself informing protection logic 'fault' as shown in Figure 9. As soon as protection logic receives the information, the output of 'PROTECT' becomes low to turn off all the power stages for a 'Hold Time' which is configurable. After 'Hold Time' has passed, protection logic tries to turn on power stage circuits again. If power stage circuit still suffers from protection problem, protection logic keeps on turning on and off until the condition which is configured on control registers.

Figure 9 Fault, Protect pin Timing Diagram

When FAULT signal is changed from high to low, PROTECT signal changes from high to low after 0.06usec. When this happens, PROTECT signal remains low even the FAULT signal changes to high.

PROTECT signal is changed to high by the FAULT signal after Hold Time and at the same time it increases Auto PROTECT restore counter value by 1.

If the counter value reaches AVRCT (Auto PROTECT Restore Counter Threshold) in Auto PROTECT restore interval, the PROTECT signal becomes low permanently. Designers can detect this permanent low state by reading PPM flag in register Address 0x75 and change the permanent low state to high by setting Auto PROTECT restore counter value to 0 by using FPMLD flag in register Address 0x1E. Also, designers can control the PROTECT signal directly by using PWMM flag in register Address 0x1E.

Auto PROTECT restore interval is defined by PHT, AVRCT, IRC flags in register Address 0x1D and the default value is PHT \* AVRCT \* IRC = 4 \* 5 \* 2 = 40msec.

#### 6. Audio Input

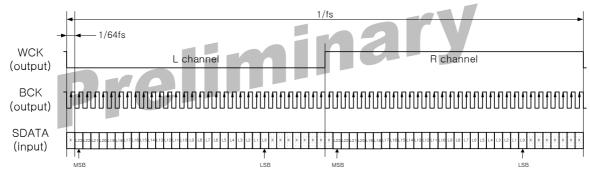

### 6.1. I<sup>2</sup>S and Serial Audio Interface

Serial audio port of NTP3000 can be configured as either the master or slave mode, and BCK(bit clock) and WCK(word clock) are bi-directional pins depending on the clock mode setting. In the master mode, WCK( $f_s$ ) and BCK(configurable) are output signals from the NTP3000, and the external DSP receiver delivers SDATA signal synchronized with them. NTP3000 accepts WCK and BCK signal along with SDATA coming from external devices in the slave mode. INS flag determines clock mode between master and slave mode.

<sup>\*</sup> WCK and BCK are output when master mode, and input when slave mode.

Figure 10 Serial audio interface format

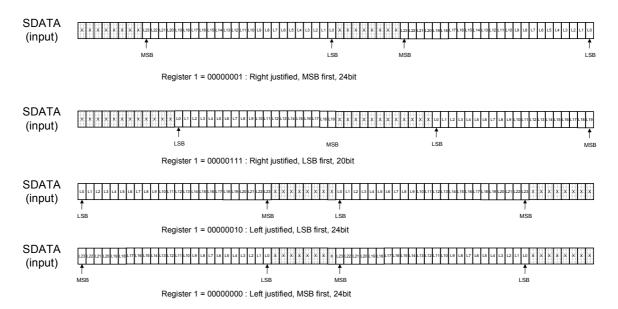

For general serial mode other than I<sup>2</sup>S, the format of data can be changed by LRJ(Left, Right Justify), MLF(MSB, LSB First)and BS(Bit Size) flags of register Address 0x01. <u>Figure 11</u> shows some examples of general serial audio formats and their register settings.

Figure 11 General serial audio data formats

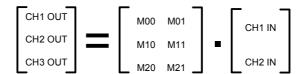

### 7. Mixer

Channel mixer can be used in lots of application needs like bass management, subwoofer signal generation, pseudo stereo, etc. Mixer cross-connects two input channels to three output channels. Mixer can control both gain and polarity of each channel input. Step size of mixer gain change is also variable according to the gain level as shown below.

Table 4 Variable step mixing gain

| Volume Range(dB) | Step(dB) |

|------------------|----------|

| +18 ~ + 6        | 1        |

| +5.5 ~ -5.5      | 0.5      |

| -6 ~ -32         | 1        |

| < -32            | -8       |

In total, 6 mixing gain coefficients denoted as M00, M01, M10,..., M21 are defined as shown in the equation below. Each Mxx stores volume value in dB scale, and the number values versus gain in dB are shown in the <u>appendix</u>. There are some places in the mixing matrix that are considered as trivial connections and thus predefined as  $-\infty$  dB.

[Output Channels] = [Mixer Matrix] x [Input Channels]

Figure 12 Mixer matrix

In order to load mixer coefficients into internal memory, send the coefficient value itself to the register Address  $0x37 \sim 0x3C$ . Total 6 registers are preserved and matched to M00, M01, M10, M11, M20, M21, sequentially.

### 8. Pre-processing

#### 8.1. Adaptive Loudness Compensation

NTP3000 supports Adaptive Loudness Control (ALC) function. This function makes the identical input signal level without sacrificing the dynamic range.

The difference with the Dynamic Range Compression (DRC) function described in <u>Section 9</u> is as follows; DRC sustains the signal level when volume is operating but ALC sustains the signal level when volume is not operating – that means ALC sustains the signal level of the original input source. Also, DRC operation is performed by peak detection scheme and ALC is performed by energy detection scheme.

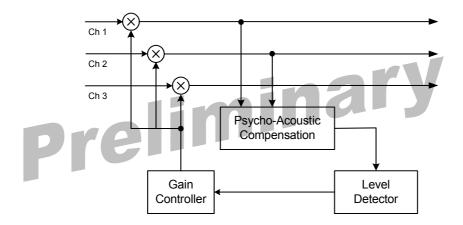

ALC structure of NTP3000 is shown in Figure 13.

Figure 13 Adaptive Loudness Compensation Diagram

ALC can be useful to compensate the signal level difference of different channels and different programs in same channel in TV related product applications. There is a biquad filters in the Psycho-Acoustic Compensation block. To download the filter coefficients of this biquad, the page flag register 0x3F should be set to 0x20 and the five 32 bit coefficients should be downloaded to 0x40 ~ 0x44. See the system register Addresses 0x07~09, 0x3F, 0x40~44 in the <u>Appendix 1</u>. The downloading method will be described in detail on the separate application note.

#### 8.2. Pre Biguad Filter Chain

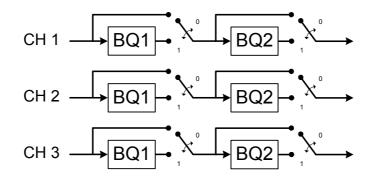

NTP3000 has two kinds of biquad filter chains. One is Pre biquad filter chain and the other is Post Biquad filter chain for bass management, loudness control, loud-speaker EQ, etc. The former is called pre-biquad filter chain and two 2<sup>nd</sup> order floating point biquad filters are connected serially to all the three channels. The structure is shown in Figure 14.

Figure 14 Biquad Filter Structure

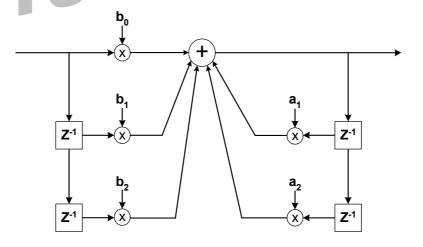

Filter coefficients are 32-bit floating point numbers and can be downloaded thru I<sup>2</sup>C interface. To download the pre-biquad filter coefficients to internal memory of NTP3000, designer should change the Various 1 for Channel 1&2 and Various 2 for Channel 3 flags of register Address 0x3F to 'enable coefficient write' status. And then write the actual coefficient values to ten register Addresses, from 0x40 to 0x53.

When Various 1 Flag of Address 0x3F is set to 1, Address 0x40~44 designates coefficients of 1<sup>st</sup> prebiquad filter chain of channel 1 and indicates b0, b1, b2, a1, a2 respectively. Address 0x45~49 designates the coefficients of 2<sup>nd</sup> chain of channel 1, 0x4A~4E for 1<sup>st</sup> chain of channel 2, and 0x4F~53 for 2<sup>nd</sup> chain of channel 2.

When Various 2 Flag of Address 0x3F is set to 1, Address 0x40~44 designates coefficients of 1<sup>st</sup> prebiquad filter chain of channel 3 and Address 0x45~49 designates the coefficients of 2<sup>nd</sup> chain of channel 3

The biquad filter structure is shown in Figure 15

Figure 15 Biquad Filter Structure

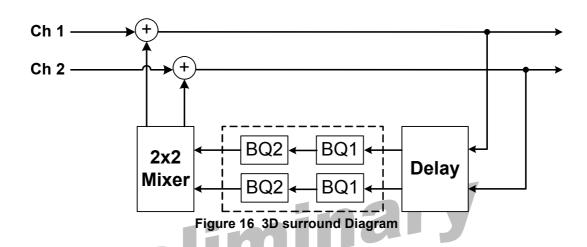

#### 8.3. 3D Surround

3D surround expands the sound field of two channel stereo to the extent that is wider than the actual speaker spacing. Because this feature is acoustically valid for two channel signal, no other channels except channel 1/2 have this internal block.

NTP3000 realizes the 3D effect by combining delay and band-pass filter. At first, define the size of delay by using register Address 0x60. Possible maximum delay is 40 samples delay and this is about 0.4msec based on 96kHz signal input.

And then download the band-pass filter coefficients to internal memory of NTP3000(same with the biquad filter coefficient download procedure). The BPF is two 2<sup>nd</sup> order IIR filter. Each channel can have different BPF. Change the 3D flag status of register Address 0x3F to 'enable coefficient write' status and write the actual coefficient values to twenty register Addresses 0x40~ 0x53. Also, internal 2x2 mixer helps ease of design. For using 3D mixer, download the gain values to four register Addresses 0x5C~0x5F.

#### 8.4. Configurable Graphic Equalizer

NTP3000 provides 7 or 5 band graphic equalizer and tone control to 1/2 channel. EQ on/off can be selected by GEQC flag of register Address 0x06.

The gains for each band can be controlled by writing the gain values (refer Graphic equalizer band gain table in <u>Appendix 2</u>) to register Addresses 0x32~36 respectively.

In tone control mode the BQ1 ~ BQ5 can be used as programmable biquad filters.

Figure 17 GEQ filter structure

### 8.5. Post Biquad Filter Chain

The post biquad filter chains of NTP3000 can be used in various purposes - bass management, loudness control, parametric EQ, loud-speaker EQ, etc.Independent filter design for 1, 2 channels are possible and five 2<sup>nd</sup> order floating point parametric filters are linked serially. Especially for loudness control, as shown in Figure 18, last 3 filters are different from first 2 filters.

Filter coefficients are 32-bit floating point numbers and can be downloaded thru I<sup>2</sup>C interface. To download post biquad filter coefficients to NTP3000, select download channel by using CH flag in register Address 0x3F first. And then write actual coefficient values to 25 register Addresses, from 0x40 to 0x58.

Address 0x40~44 designates 1<sup>st</sup> chain coefficients and means b0, b1, b2, a1, a2 in sequence. Address 0x45~49designates 2<sup>nd</sup> chain, and so on.The enable/disable operation of these biquads can be made by using BQF flag in register Addresses 0x3D~3E.

For the enhancement of 3D effect or redirection of Bass signal back into Main channel, Ch3 fire back structure is integrated like Figure 14.

#### 8.6. Loudness

NTP3000 provides loudness control function using post biquad filter chains. Loudness control means the compensation of frequency characteristics in low volume level to fit the human ear condition.

### 9. Volume & Dynamic Range Control

Master and channel volumes are independently controlled and softly changed. The system register Address 0x2E is the master volume control that affects all 3 channels simultaneously and the Address 0x2F~31 correspond to the channel volume control register from 1 to 3 respectively.

The possible maximum of signal boost is +48.4375dB using master volume fine control because the master volume varies the gain of input signal independent from a channel volume, and a clipping might occur preventing overflow error if the input signal magnitude is large enough when the combined volume setting is higher than 0dB at the same time.

#### 9.1. Master Volume Control

By setting volume control registers, master volume is controlled between infinity and +24dB with changing step size as follows. For details on the master volume setting, see the register value table shown in <u>Appendix 2</u>.

Table 5 Level dependent master volume steps

| Step   | Range          |

|--------|----------------|

| 0.5 dB | +24 ~ -100 dB  |

| 10dB   | -100 ~ -150 dB |

#### 9.2. Channel Volume Control

By setting volume control registers, channel volumes are independently controlled between infinity and +24dB with changing step size as described below, and in the <u>Appendix 2</u>, exact values for channel volume setting are described.

Table 6 Level dependent channel volume steps

| Step   | Range          |

|--------|----------------|

| 0.5 dB | +24 ~ -100 dB  |

| 10dB   | -100 ~ -150 dB |

#### 9.3. Master Volume Fine Control

Fine control for master volume is possible (+0.0625dB step upto maximum +0.4375dB boost). Refer the system register Address 0x2D in the Appendix 1.

#### 9.4. Master Volume Override

By setting the master volume override flag on each channel, the master volume is not applied to the configured channels. See the system register Address 0x0A in the Appendix 1.

#### 9.5. Mute

NTP3000 enters mute state by setting soft mute flag of register Address 0x20. Soft mute is implemented so that the volume gradually increases or decreases when mute is turned off or on respectively.

Also the soft mute speed and soft volume change speed rates are programmable. Designers can minimize the pop noise by controlling the soft mute speed and volume change intervals. Refer SMC, SVI flag of register Address 0x06.

#### 9.6. Auto-mute

The chip mutes audio signal if the input signal level is below auto mute threshold during auto mute inspection interval that are programmable by register setting. Also, the behavior when auto mute has been entered is changeable between 50:50 switching on or off.

Auto-mute is supported for internal channels 1~3 after 2x3 mixer block. Refer register Addresses 0x04 and 0x05.

#### 9.7. Dynamic Range Control

Dynamic range compression can be turned on or off with programmable compression threshold and attack/release rates. The threshold parameters of DRC can be controlled separately for channel 1/2 and channel 3. For detailed setting, please refer system register Addresses 0x0E~10.

### 10. Output Interface

#### 10.1. Output mode configuration

The output mode of NTP3000 is 2.0 stereo reproduction mode and 2.1 reproduction mode. For this configuration register 0x0B~0x0D should be set to appropriate values.

#### 10.2. AM Interference relief mode

The NTP3000 has AM interference reduction mode. In this mode SNR performance of NTP3000 can be degrade to 90 dB and the PWM switching frequency is spread to 384kHz ~ 768kHz.

#### 10.3. PWM Output Mapper

Any internal channel from one through three that procedures PWM output can be assigned to any PWM output hardware port(or pin) by mapping output port register. This feature is very helpful for the hardware designer because it can relieve difficulties in the power stage signal routing and channel assignment if the output channel order is fixed. See the system register address 0x0B~0x0D in the <u>Appendix 1</u>.

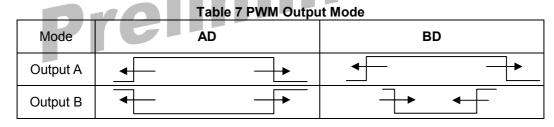

#### 10.4. Switching Output Mode

There are three selectable switching signal output modes called AD and BD mode in NTP3000. The difference among these output modes is the relative signal pattern relationship between PWM OUTxA and PWM OUTxB for the channel x.

The selection of output mode is dependent upon the topology of the output stage within NTP3000, and the design target and policy. AD mode can be applied to both half bridge and full bridge output stage. BD mode can be used for full bridge output stage only. MD flag of register address 0x03 set the output mode, then set the design stage.

AD asynchronous pair means the normal AD mode PWM output. In other words, A output and B output of each PWM output pair are mutually complement. In the case of AD asynchronous pair, A output and B output is perfectly identical, not in complement relation. That is useful in some special case including single-ended power stage design.

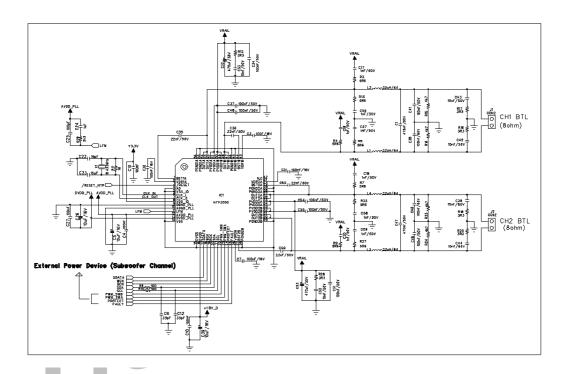

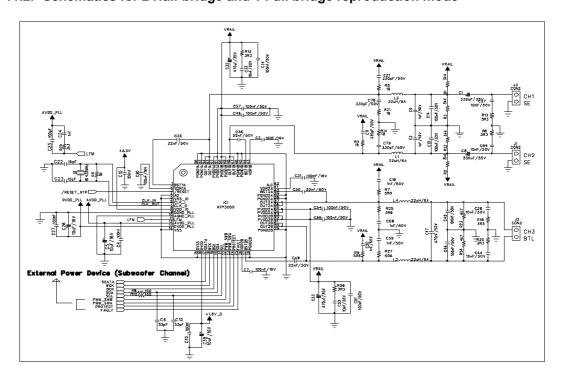

### 11. Typical Application Schematics

### 11.1. Schematics for 2 Full bridge reproduction mode

### 11.2. Schematics for 2 Half bridge and 1 Full bridge reproduction mode

### **A1. Configuration Register Summary**

### Table 8 Address 0x00: Input Format

| Bit  | 7 | 6 | 5 | 4 | 3   | 2 | 1  | 0  |

|------|---|---|---|---|-----|---|----|----|

| Name | X | X | X |   | FSM |   | IN | IS |

| Name  | Description                                 | Value | Meaning                           | Ref. |

|-------|---------------------------------------------|-------|-----------------------------------|------|

|       |                                             | 00    | I <sup>2</sup> S, slave mode      |      |

| INS   | Input format                                | 01    | I <sup>2</sup> S, master mode     |      |

| ING   | input ioimat                                | 10    | General serial audio, slave mode  |      |

|       |                                             | 11    | General serial audio, master mode |      |

|       |                                             | 000   | 48 kHz                            |      |

|       |                                             | 001   | 8 kHz                             |      |

|       | Compling                                    | 010   | 16 kHz                            |      |

| FSM   | Sampling<br>Frequency<br>in Master mode IIS | 011   | 32 kHz                            |      |

| FSIVI |                                             | 100   | 12 kHz                            |      |

|       |                                             | 101   | 24 kHz                            |      |

|       |                                             | 110   | 96 kHz                            |      |

|       |                                             | 111   | 192 kHz                           |      |

| Та | Table 9 Address 0x01: General Serial Audio Format |   |   |      |     |     |     |  |  |

|----|---------------------------------------------------|---|---|------|-----|-----|-----|--|--|

|    | Bit                                               | 7 | 6 | 5 4  | 3 2 | 1   | 0   |  |  |

|    | Name                                              | X | X | BCKS | BS  | MLF | LRJ |  |  |

|    |                                                   |   |   |      |     |     |     |  |  |

| Name  | Description           | Value | Meaning       | Ref. |

|-------|-----------------------|-------|---------------|------|

| LRJ   | Serial data justify   | 0     | Left justify  |      |

| LKJ   | Serial data justily   | 1     | Right justify |      |

| MLF   | Serial bit order      | 0     | MSB first     |      |

| IVILI | Serial bit order      | 1     | LSB first     |      |

|       | Serial bit size       | 00    | 24 bit        |      |

| BS    |                       | 01    | 20 bit        |      |

| ВЗ    |                       | 10    | 18 bit        |      |

|       |                       | 11    | 16 bit        |      |

|       |                       | 00    | 64 BCK/WCK    |      |

| BCKS  | Bit clock size select | 01    | 48 BCK/WCK    |      |

|       |                       | 10    | 32 BCK/WCK    |      |

#### Table 10 Address 0x02: Master clock frequency control

| Bit  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |

|------|---|---|---|---|---|---|---|----|

| Name | Х | Х | Х | Х | Х | Х | M | CF |

| Name | Description  | Value | Meaning                                 | Ref.  |

|------|--------------|-------|-----------------------------------------|-------|

|      |              | 00    | 12.288 MHz                              |       |

|      | Master Clock | 01    | 24.576 MHz                              |       |

| MCF  |              | 10    | 18.432 MHz                              |       |

|      | Frequency    | 11    | User defined frequency. Required to set | See   |

|      |              |       | address 0x7D and address 0x7E first.    | Table |

Table 11 User defined master clock frequency

| Master Clock Frequency | Address 0x7D | Address 0x7E |

|------------------------|--------------|--------------|

| 8.192MHz               | 0xC0         | 0x16         |

| 16.384MHz              | 0xE1         | 0x16         |

Caution 1) Register values different from those on the table are forbidden.

**Caution 2**) Writing values on Address 0x7D and 0x7E with MCF user defined frequency mode can make system unstable. Address 0x7D and 0x7E must be configured **before** MCF is set as user defined frequency.

Table 12 Address 0x03: Miscellaneous Control

| Bit  | 7 | 6 | 5   | 4   | 3 | 2   | 1  | 0 |

|------|---|---|-----|-----|---|-----|----|---|

| Name | Х | Х | BHL | AHL | Х | POL | MD |   |

| Name | Description        | Value | Meaning                               | Ref. |

|------|--------------------|-------|---------------------------------------|------|

|      |                    | 00    | AD mode with asynchronous signal pair |      |

| MD   | PWM output mode    | 01    | AD mode with synchronous signal pair  |      |

| IVID | Pyvivi output mode | 10    | BD mode                               |      |

|      |                    | 11    | AM Interference mode                  |      |

| POL  | Ch. 3 polarity     | 0     | Normal                                |      |

| FOL  | Control            | 1     | Inverse polarity                      |      |

| AHL  | A-out state        | 0     | Low                                   |      |

| ALL  | When switching off | 1     | High                                  |      |

| BHL  | B-out state        | 0     | Low                                   |      |

| ВПС  | when switching off | 1     | High                                  |      |

|      |                    |       |                                       |      |

Table 13 Address 0x04: Front Auto-mute control for channel 1, 2

| Bit  | 7    | 6 | 5    | 4 | 3  | 2 | 1 | 0 |

|------|------|---|------|---|----|---|---|---|

| Name | EAMC |   | ll l |   | AT |   |   |   |

| Name   | Description                      | Value | Meaning                                  | Ref. |

|--------|----------------------------------|-------|------------------------------------------|------|

| AT     | AT Auto-mute detection threshold |       | See Auto-mute detection threshold tables |      |

|        |                                  | 00    | 5 msec                                   |      |

| l II   | Auto-mute                        | 01    | 50 msec                                  |      |

| "      | response time                    | 10    | 500 sec                                  |      |

|        |                                  | 11    | 2 sec                                    |      |

|        |                                  | 00    | Auto mute disable(No-Effect)             |      |

| EAMC   | Effect of Auto-mute              | 01    | Channel SoftMute                         |      |

| EAIVIC | condition                        | 10    | 50:50 switching if auto-mute             |      |

|        |                                  | 11    | Stop switching if auto-mute              |      |

Table 14 Address 0x05: Front Auto-mute control for channel 3

| Bit  | 7           | 6 | 5     | 4 | 3    | 2 | 1 | 0 |

|------|-------------|---|-------|---|------|---|---|---|

| Name | EAMC        |   |       |   | AT   |   |   |   |

| Name | Description |   | Value |   | Ref. |   |   |   |

| AT     | Auto-mute detection threshold | <b>00</b> ~0F | See Auto-mute detection threshold tables |  |

|--------|-------------------------------|---------------|------------------------------------------|--|

|        |                               | 00            | 5 msec                                   |  |

| II     | Auto-mute                     | 01            | 50 msec                                  |  |

| "      | response time                 | 10            | 500 sec                                  |  |

|        |                               | 11            | 2 sec                                    |  |

|        |                               | 00            | Auto mute disable(No-Effect)             |  |

| EAMC   | Effect of Auto-mute           | 01            | Channel SoftMute                         |  |

| LAIVIC | condition                     | 10            | 50:50 switching if auto-mute             |  |

|        |                               | 11            | Stop switching if auto-mute              |  |

### Table 15 Address 0x06 : Various configuration

| Bit  | 7 | 6 | 5    | 4 | 3   | 2 | 1   | 0 |

|------|---|---|------|---|-----|---|-----|---|

| Name |   |   | GEQC |   | SVI |   | SMC |   |

| Name  | Description        | Value | Meaning                        | Ref. |

|-------|--------------------|-------|--------------------------------|------|

|       |                    | 00    | 42 / 46 msec (at 96 / 88.2kHz) |      |

| SMC   | Soft mute          | 01    | 85 / 92 msec                   |      |

| SIVIC | Speed control      | 10    | 21 / 23 msec                   |      |

|       |                    | 11    | 0 msec (Hard change)           |      |

|       |                    | 00    | Medium speed                   |      |

| SVI   | Soft volume change | _01   | High speed                     |      |

| 371   | Soft volume change | 10    | Low speed                      |      |

|       |                    | 11    | Soft volume change disable     |      |

|       | Graphic EQ         | 00    | Bypass                         |      |

| GEQC  | configuration      | 10    | Configuration 1                |      |

|       | Confingulation     | 11    | User defined                   |      |

### Table 16 Address 0x07: ALC configuration 1

| Bit  | 7  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------|----|---|---|---|---|---|---|---|

| Name | LB |   |   |   | Х | Х | Х | Х |

| Name | Description      | Value | Meaning               | Ref. |

|------|------------------|-------|-----------------------|------|

|      | Lower Bound      | 0000  | 0 dB                  |      |

| LB   | for Up condition | ~     |                       |      |

|      | relative scale   | 1101  | -12 dB with 1 dB step | ]    |

### Table 17 Address 0x08: ALC configuration 2

| Bit  | 7 | 6 | 5   | 4 | 3 | 2  | 1 | 0 |

|------|---|---|-----|---|---|----|---|---|

| Name | X | X | APR |   |   | CC |   |   |

| Name | Description | Value | Meaning              | Ref. |

|------|-------------|-------|----------------------|------|

|      |             | 00000 | 0 dB                 |      |

| CC   | C control   | ~     |                      |      |

|      |             | 11111 | 31 dB with 1 dB step |      |

| APR  | ALC enable  | 0     | ALC off              |      |

| AFK  | ALC enable  | 1     | ALC on               |      |

### Table 18 Address 0x09: ALC configuration 3

| Bit  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|------|---|---|---|---|---|---|---|---|--|

| Name | Χ | Х | С |   |   | A |   |   |  |

| Name | Description      | Value | Meaning                             | Ref. |

|------|------------------|-------|-------------------------------------|------|

| Α    | ALC attack rate  |       | Attack and release rate             |      |

| В    | ALC release rate |       | See attack and release rate tables. |      |

#### Table 19 Address 0x0A: Master volume override

| Bit  | 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    |

|------|---|---|---|---|---|------|------|------|

| Name | X | X | X | X | X | MVO3 | MVO2 | MVO1 |

| Name  | Description     | Value | Meaning                                    | Ref. |

|-------|-----------------|-------|--------------------------------------------|------|

| MVOn  | Master volume   | 0     | Master volume is effective for channel n   |      |

| WWOII | override on/off | 1     | Master volume is ineffective for channel n |      |

### Table 20 Address 0x0B: PWM output port Control for PWM port 1A & 1B

| Bit  | 7 | 6 | 5 | 4     | 3 | 2 | 1     | 0 |

|------|---|---|---|-------|---|---|-------|---|

| Name | Χ | X |   | OPM1B |   |   | OPM1A |   |

| Name   | Description     | Value | Meaning                           | Ref. |

|--------|-----------------|-------|-----------------------------------|------|

|        |                 | 000   | PWM1A is connected to PWM port 1A |      |

|        | Select source   | 001   | PWM1B is connected to PWM port 1A |      |

| OPM1A  | channel for     | 010   | PWM2A is connected to PWM port 1A |      |

| OFWIA  | PWM output port | 011   | PWM2B is connected to PWM port 1A |      |

|        | 1A              | 100   | PWM3A is connected to PWM port 1A |      |

|        |                 | 101   | PWM3B is connected to PWM port 1A |      |

|        |                 | 000   | PWM1A is connected to PWM port 1B |      |

|        | Select source   | 001   | PWM1B is connected to PWM port 1B |      |

| OPM1B  | channel for     | 010   | PWM2A is connected to PWM port 1B |      |

| OFWITE | PWM output port | 011   | PWM2B is connected to PWM port 1B |      |

|        | 1B              | 100   | PWM3A is connected to PWM port 1B |      |

|        |                 | 101   | PWM3B is connected to PWM port 1B |      |

### Table 21 Address 0x0C: PWM output port Control for PWM port 2A & 2B

| Bit  | 7 | 6 | 5 | 4     | 3 | 2 | 1     | 0 |

|------|---|---|---|-------|---|---|-------|---|

| Name | X | Х |   | OPM2B |   |   | OPM2A |   |

| Name        | Description     | Value | Meaning                           | Ref. |

|-------------|-----------------|-------|-----------------------------------|------|

|             |                 | 000   | PWM1A is connected to PWM port 2A |      |

|             | Select source   | 001   | PWM1B is connected to PWM port 2A |      |

| OPM2A chanr | channel for     | 010   | PWM2A is connected to PWM port 2A |      |

| OFIVIZA     | PWM output port | 011   | PWM2B is connected to PWM port 2A |      |

|             | 2A              | 100   | PWM3A is connected to PWM port 2A |      |

|             |                 | 101   | PWM3B is connected to PWM port 2A |      |

| OPM2B       | Select source   | 000   | PWM1A is connected to PWM port 2B |      |

| channel for     | 001 | PWM1B is connected to PWM port 2B |  |

|-----------------|-----|-----------------------------------|--|

| PWM output port | 010 | PWM2A is connected to PWM port 2B |  |

| 2B              | 011 | PWM2B is connected to PWM port 2B |  |

|                 | 100 | PWM3A is connected to PWM port 2B |  |

|                 | 101 | PWM3B is connected to PWM port 2B |  |

### Table 22 Address 0x0D: PWM output port Control for PWM port 3A & 3B

| Bit  | 7 | 6 | 5 | 4     | 3 | 2 | 1     | 0 |

|------|---|---|---|-------|---|---|-------|---|

| Name | X | X |   | OPM3B |   |   | OPM3A |   |

| Name    | Description     | Value | Meaning                           | Ref. |

|---------|-----------------|-------|-----------------------------------|------|

|         |                 | 000   | PWM1A is connected to PWM port 3A |      |

|         | Select source   | 001   | PWM1B is connected to PWM port 3A |      |

| ОРМЗА   | channel for     | 010   | PWM2A is connected to PWM port 3A |      |

| OFINISA | PWM output port | 011   | PWM2B is connected to PWM port 3A |      |

|         | 3A              | 100   | PWM3A is connected to PWM port 3A |      |

|         |                 | 101   | PWM3B is connected to PWM port 3A |      |

|         |                 | 000   | PWM1A is connected to PWM port 3B |      |

|         | Select source   | 001   | PWM1B is connected to PWM port 3B |      |

| ОРМЗВ   | channel for     | 010   | PWM2A is connected to PWM port 3B |      |

| OFINISE | PWM output port | 011   | PWM2B is connected to PWM port 3B |      |

|         | 3B              | _100  | PWM3A is connected to PWM port 3B |      |

|         |                 | 101   | PWM3B is connected to PWM port 3B |      |

#### Table 23 Address 0x0E: DRC control for channel 1&2

| Bit  | 7 | 6 | 5 | 4   | 3 | 2 | 1 | 0   |

|------|---|---|---|-----|---|---|---|-----|

| Name |   |   |   | CTS |   |   |   | CPR |

| Name           | Description       | Value | Value Meaning                       |  |  |

|----------------|-------------------|-------|-------------------------------------|--|--|

| CPR            | DRC enable 0      |       | Dynamic Range Compression off       |  |  |

| CPR DRC enable |                   | 1     | Dynamic Range Compression on        |  |  |

| CTS            | CTS DRC threshold |       | Unsigned 6-bit DRC threshold        |  |  |

| 013            |                   |       | Refer to DRC threshold value table. |  |  |

#### Table 24 Address 0x0F: DRC control for channel 3

| Bit  | 7 | 6 | 5 | 4   | 3 | 2 | 1 | 0   |

|------|---|---|---|-----|---|---|---|-----|

| Name |   |   |   | CTS |   |   |   | CPR |

| Name | Description   | Value   | Value Meaning                       |  |  |  |

|------|---------------|---------|-------------------------------------|--|--|--|

| CPR  | DRC enable    | 0       | Dynamic Range Compression off       |  |  |  |

| CFK  | DIC enable    | 1       | Dynamic Range Compression on        |  |  |  |

| CTS  | DDC throshold | 57~12dB | Unsigned 6-bit DRC threshold        |  |  |  |

| CIS  | DRC threshold | 57~12UB | Refer to DRC threshold value table. |  |  |  |

### Table 25 Address 0x10: DRC configuration control

| Bit  | 7 | 6 | 5 | 4   | 3 | 2 | 1   | 0 |

|------|---|---|---|-----|---|---|-----|---|

| Name | X | X |   | C1C |   |   | A1C |   |

| Name | Description      | Value | Meaning                             | Ref. |

|------|------------------|-------|-------------------------------------|------|

| A1C  | DRC attack rate  |       | Attack and release rate             |      |

| C1C  | DRC release rate |       | See attack and release rate tables. |      |

#### Table 26 Address 0x11: Modulation Index & NS-Type Control

| Bit  | 7 | 6  | 5 | 4  | 3   | 2 | 1    | 0 |

|------|---|----|---|----|-----|---|------|---|

| Name | X | M0 |   | NT | MD3 |   | MD12 |   |

| Name   | Description                            | Value | Meaning                                    | Ref. |

|--------|----------------------------------------|-------|--------------------------------------------|------|

|        | Modulation index                       | 11    | Minimum pulse width = 2                    |      |

| MD12   | control by Minimum                     | 10    | Minimum pulse width = 4                    |      |

| IVIDIZ | pulse width                            | 01    | Minimum pulse width = 6                    |      |

|        | for Ch 1&2                             | 00    | Minimum pulse width = 8                    |      |

|        | Modulation index                       | 11    | Minimum pulse width = 2                    |      |

| MD3    | control by Minimum pulse width for Ch3 | 10    | Minimum pulse width = 4                    |      |

| IVIDS  |                                        | 01    | Minimum pulse width = 6                    |      |

|        | puise width for Chis                   | 00    | Minimum pulse width = 8                    |      |

| NT     | Noise shaping Type                     | 0     | Type 1 4                                   |      |

| INI    | for Ch 1&2 &3                          | 1     | Type 2 5                                   |      |

|        |                                        | 00    | No left shift on dither value = Dither off |      |

| MO     | Dither Position                        | 01    | 1bit left shift on dither value            |      |

| IVIO   | Selector                               | 10    | 2bit left shift on dither value            |      |

|        |                                        | 11    | 3bit left shift on dither value            |      |

#### Table 27 Address 0x12: Prescaler Control for Ch 1&2

| Bit  | 7 | 6  | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|------|---|----|---|---|---|---|---|---|--|--|

| Name |   | PS |   |   |   |   |   |   |  |  |

| Name | Description     | Value    | Meaning     | Ref. |

|------|-----------------|----------|-------------|------|

| PS   | Prescaler value | unsigned | 208 default |      |

### Table 28 Address 0x13: Prescaler Control for Ch 3

|   | Bit  | 7  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---|------|----|---|---|---|---|---|---|---|--|

| ĺ | Name | PS |   |   |   |   |   |   |   |  |

| Name | Description     | Value    | Meaning     | Ref. |

|------|-----------------|----------|-------------|------|

| PS   | Prescaler value | unsigned | 208 default |      |

### Table 29 Address 0x17: Aout Rising Edge Delay

| Bit  | 7 | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|------|---|------|---|---|---|---|---|---|--|--|

| Name |   | ARED |   |   |   |   |   |   |  |  |

| Name | Description            | Value    | Meaning   | Ref. |

|------|------------------------|----------|-----------|------|

| ARED | Aout Rising Edge Delay | unsigned | 0 default |      |

#### Table 30 Address 0x18: Aout Falling Edge Delay

| Bit  | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|------|------|---|---|---|---|---|---|---|--|

| Name | AFED |   |   |   |   |   |   |   |  |

|   | Name | Description             | Value    | Meaning   | Ref. |

|---|------|-------------------------|----------|-----------|------|

| ĺ | AFED | Aout Falling Edge Delay | unsigned | 0 default |      |

### Table 31 Address 0x19: Bout Rising Edge Delay

|   | Bit  | 7 | 6 | 5 | 4    | 3 | 2 | 1 | 0 |

|---|------|---|---|---|------|---|---|---|---|

| Ī | Name |   |   |   | BREI | D |   |   |   |

| Name | Description            | Value    | Meaning   | Ref. |

|------|------------------------|----------|-----------|------|

| BRED | Bout Rising Edge Delay | unsigned | 0 default |      |

#### Table 32 Address 0x1A: Bout Falling Edge Delay

| Ī | Bit  | 7 | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---|------|---|------|---|---|---|---|---|---|--|

|   | Name |   | BFED |   |   |   |   |   |   |  |

|   | Name | Description Valu        |          | Meaning   | Ref. |

|---|------|-------------------------|----------|-----------|------|

| ĺ | BFED | Bout falling Edge Delay | unsigned | 0 default |      |

#### Table 33 Address 0x1B: PWM off & Auto PROTECT Control

| Bit  | 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0   |

|------|---|---|---|---|---|---|-----|-----|

| Name | 1 | 0 | 1 | 0 | 1 | 0 | APM | POF |

| Name | Description  | Value | Meaning                                                                                                                                                                 | Ref. |

|------|--------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|      | PWM off flag | 0     | Even if Auto PROTECT condition is met, the PWM output of all channel is not affected.                                                                                   |      |

| POF  |              | 1     | When Auto PROTECT condition is met, the PWM output of all channel goes to the defined state which is set by the PWM off state control register (Address 0x03 AHL, BHL). |      |

| APM  | PROTECT flag | 0     | Even if Auto PROTECT condition is met, the PROTECT output of all channel is not affected.                                                                               |      |

|      |              | 1     | When Auto PROTECT condition is met, the PROTECT output goes to Low state.                                                                                               |      |

### Table 34 Address 0x1C: Auto PROTECT condition Control Masking

| Bit  | 7     | 6       | 5       | 4     | 3     | 2     | 1     | 0     |

|------|-------|---------|---------|-------|-------|-------|-------|-------|

| Name | VMSK3 | VMSK2   | VMSK1   | VMSK0 | PMSK3 | PMSK2 | PMSK1 | PMSK0 |

|      |       |         |         |       |       |       |       |       |

| Name | Desci | rintion | مرياد/\ |       | Меа   | nina  |       | ₽of   |

| Name | Description                       | Value | Meaning | Ref. |

|------|-----------------------------------|-------|---------|------|

| PMSK | Masking bit of<br>PWM off control |       |         |      |

| VMSK | Masking bit of PROTECT signal     |       |         |      |

#### Table 35 Address 0x1D: PROTECT Control

| Bit  | 7  | 6 | 5 | 4     | 3 | 2   | 1 | 0 |

|------|----|---|---|-------|---|-----|---|---|

| Name | IR |   |   | AVRCT |   | PHT |   |   |

| Name  | Description                       | Value | Meaning                    | Ref. |

|-------|-----------------------------------|-------|----------------------------|------|

|       |                                   | 000   | 0.5 msec Hold Time         |      |

|       |                                   | 001   | 1 msec Hold Time           |      |

| PHT   | PROTECT Low                       | 010   | 2 msec Hold Time           |      |

| FIII  | Hold Time                         | 011   | 4 msec Hold Time (Default) |      |

|       |                                   | 100   | 8 msec Hold Time           |      |

|       |                                   | 101   | 16msec Hold Time           |      |

|       | Auto PROTECT<br>Restore Counter   | 000   | 2                          |      |

|       |                                   | 001   | 5 (Default)                |      |

|       |                                   | 010   | 10                         |      |

| AVRCT |                                   | 011   | 15                         |      |

| AVICT | Threshold                         | 100   | 20                         |      |

|       | Tillesiloid                       | 101   | 25                         |      |

|       |                                   | 110   | 30                         |      |

|       |                                   | 111   | Infinity                   |      |

|       | Auto PROTECT                      | 00    | 2 (Default)                |      |

| IRC   | Restore Interval<br>Ratio Control | 01    | 4                          |      |

### Table 36 Address 0x1E: PROTECT Control

| Bit  | 7 | 6 | 5 | 4 | 3   | 2     | 1    | 0 |

|------|---|---|---|---|-----|-------|------|---|

| Name | 0 | 0 | 0 | 0 | SRD | FPMLD | PWMM |   |

| Name        | Description      | Value     | Meaning                                | Ref. |

|-------------|------------------|-----------|----------------------------------------|------|

| PWMM        | PROTECT          | 10        | PROTECT output is low. (reset default) |      |

| F VV IVIIVI | register         | otherwise | PROTECT output is high.                |      |

|             | Permanent        | 0         | No effect                              |      |

| FPMLD       | PROTECT          | 1         | Reset the auto PROTECT restore counter |      |

|             | Low disable flag |           | to 0                                   |      |

| SRD         | FAULT disable    | 0         | FAULT is effect for PROTECT            |      |

| SKD         |                  | 1         | FAULT is ineffective for PROTECT       |      |

### Table 37 Address 0x1F: Switching Off Control

| Bit  | 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    |

|------|---|---|---|---|---|------|------|------|

| Name | Х | X | X | X | X | POF3 | POF2 | POF1 |

| Name  | Description      | Value | Meaning                     | Ref. |

|-------|------------------|-------|-----------------------------|------|

| POFn  | Switching output | 0     | Channel n PWM switching on  |      |

| POFII | On/off control   | 1     | Channel n PWM switching off |      |

#### Table 38 Address 0x20: Softmute Control

| Bit  | 7 | 6 | 5 | 4 | 3 | 2   | 1   | 0   |

|------|---|---|---|---|---|-----|-----|-----|

| Name | Х | X | X | X | X | SM3 | SM2 | SM1 |

| Name | Description | Value | Meaning                | Ref. |

|------|-------------|-------|------------------------|------|

| SMn  | Softmute    | 0     | increase for channel n |      |

|      |             | 1     | decrease for channel n |      |

#### Table 39 Address 0x2C: FBQ\_FLAG for Ch 1&2&3

| Bit  | 7 | 6 | 5     | 4     | 3     | 2     | 1     | 0     |

|------|---|---|-------|-------|-------|-------|-------|-------|

| Name | Х | Х | FBQ32 | FBQ31 | FBQ22 | FBQ21 | FBQ12 | FBQ11 |

|      |   |   |       |       |       |       |       |       |

| Name   | Description              | Value | Meaning | Ref. |

|--------|--------------------------|-------|---------|------|

| FBQ11  | 1 <sup>st</sup> FBQ flag | 0     | Bypass  |      |

| IDQII  | for CH1                  | 1     | Enable  |      |

| FBQ12  | 2nd FBQ flag             | 0     | Bypass  |      |

| 1 DQ12 | for CH1                  | 1     | Enable  |      |

| FBQ21  | 1 <sup>st</sup> FBQ flag | 0     | Bypass  |      |

| FBQZI  | for CH2                  | 1     | Enable  |      |

| FBQ22  | 2nd FBQ flag             | 0     | Bypass  |      |

| FBQZZ  | for CH2                  | 1     | Enable  |      |

| FBQ31  | 1 <sup>st</sup> FBQ flag | 0     | Bypass  |      |

| FBQ31  | for CH3                  | 1     | Enable  |      |

| FBQ32  | 2nd FBQ flag             | 0     | Bypass  |      |

| FBQ32  | for CH3                  | 1     | Enable  |      |

#### Table 40 Address 0x2D: Master Fine volume

| Bit  | 7 | 6 | 5 | 4 | 3 | 2    | 1 | 0 |

|------|---|---|---|---|---|------|---|---|

| Name | X | X | X | X | X | MVFC |   |   |

| Name | Description   | Value | Meaning                    | Ref. |

|------|---------------|-------|----------------------------|------|

|      | Master volume | 000   | 0 dB                       |      |

| MVFC | fine control  | ~     | ~                          |      |

|      |               | 111   | 0.5 dB with 0.0625 dB step |      |

### Table 41 Address 0x2E~0x31: Master volume & Channel 1~3 volume respectively

| Bit  | 7 | 6 | 5 | 4 | 3  | 2 | 1 | 0 |

|------|---|---|---|---|----|---|---|---|

| Name |   |   |   | V | DL |   |   |   |

| Name | Description    | Value | Value Meaning                                                                                          |  |  |  |

|------|----------------|-------|--------------------------------------------------------------------------------------------------------|--|--|--|

| VOL  | Volume control |       | See volume control register tables. Reset default is 0 ( = $-\infty$ dB)for Master and 207 for Channel |  |  |  |

#### Table 42 Address 0x32~0x36: GEQ Gain for Band 2~6

| Bi  | t  | 7 | 6 | 5 | 4 | 3 | 2  | 1 | 0 |

|-----|----|---|---|---|---|---|----|---|---|

| Nar | ne | X | X | X |   |   | BG |   |   |

| Name | Description | Value | Meaning                   | Ref. |

|------|-------------|-------|---------------------------|------|

| BG   | Band Gain   |       | See register value table. |      |

| Name | Address | Band   | Frequency | Ref |

|------|---------|--------|-----------|-----|

|      | 0x32    | Band 2 | 220Hz     |     |

|      | 0x33    | Band 3 | 470Hz     |     |

| Band | 0x36    | Band 4 | 1kHz      |     |

|      | 0x34    | Band 5 | 2.2kHz    |     |

|      | 0x35    | Band 6 | 4.7kHz    |     |

### Table 43 Address 0x69 & 0x6A: GEQ Gain for Band 1 & Band 7

| Bit  | 7 | 6 | 5 | 4 | 3 | 2  | 1 | 0 |

|------|---|---|---|---|---|----|---|---|

| Name | Х | Х | Χ |   |   | BG |   |   |

| Name | Description | Value | Meaning                   | Ref. |

|------|-------------|-------|---------------------------|------|

| BG   | Band Gain   |       | See register value table. |      |

| Name   | Address | Band   | Frequency | Ref |

|--------|---------|--------|-----------|-----|

| Band - | 0x69    | Band 1 | 80Hz      |     |

| Dallu  | 0x6A    | Band 7 | 12kHz     |     |

#### Table 44 Address 0x37~0x3C: Mixer Gain

|   | Bit  | 7 | 6 | 5 | 4 | 3  | 2 | 1 | 0 |

|---|------|---|---|---|---|----|---|---|---|

| ſ | Name | X |   |   |   | MG |   |   |   |

| Name | Description | Value | Meaning                      | Ref. |

|------|-------------|-------|------------------------------|------|

| MG   | Mixer gain  |       | Mixer gain download register |      |

### Table 45 Address 0x3D~0x3E: Back Biquad Filter Configuration for Ch 1~2 respectively

| Bit  | 7  | 6   | 5  | 4 | 3  | 2   | 1     | 0     |

|------|----|-----|----|---|----|-----|-------|-------|

| Name | BQ | F5n | BQ |   | BQ | F3n | BQF2n | BQF1n |

| Name    | Description                                | Value                                                                 | Meaning                            | Ref. |

|---------|--------------------------------------------|-----------------------------------------------------------------------|------------------------------------|------|

| BQF1n   | On/Off biquad 1                            | 0                                                                     | Bypass biquad 1 of channel n       |      |

| DQI III | of CH n (= CH 1,2,3)                       | 1                                                                     | Enable biquad 1 of channel n       |      |

| BQF2n   | On/Off biquad 2                            |                                                                       | Bypass biquad 2 of channel n       |      |

| DQI ZII | of CH n (= CH 1,2,3)                       | 1                                                                     | Enable biquad 2 of channel n       |      |

|         | BQF3n On/Off biquad 3 of CH n (= CH 1,2,3) | 00                                                                    | Bypass biquad 3 of channel n       |      |

| BQF3n   |                                            | 01                                                                    | Enable biquad 3 of channel n       |      |

|         |                                            | 10                                                                    | Enable biquad 3 as Loudness Filter |      |

|         | On/Off bigued 4                            | 00                                                                    | Bypass biquad 4 of channel n       |      |

| BQF4n   | On/Off biquad 4<br>of CH n (= CH 1,2,3)    | 01                                                                    | Enable biquad 4 of channel n       |      |

|         | 01 01111 (= 011 1,2,3)                     | 10                                                                    | Enable biquad 4 as Loudness Filter |      |

|         | On/Off bigued 5                            | 00                                                                    | Bypass biquad 5 of channel n       |      |

| BQF5n   | of CH n (= CH 1,2,3)                       | On/Off biquad 5 of CH n (= CH 1 2 3)  O1 Enable biquad 5 of channel n |                                    |      |

|         | 01 01111 (= 011 1,2,0)                     | 10                                                                    | Enable biquad 5 as Loudness Filter |      |

### Table 46 Address 0x3F: Biquad Filter Coefficient Page

| able 46 Add | ie 46 Address UX3F: Biquad Filter Coeπicient Page |          |          |    |      |      |     |     |  |  |

|-------------|---------------------------------------------------|----------|----------|----|------|------|-----|-----|--|--|

|             |                                                   |          |          |    |      |      |     |     |  |  |

| Bit         | 7                                                 | 6        | 5        | 4  | 3    | 2    | 1   | 0   |  |  |

| Name        | CH3L                                              | Various2 | Various1 | 3D | GEQ2 | GEQ1 | CH2 | CH1 |  |  |

| Name                  | Description          | Value | Meaning                             | Ref. |

|-----------------------|----------------------|-------|-------------------------------------|------|

| CHn                   | Write enable         | 0     | Disable channel n coefficient write |      |

| Cilli                 | Wille chable         | 1     | Enable Channel n coefficient write  |      |

| GEQ1 Write enable for |                      | 0     | Disable coefficient write           |      |

| GEQT                  | GEQ UD mode Ch1      | 1     | Enable coefficient write            |      |

| GEQ2 Write enable for |                      | 0     | Disable coefficient write           |      |

| GEQZ                  | GEQ UD mode CH2      | 1     | Enable coefficient write            |      |

| 3D                    | Write enable for     |       | Disable coefficient write           |      |

| 30                    | 3D filter            | 1     | Enable coefficient write            |      |

| Various1              | Write enable for     | 0     | Disable coefficient write           |      |

| various i             | FBQ, ALC             | 1     | Enable coefficient write            |      |

| Various2              | Write enable for FBQ | 0     | Disable coefficient write           |      |

| variousz              | and BBQ of CH3       | 1     | Enable coefficient write            |      |

| CH3L                  | Write enable for     | 0     | Disable coefficient write           |      |

| CITSL                 | CH3 Loudness gain    | 1     | Enable coefficient write            |      |

Table 47 Address 0x40~0x58: Biquad Filter Coefficient

32-bit floating point

Table 48 Address 0x59~0x5B: Loudness Gain for BQ 3,4,5 of Ch 1& 2 &3

32-bit floating point

Table 49 Address 0x5C~0x5F: Mixer Gain value for 3D

32bit floating point

### Table 50 Address 0x60: 3D delay amount

| Bit  | 7 | 6 | 5 | 4 | 3    | 2    | 1 | 0 |

|------|---|---|---|---|------|------|---|---|

| Name | X | X |   |   | 3D D | elay |   |   |

| Name     | Description | Value    | Meaning | Ref. |

|----------|-------------|----------|---------|------|

| 3D Delay | 3D Delay    | unsigned | 1 ~ 40  |      |

### Table 51 Address 0x61 3D effect control configuration

| Bit  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|------|---|---|---|---|---|---|---|-----|

| Name | X | X | X | X | X | X | X | 3BF |

| Name | Description    | Value | Meaning | Ref. |

|------|----------------|-------|---------|------|

| 3BF  | 2D Dynasa Flag | 0     | Bypass  |      |

| SDF  | 3D Bypass Flag | 1     | 3D on   |      |

### Table 52 Address 0x62 PWM Mode Control Register

| Bit  | 7 | 6 | 5 | 4 | 3 | 2 | 1  | 0 |  |  |

|------|---|---|---|---|---|---|----|---|--|--|

| Name | X | Х | Х | X | Х | X | PM |   |  |  |

|      |   |   |   |   |   |   |    |   |  |  |

| Name | Description   | Value | Meaning                                    | Ref. |  |  |  |  |

|------|---------------|-------|--------------------------------------------|------|--|--|--|--|

|      |               | 00    | <b>00</b> Forbidden. Must be set as below. |      |  |  |  |  |

| PM   | PWM Mode      | 01    | 1 chip, 2.1 channel mode                   |      |  |  |  |  |

| FIVI | PVVIVI IVIOGE | 10    | 1 chip 2.0 channel mode or 2.1 channel     |      |  |  |  |  |

|      |               | 10    | with external power stage                  |      |  |  |  |  |

### Table 52 Address 0x63 Stand-by in 2 Channel mode

| Bit  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |

|------|---|---|---|---|---|---|---|----|

| Name | X | X | X | X | X | X | X | SB |

| Name | Description                   | Value | Meaning            | Ref. |

|------|-------------------------------|-------|--------------------|------|

|      |                               | 0     | Stand-by operation |      |

| SB   | stand-by in<br>2 Channel mode | 1     | Normal operation   |      |

#### Table 53 Address 0x75: System Status (Read-only)

| Bit  | 7 | 6  | 5  | 4 | 3   | 2    | 1    | 0   |

|------|---|----|----|---|-----|------|------|-----|

| Name |   | F: | SI |   | MPW | LSRC | ULCK | PPM |

| Name   | Description                   | Value | Meaning                                          | Ref. |

|--------|-------------------------------|-------|--------------------------------------------------|------|

| ULCK   | sampled PLL                   | 0     | PLL is locked state.                             |      |

| OLCK   | unlock error                  | 1     | PLL is unlocked state.                           |      |

| MPW    | MCK/WCK 0 Ratio is incorrect. |       | Ratio is incorrect.                              |      |

| IVIEVV | ratio error                   | 1     | Ratio is correct.                                |      |

|        | Permanent                     | 0     |                                                  |      |