TPS659119-Q1

SWCS106F-MARCH 2013-REVISED JULY 2016

# TPS659119-Q1 Automotive Integrated Power-Management Unit

#### **Features**

- **Qualified for Automotive Applications**

- AEC-Q100 Qualified with the Following Results:

- Device Temperature Grade 3: -40°C to 85°C Ambient Operating Temperature Range

- Device HBM ESD Classification Level 2

- Device CDM ESD Classification Level C4B

- Embedded Power Controller (EPC) With **EEPROM Programmability**

- Two Efficient Step-Down DC-DC Converters With Dynamic Voltage Scaling for Processor Cores (VDD1, VDD2)

- One Efficient Step-Down DC-DC Converter for I/O Power (VIO)

- An Interface to Control an External DCDC Converter (EXTCTRL)

- Eight LDO Voltage Regulators and One RTC LDO (Supply for Internal RTC)

- One High-Speed I<sup>2</sup>C Interface for General-Purpose Control Commands (CTL-I<sup>2</sup>C)

- Two Independent Enable Signals for Controlling Power Resources (EN1, EN2) Which can be Used as a High-Speed I2C Interface Dedicated for VDD1 and VDD2 Voltage Scaling.

- Thermal Shutdown Protection and Hot-Die Detection

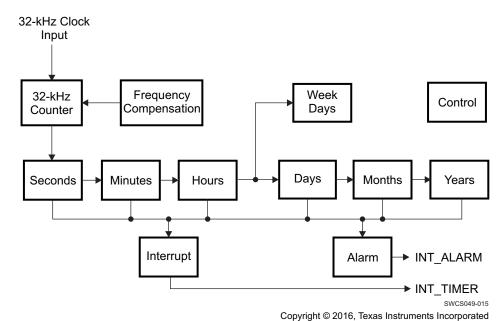

- A Real-Time Clock (RTC) Resource with:

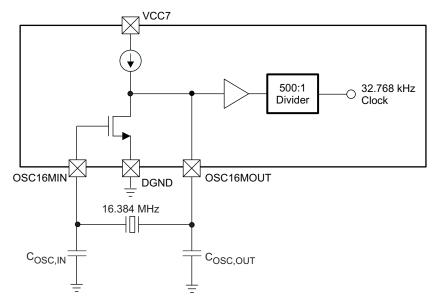

- Fast Start-Up 16.384-MHz Crystal Oscillator

- Configurable Clock Source from Crystal Oscillator, External 32-kHz Clock or Internal 32-kHz RC Oscillator

- Date, Time, and Calendar

- Alarm Capability

- Nine Configurable GPIOs with Multiplexed Feature Support:

- Four can be Used as Enable for External Resources, Included into Power-Up Sequence and Controlled by State-Machine

- As GPI, GPIOs Support Logic-level Detection and Can Generate Maskable Interrupt for Wake-Up

- Two of the GPIOs Have 10-mA Current Sink Capability for Driving LEDs

- DCDCs Switching Synchronization Through an External 3-MHz Clock

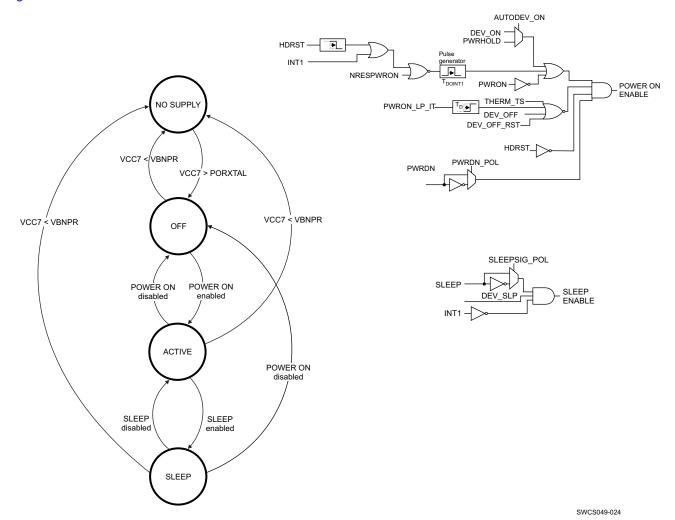

- Two Reset Inputs for Cold Reset (HDRST) and a Power-Initialization Reset (PWRDN) for Thermal

Reset Input

- 32-kHz Clock Output (CLK32KOUT) and System Reset (NRESPWRON) Included in Power Sequence

- Watchdog

- Two ON and OFF LED-Pulse Generators and One **PWM Generator**

## 2 Applications

- Automotive

- Infotainment

- **ADAs**

- Instrument Cluster

## 3 Description

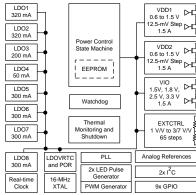

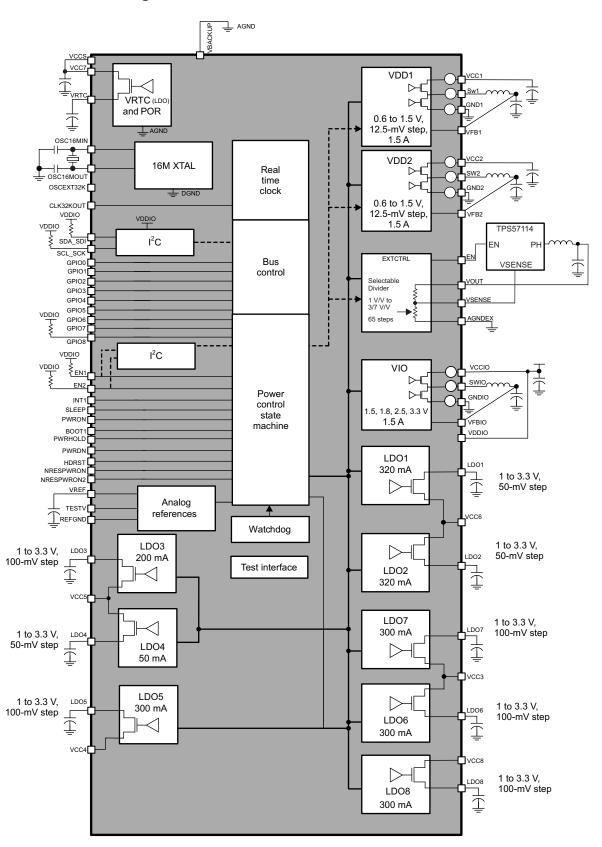

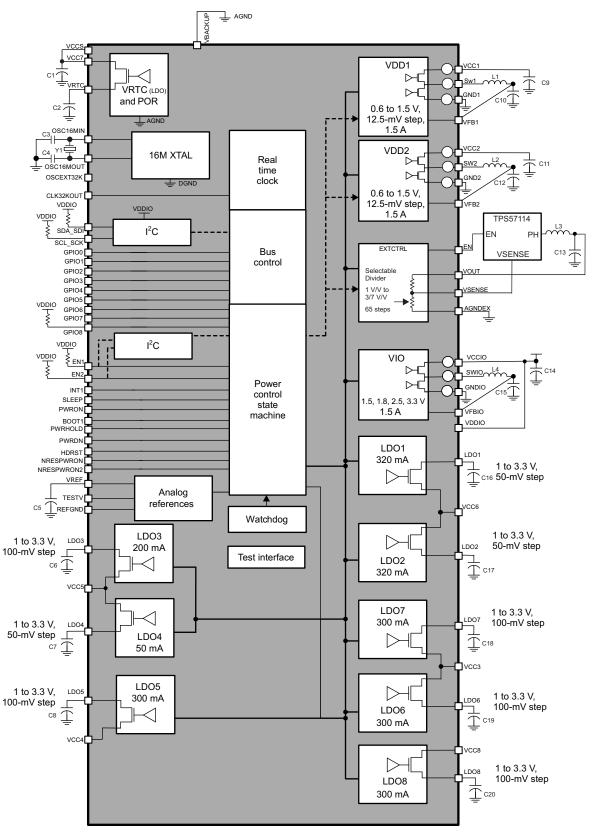

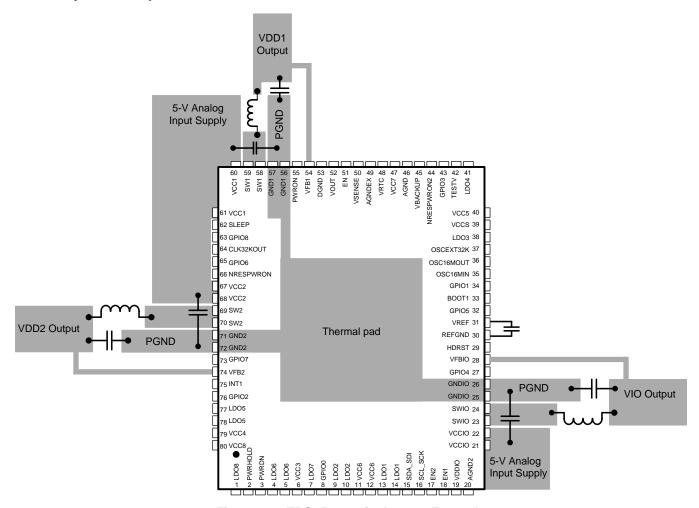

The TPS659119-Q1 device is an integrated powermanagement IC dedicated to systems using an applications processor requiring multiple power rails. The device provides three step-down converters, one control for an external converter, eight LDOs, and is designed to be flexible for supporting different processors and applications.

Two of the step-down converters provide power for dual-processor cores and support for dynamic voltage scaling by a dedicated I<sup>2</sup>C interface for optimum power savings. The third converter provides power for inputs and outputs (I/Os) and memory in the system. The control for an external converter can sequence and scale the voltage of an external converter for a high-current rail in the system.

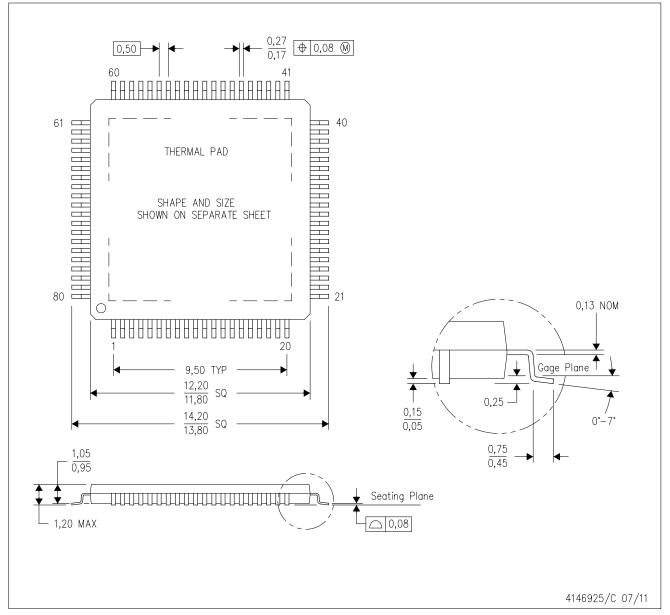

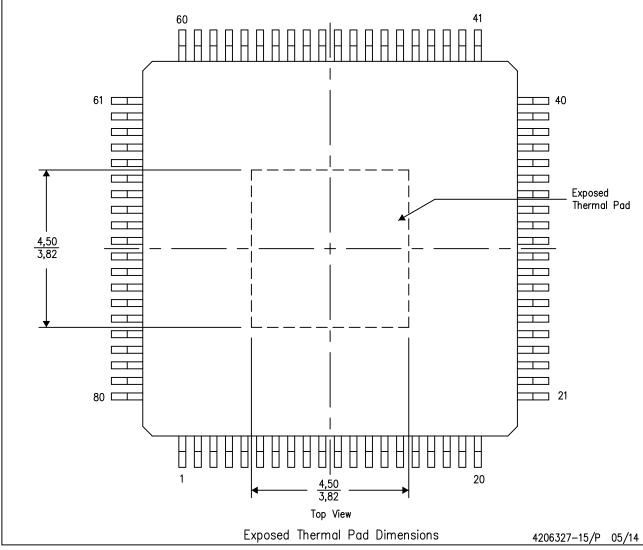

#### Device Information<sup>(1)</sup>

| PART NUMBER  | PACKAGE    | BODY SIZE (NOM)     |

|--------------|------------|---------------------|

| TPS659119-Q1 | HTQFP (80) | 12.00 mm × 12.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

#### Simplified Schematic

# **Table of Contents**

| 1                 | Features 1                                                           |       | Example                                                               | 28  |

|-------------------|----------------------------------------------------------------------|-------|-----------------------------------------------------------------------|-----|

| 2                 | Applications 1                                                       |       | 7.25 Power Control Timing Requirements                                | 28  |

| 3<br>4            | Description                                                          |       | 7.26 Device SLEEP State Control Timing Requirements                   | 29  |

| <del>+</del><br>5 | Description (continued)4                                             |       | 7.27 Supplies State Control Through EN1 and EN Timing Characteristics |     |

| 6                 | Pin Configuration and Functions 4                                    |       | 7.28 VDD1 Supply Voltage Control Through EN1                          |     |

| 7                 | Specifications7                                                      |       | Requirements                                                          |     |

|                   | 7.1 Absolute Maximum Ratings 7                                       | _     | 7.29 Typical Characteristics                                          |     |

|                   | 7.2 ESD Ratings7                                                     | 8     | Detailed Description                                                  |     |

|                   | 7.3 Recommended Operating Conditions 8                               |       | 8.1 Overview                                                          |     |

|                   | 7.4 Thermal Characteristics 8                                        |       | 8.2 Functional Block Diagram                                          | 37  |

|                   | 7.5 External Component Recommendation 8                              |       | 8.3 Feature Description                                               | 38  |

|                   | 7.6 I/O Pullup and Pulldown Characteristics 10                       |       | 8.4 Device Functional Modes                                           | 42  |

|                   | 7.7 Digital I/O Voltage Electrical Characteristics 10                |       | 8.5 Programming                                                       | 54  |

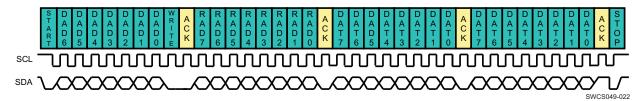

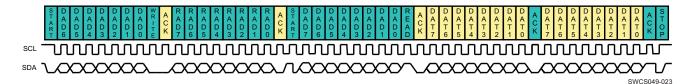

|                   | 7.8 I <sup>2</sup> C Interface and Control Signals                   |       | 8.6 Register Maps                                                     | 58  |

|                   | 7.9 Switching Characteristics—I <sup>2</sup> C Interface and Control | 9     | Application and Implementation                                        | 117 |

|                   | Signals 12                                                           |       | 9.1 Application Information                                           |     |

|                   | 7.10 Power Consumption                                               |       | 9.2 Typical Application                                               |     |

|                   | 7.11 Power References and Thresholds                                 | 10    | Power Supply Recommendations                                          |     |

|                   | 7.12 Thermal Monitoring and Shutdown 13                              | 11    | Layout                                                                |     |

|                   | 7.13 32-kHz RTC Clock 14                                             | • • • | 11.1 Layout Guidelines                                                |     |

|                   | 7.14 VRTC LDO 15                                                     |       | 11.2 Layout Example                                                   |     |

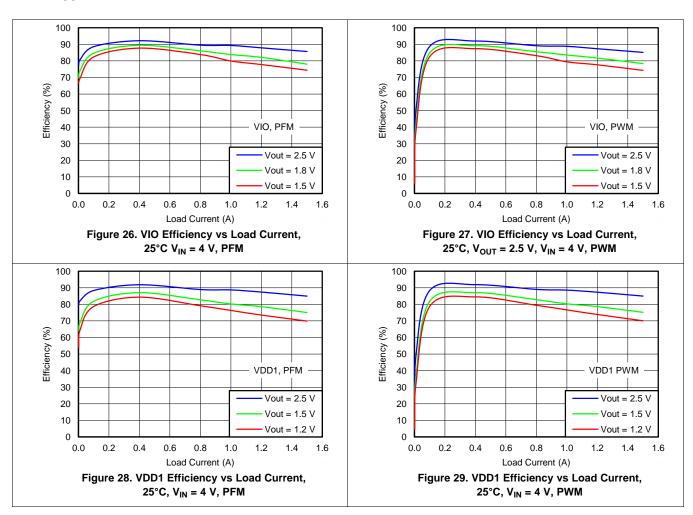

|                   | 7.15 VIO SMPS                                                        | 12    |                                                                       |     |

|                   | 7.16 VDD1 SMPS                                                       | 12    | Device and Documentation Support                                      |     |

|                   | 7.17 VDD2 SMPS                                                       |       | 12.1 Device Support                                                   | 123 |

|                   | 7.18 EXTCTRL                                                         |       | 12.2 Receiving Notification of Documentation Updates                  | 124 |

|                   | 7.19 LDO1 AND LDO2                                                   |       | 12.3 Community Resources                                              |     |

|                   | 7.20 LDO3 and LDO4                                                   |       | 12.4 Trademarks                                                       |     |

|                   | 7.21 LDO524                                                          |       |                                                                       |     |

|                   | 7.22 LDO6 and LDO7                                                   |       | 12.5 Electrostatic Discharge Caution                                  |     |

|                   | 7.23 LD08                                                            | 4.0   | 12.6 Glossary                                                         | 124 |

|                   | 7.24 Timing Requirements for Boot Sequence                           | 13    | Mechanical, Packaging, and Orderable Information                      | 124 |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C        | changes from Revision E (September 2014) to Revision F                                                                                                          | Page |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •        | Deleted Top Specification from title of document                                                                                                                | 1    |

| •        | Changed the Handling Ratings table to ESD Ratings and moved the storage temperature to the Absolute Maximu Ratings table                                        |      |

| <u>•</u> | Added the Receiving Notification of Documentation Updates and Community Resources sections                                                                      | 124  |

| C        | changes from Revision D (July 2014) to Revision E                                                                                                               | Page |

| •        | Updated the PSKIP rows for the TPS659119KBIPFPRQ1 in the EEPROM Configuration table                                                                             | 49   |

| •        | Added column for TPS659119LBIPFP to and removed the TOP-SIDE MARKING row from the EEPROM CONFIGURATION table in the BOOT CONFIGURATION AND SWITCH-OFF SEQUENCES |      |

Submit Documentation Feedback

| Cr       | nanges from Revision C (August 2013) to Revision D                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page           |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| •        | Changed CDM classification level from C4A to C4B and updated CDM ESD rating to include corner pin values as well as other pin values                                                                                                                                                                                                                                                                                                                                                         | 1              |

| •        | Updated data sheet format to include new document flow and the following new items: Device Information table, Overview section, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section (now contains the glossary), Mechanical, Packaging, and Orderable Information section. Also deleted Appendix A: Functional Registers and moved the register map and descriptions to the Detailed Description section. | 1              |

| •        | Deleted the PARAMETER and TEST CONDITION column headings from the Absolute Maximum Ratings, Recommended Operating Conditions, and External Component Recommendation tables                                                                                                                                                                                                                                                                                                                   | 7              |

| •        | Moved storage temperature range and ESD ratings from the <i>Absolute Maximum Ratings</i> table into the new <i>Handling Ratings</i> table                                                                                                                                                                                                                                                                                                                                                    | 7              |

| •        | Changed the TYP column to NOM in the Recommended Operating Conditions table                                                                                                                                                                                                                                                                                                                                                                                                                  | <mark>7</mark> |

| •        | Replaced Characteristics with Requirements in all timing table titles                                                                                                                                                                                                                                                                                                                                                                                                                        | 7              |

| •        | Split the DC output parameter for each LDO into output voltage, step size, and output accuracy and removed multiple TYP values                                                                                                                                                                                                                                                                                                                                                               | 7              |

| •        | Added column for TPS659119KBIPFP (top-side marking) to the <i>EEPROM CONFIGURATION</i> table in the <i>BOOT CONFIGURATION AND SWITCH-ON AND SWITCH-OFF SEQUENCES</i> section                                                                                                                                                                                                                                                                                                                 | 49             |

| •        | Added pullup resistors to VDDIO on the I <sup>2</sup> C pins in the <i>Application Schematic</i> image                                                                                                                                                                                                                                                                                                                                                                                       | 118            |

| •        | Added T659119KB device marking information to the PACKAGE OPTION ADDENDUM and PACKAGE MATERIALS INFORMATION pages at the end of the document                                                                                                                                                                                                                                                                                                                                                 | 123            |

| Cł       | nanges from Revision B (April 2013) to Revision C                                                                                                                                                                                                                                                                                                                                                                                                                                            | Page           |

| <u>.</u> | Added Storage Temperature range to ABSOLUTE MAXIMUM RATINGS table                                                                                                                                                                                                                                                                                                                                                                                                                            | 7              |

| Cł       | nanges from Revision A (April 2013) to Revision B                                                                                                                                                                                                                                                                                                                                                                                                                                            | Page           |

| •        | Changed 0x20 to 0x22 for TPS659119HAIPFPRQ1 column in EEPROM Configuration table.                                                                                                                                                                                                                                                                                                                                                                                                            | 49             |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

# 5 Description (continued)

The device also includes eight general-purpose LDOs providing a wide range of voltage and current capabilities. Five of the LDOs support 1 to 3.3 V with 100-mV steps, and three LDOs support 1 to 3.3 V with 50-mV steps. All LDOs are fully controllable by the  $I^2C$  interface.

In addition to the power regulators, the device contains nine configurable GPIOs with multiplexing features to support a wide variety of functions. The device also includes an embedded power controller to manage the power sequencing requirements of the system. The power sequencing is programmable by EEPROM.

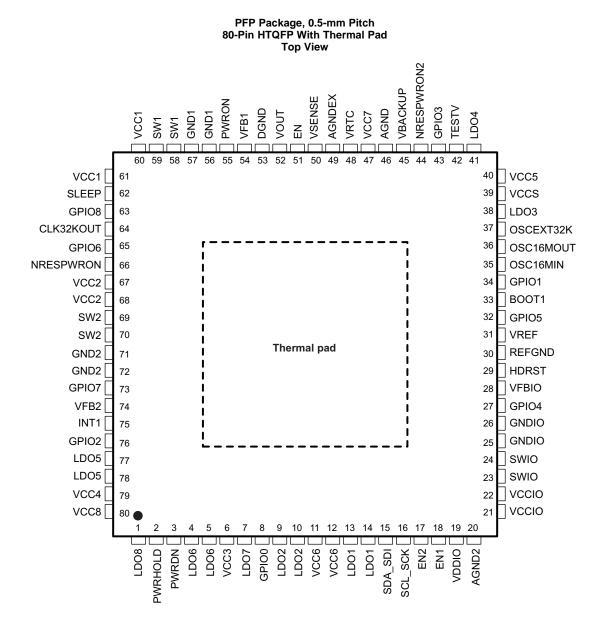

# 6 Pin Configuration and Functions

Product Folder Links: TPS659119-Q1

Submit Documentation Feedback

## **Pin Functions**

| PIN       | PIN FUNCTIONS |         |           |                                                                                                       |              |                                  |  |  |  |

|-----------|---------------|---------|-----------|-------------------------------------------------------------------------------------------------------|--------------|----------------------------------|--|--|--|

| NAME      | NO.           | TYPE    | I/O       | DESCRIPTION                                                                                           | SUPPLIES     | PU / PD                          |  |  |  |

| LDO8      | 1             | Power   | 0         | LDO regulator output                                                                                  | VCC3, REFGND | PD 5 µA                          |  |  |  |

| PWRHOLD   | 2             | Digital | 1         | Switch-on, switch off control signal and GPI                                                          | VRTC, DGND   | Programmable PD (default active) |  |  |  |

| PWRDN     | 3             | Analog  | I         | Reset input, for example, thermal reset                                                               | VRTC, DGND   | PD                               |  |  |  |

| LDO6      | 5             | Power   | 0         | LDO regulator output                                                                                  | VCC3, REFGND | PD 5 µA                          |  |  |  |

| VCC3      | 6             | Power   | I         | LDO6 and LDO7 power Input                                                                             | VCC3, AGND2  | No                               |  |  |  |

| LDO7      | 7             | Power   | 0         | LDO regulator output                                                                                  | VCC3, REFGND | PD 5 µA                          |  |  |  |

| GPIO0     | 8             | Digital | I/O       | GPIO, push pull and OD as output                                                                      | VCC7, DGND   | OD: external PU                  |  |  |  |

| LDO2      | 9             | Power   | 0         | LDO regulator output                                                                                  | VCC6, REFGND | No                               |  |  |  |

| VCC6      | 11<br>12      | Power   | I         | LDO1, LDO2 power Input                                                                                | VCC6, AGND2  | No                               |  |  |  |

| LDO1      | 13<br>14      | Power   | 0         | LDO regulator output                                                                                  | VCC6, REFGND | No                               |  |  |  |

| SDA_SDI   | 15            | Digital | I/O       | l <sup>2</sup> C bidirectional-data signal and serial-peripheral-interface data input (multiplexed)   | VDDIO, DGND  | External PU                      |  |  |  |

| SCL_SCK   | 16            | Digital | I/O       | I <sup>2</sup> C bidirectional-clock signal and serial-peripheral-interface clock input (multiplexed) | VDDIO, DGND  | External PU                      |  |  |  |

| EN2       | 17            | Digital | I/O       | Enable for supplies and voltage scaling dedicated to I <sup>2</sup> C data                            | VDDIO, DGND  | External PU                      |  |  |  |

| EN1       | 18            | Digital | I/O       | Enable for supplies and voltage scaling dedicated to I <sup>2</sup> C clock                           | VDDIO, DGND  | External PU                      |  |  |  |

| VDDIO     | 19            | Power   | I         | Digital I/O supply                                                                                    | VDDIO, DGND  | No                               |  |  |  |

| AGND2     | 20            | Power   | I/O       | Analog ground                                                                                         | AGND2        | No                               |  |  |  |

| VCCIO     | 21<br>22      | Power   | 1         | VIO DC-DC power Input                                                                                 | VCCIO, GNDIO | No                               |  |  |  |

| swio      | 23<br>24      | Power   | 0         | VIO DC-DC switched output                                                                             | VCCIO, GNDIO | No                               |  |  |  |

| GNDIO     | 25<br>26      | Power   | I/O       | VIO DC-DC power ground                                                                                | VCCIO, GNDIO | No                               |  |  |  |

| GPIO4     | 27            | Digital | I/O<br>OD | GPIO                                                                                                  | VRTC, DGND   | OD: External PU                  |  |  |  |

| VFBIO     | 28            | Analog  | I         | VIO feedback voltage                                                                                  | VCC7, DGND   | PD 5 µA                          |  |  |  |

| HDRST     | 29            | Digital | I         | Cold reset                                                                                            | VRTC, DGND   | PD                               |  |  |  |

| REFGND    | 30            | Analog  | I/O       | Reference ground                                                                                      | REFGND       | No                               |  |  |  |

| VREF      | 31            | Analog  | 0         | Bandgap voltage                                                                                       | VCC7, REFGND | No                               |  |  |  |

| GPIO5     | 32            | Digital | I/O<br>OD | GPIO                                                                                                  | VRTC, DGND   | OD: external PU                  |  |  |  |

| BOOT1     | 33            | Digital | I         | Power-up sequence selection                                                                           | VRTC, DGND   | No                               |  |  |  |

| GPIO1     | 34            | Digital | I/O<br>OD | GPIO and LED1 output                                                                                  | VRTC, DGND   | OD: External PU                  |  |  |  |

| OSC16MIN  | 35            | Analog  | ı         | 16.384-MHz crystal oscillator input                                                                   | VCC7, DGND   | External PD if not in use        |  |  |  |

| OSC16MOUT | 36            | Analog  | 0         | 16.384-MHz crystal oscillator output                                                                  | VCC7, DGND   | No                               |  |  |  |

| OSCEXT32K | 37            | Digital | ı         | External 32-kHz clock input                                                                           | VRTC, DGND   | External PD if not in use        |  |  |  |

| LDO3      | 38            | Power   | 0         | LDO regulator output                                                                                  | VCC5, REFGND | PD 5 µA                          |  |  |  |

| VCCS      | 39            | Analog  | I/O       | VCC7 voltage sense input                                                                              | VCC7, DGND   | No                               |  |  |  |

| VCC5      | 40            | Power   | I         | LDO3 and LDO4 power Input                                                                             | VCC5, AGND   | No                               |  |  |  |

| LDO4      | 41            | Power   | 0         | LDO regulator output                                                                                  | VCC5, REFGND | PD 5 μA                          |  |  |  |

| TESTV     | 42            | Analog  | 0         | Analog test output (DFT)                                                                              | VCC7, AGND   | No                               |  |  |  |

Copyright © 2013–2016, Texas Instruments Incorporated

Submit Documentation Feedback

# Pin Functions (continued)

| PIN        |          |         |            | Fin Functions (continued)                     |                  |                                                                        |

|------------|----------|---------|------------|-----------------------------------------------|------------------|------------------------------------------------------------------------|

| NAME       | NO.      | TYPE    | 1/0        | DESCRIPTION                                   | SUPPLIES         | PU / PD                                                                |

| GPIO3      | 43       | Digital | I/O<br>OD  | GPIO and LED2 output                          | VRTC, DGND       | OD: External PU                                                        |

| NRESPWRON2 | 44       | Digital | O OD       | Second NRESPWRON output                       | VRTC, DGND       | PD active during<br>device OFF<br>state.External pullup<br>when ACTIVE |

| VBACKUP    | 45       | Power   | I          | Tie this pin to AGND                          | VBACKUP, AGND    | No                                                                     |

| AGND       | 46       | Power   | I/O        | Analog ground                                 | AGND             | No                                                                     |

| VCC7       | 47       | Power   | I          | VRTC power input and analog references supply | VCC7, REFGND     | No                                                                     |

| VRTC       | 48       | Power   | 0          | LDO regulator output                          | VCC7, REFGND     | PD 5 µA                                                                |

| AGNDEX     | 49       | Power   | I/O        | EXTCTRL resistive divider ground              | AGNDEX           | No                                                                     |

| VSENSE     | 50       | Analog  | I          | EXTCTRL resistive divider output              | VOUT, AGNDEX     | No                                                                     |

| EN         | 51       | Digital | 0          | EXTCTRL enable signal for external converter  | VCC7, DGND       | No                                                                     |

| VOUT       | 52       | Analog  | I          | EXTCTRL resistive divider input               | VOUT, AGNDEX     | No                                                                     |

| DGND       | 53       | Power   | I/O        | Digital ground                                | DGND             | No                                                                     |

| VFB1       | 54       | Analog  | I          | VDD1 feedback voltage                         | Itage VCC7, DGND |                                                                        |

| PWRON      | 55       | Digital | I          | External switch-on control (ON button)        | VCC7, DGND       | Programmable PU (default active)                                       |

| GND1       | 56<br>57 | Power   | I/O        | VDD1 DC-DC power ground                       | VCC1, GND1       | No                                                                     |

| SW1        | 58<br>59 | Power   | 0          | VDD1 DC-DC switched output                    | VCC1, GND1       | No                                                                     |

| VCC1       | 60<br>61 | Power   | ı          | VDD1 DC-DC power Input                        | VCC1, GND1       | No                                                                     |

| SLEEP      | 62       | Digital | ı          | ACTIVE-SLEEP state transition control signal  | VDDIO, DGND      | Programmable PD (default active)                                       |

| GPIO8      | 63       | Digital | I/O,<br>OD | GPIO                                          | VRTC, DGND       | OD: External PU                                                        |

| CLK32KOUT  | 64       | Digital | 0          | 32-kHz clock output                           | VDDIO, DGND      | PD, disabled in<br>ACTIVE or SLEEP<br>state                            |

| GPIO6      | 65       | Digital | I/O,<br>OD | GPIO                                          | VRTC, DGND       | OD: External PU                                                        |

| NRESPWRON  | 66       | Digital | 0          | Power off reset                               | VDDIO, DGND      | PD active during device OFF state                                      |

| VCC2       | 67<br>68 | Power   | I          | VDD2 DC-DC power input                        | VCC2, GND2       | No                                                                     |

| SW2        | 69<br>70 | Power   | 0          | VDD2 DC-DC switched output                    | VCC2, GND2       | No                                                                     |

| GND2       | 71<br>72 | Power   | I/O        | VDD2 DC-DC power ground                       | VCC2, GND2       | No                                                                     |

| GPIO7      | 73       | Digital | I/O,<br>OD | GPIO                                          | VRTC, DGND       | OD: External PU                                                        |

| VFB2       | 74       | Analog  | I          | VDD2 DC-DC feedback voltage                   | VCC7, DGND       | PD 5 μA                                                                |

| INT1       | 75       | Digital | 0          | Interrupt flag                                | VDDIO, DGND      | No                                                                     |

| GPIO2      | 76       | Digital | I/O,<br>OD | GPIO and DC-DC clock synchronization          | VRTC, DGND       | OD: External PU                                                        |

| LDO5       | 77<br>78 | Power   | 0          | LDO regulator output                          | VCC4, REFGND     | PD 5 μA                                                                |

| VCC4       | 79       | Power   | I          | LDO5 power input                              | VCC4, AGND2      | No                                                                     |

| VCC8       | 80       | Power   | 1          | LDO8 power input                              | VCC8, AGND2      | No                                                                     |

Submit Documentation Feedback

# 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                                                                                                                                                                                                                                          |                                                                                  |                 | MIN        | MAX            | UNIT |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------|------------|----------------|------|

|                                                                                                                                                                                                                                                                                          | VCC1, VCC2, VCCIO, VCC3, VCC4, V                                                 | CC5, VCC7, VCC8 | -0.3       | 7              | V    |

| VCC6, VDDIO  SW1, SW2, SWIO  VFB1,VFB2,VFBIO  VOUT, VSENSE  BOOT1  SDA_SDI, SCL_SCK, EN2, EN1, SLEE NRESPWRON  PWRON  PWRON  PWRHOLD, GPIO0  OSCEXT32K, GPIO1, GPIO2, GPIO3, GPIO7, GPIO8 <sup>(2)</sup> HDRST  OSC16MIN, OSC16MOUT  NRESPWRON2 <sup>(2)</sup> PWRDN <sup>(3)</sup> VCCS | VCC6, VDDIO                                                                      |                 |            | 3.6            | V    |

|                                                                                                                                                                                                                                                                                          |                                                                                  | -0.3            | 7          | V              |      |

|                                                                                                                                                                                                                                                                                          | 10 ns Transient                                                                  |                 |            | 7              | V    |

|                                                                                                                                                                                                                                                                                          | VFB1,VFB2,VFBIO                                                                  | -0.3            | 3.6        | V              |      |

|                                                                                                                                                                                                                                                                                          | VOUT, VSENSE                                                                     |                 |            | 7              | V    |

|                                                                                                                                                                                                                                                                                          | BOOT1                                                                            |                 | -0.3       | VRTCMAX + 0.3  | V    |

| Vallaga                                                                                                                                                                                                                                                                                  | SDA_SDI, SCL_SCK, EN2, EN1, SLEEP, INT1, CLK32KOUT, NRESPWRON                    |                 |            | VDDIOMAX + 0.3 | ٧    |

| voltage                                                                                                                                                                                                                                                                                  | PWRON                                                                            |                 |            | 7              | V    |

|                                                                                                                                                                                                                                                                                          | PWRHOLD, GPIO0                                                                   |                 |            | 7              | V    |

|                                                                                                                                                                                                                                                                                          | OSCEXT32K, GPIO1, GPIO2, GPIO3, GPIO4, GPIO5, GPIO6, GPIO7, GPIO8 <sup>(2)</sup> |                 |            | 7              | ٧    |

|                                                                                                                                                                                                                                                                                          | HDRST                                                                            |                 | -0.3       | VRTCMAX + 0.3  | V    |

|                                                                                                                                                                                                                                                                                          | OSC16MIN, OSC16MOUT                                                              |                 | -0.3       | 5.7            | V    |

|                                                                                                                                                                                                                                                                                          | NRESPWRON2 <sup>(2)</sup>                                                        |                 | -0.3       | 7              | V    |

|                                                                                                                                                                                                                                                                                          | PWRDN <sup>(3)</sup>                                                             |                 | -0.3       | 7              | V    |

|                                                                                                                                                                                                                                                                                          | VCCS                                                                             |                 | -0.3       | 7              | V    |

| Peak output current                                                                                                                                                                                                                                                                      | All other pins than power resources                                              |                 | <b>-</b> 5 | 5              | mA   |

| Functional junction temp                                                                                                                                                                                                                                                                 | erature                                                                          |                 | -45        | 150            | °C   |

| Storage temperature, T <sub>st</sub>                                                                                                                                                                                                                                                     | g                                                                                |                 | -55        | 150            | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                    |               |                                                         |                                                 | VALUE | UNIT |

|--------------------|---------------|---------------------------------------------------------|-------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> |                                                 | ±2000 |      |

|                    |               |                                                         | All pins                                        | ±500  | V    |

| (ESD)              | discharge     | Charged-device model (CDM), per AEC Q100-011            | Corner pins (1, 20, 21, 40, 41, 60, 61, and 80) | ±750  | V    |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

<sup>(2)</sup> VRTC supplies the I/O but the I/O can also be driven from VCC7 or to VCC7 voltage level.

<sup>(3)</sup> VRTC supplies the input supplied but can also be driven from VCC7 voltage level.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

Note: VCC7 should be connected to highest supply that is connected to device VCCx pin.

**Exception**: The VCC4, VCC5, VIN, and AVIN inputs can be higher than VCC7. VCCS can be higher than VCC7 if VMBBUF\_BYPASS = 0 (buffer is enabled).

|               |                                                                      | MIN  | NOM   | MAX  | UNIT |

|---------------|----------------------------------------------------------------------|------|-------|------|------|

|               | VCC5, VCCS                                                           | 2.7  |       | 5.5  | V    |

| Input voltage | VCC3, VCC4, VCC8                                                     | 1.7  |       | 5.5  | V    |

|               | VCC1, VCC2, VCCIO, VCC7                                              | 4    | 5     | 5.5  | V    |

|               | VCC6, VDDIO                                                          | 1.4  | 3.3   | 3.6  | V    |

|               | VSENSE                                                               | -0.1 |       | 6.5  | V    |

|               | PWRON                                                                | 0    | 3.8   | 5.5  | V    |

|               | SDA_SDI, SCL_SCK, EN2, EN1, SLEEP, INT1, CLK32KOUT                   | 1.65 | VDDIO | 3.45 | V    |

|               | PWRHOLD, HDRTS                                                       | 1.65 | VRTC  | 5.5  | V    |

|               | GPIO0, GPIO1, GPIO2, GPIO3, GPIO4, GPIO5, GPIO6, GPIO7, GPIO8, PWRDN | 1.65 | VRTC  | 5.5  | V    |

|               | VCCS                                                                 | 0    |       | 5.5  | V    |

|               | OSCEXT32K                                                            | 0    |       | 5.5  | V    |

#### 7.4 Thermal Characteristics

over operating free-air temperature range (unless otherwise noted)

|                      |                                              | TPS659119-Q1 |      |  |

|----------------------|----------------------------------------------|--------------|------|--|

|                      | THERMAL METRIC <sup>(1)</sup>                | PFP (HTQFP)  | UNIT |  |

|                      |                                              | 80 PINS      |      |  |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 34.1         | °C/W |  |

| $R_{\theta JC(top)}$ | Junction-to-case(top) thermal resistance     | 9.6          | °C/W |  |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 10.1         | °C/W |  |

| ΨЈΤ                  | Junction-to-top characterization parameter   | 0.3          | °C/W |  |

| ΨЈВ                  | Junction-to-board characterization parameter | 9.9          | °C/W |  |

| $R_{\theta JC(bot)}$ | Junction-to-case(bottom) thermal resistance  | 0.9          | °C/W |  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 7.5 External Component Recommendation

For crystal oscillator components, see the 32-kHz RTC Clock section. **Note**: The VCC7 supply must have enough capacitance to specify that when the supply is switched off, voltage does not fall at a rate faster than 10 mV/ms. This ensures that RTC domain data is maintained.

|                      |                                     |                               | MIN | NOM | MAX | UNIT      |

|----------------------|-------------------------------------|-------------------------------|-----|-----|-----|-----------|

| POWER RE             | FERENCES                            |                               |     |     |     |           |

| C <sub>O(VREF)</sub> | VREF filtering capacitor            | Connected from VREF to REFGND |     | 100 |     | nF        |

| VDD1 SMPS            | 3                                   |                               |     |     |     |           |

| C <sub>I(VCC1)</sub> | Input capacitor                     | X5R or X7R dielectric         |     | 10  |     | μF        |

| C <sub>O(VDD1)</sub> | Output filter capacitor             | X5R or X7R dielectric         | 4   | 10  | 12  | μF        |

|                      | C <sub>O</sub> filter capacitor ESR | f = 3 MHz                     |     | 10  | 300 | mΩ        |

| L <sub>O(VDD1)</sub> | Inductor                            |                               |     | 2.2 |     | μH        |

| DCRL                 | L <sub>O</sub> inductor dc resistor |                               |     |     | 125 | $m\Omega$ |

| VDD2 SMPS            | 3                                   | •                             | •   |     | · · |           |

| C <sub>I(VCC2)</sub> | Input capacitor                     | X5R or X7R dielectric         |     | 10  |     | μF        |

| C <sub>O(VDD2)</sub> | Output filter capacitor             | X5R or X7R dielectric         | 4   | 10  | 12  | μF        |

|                      | C <sub>O</sub> filter capacitor ESR | f = 3 MHz                     |     | 10  | 300 | mΩ        |

| L <sub>O(VDD2)</sub> | Inductor                            |                               |     | 2.2 |     | μH        |

## **External Component Recommendation (continued)**

For crystal oscillator components, see the 32-kHz RTC Clock section. **Note**: The VCC7 supply must have enough capacitance to specify that when the supply is switched off, voltage does not fall at a rate faster than 10 mV/ms. This ensures that RTC domain data is maintained.

|                       |                                        |                                 | MIN                                   | NOM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | MAX  | UNIT |

|-----------------------|----------------------------------------|---------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|

| DCRL                  | L <sub>O</sub> inductor dc resistor    |                                 |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 125  | mΩ   |

| VIO SMPS              |                                        |                                 | · · · · · · · · · · · · · · · · · · · |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |      |

| C <sub>I(VCCIO)</sub> | Input capacitor                        | X5R or X7R dielectric           |                                       | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      | μF   |

| C <sub>O(VIO)</sub>   | Output filter capacitor                | X5R or X7R dielectric           | 4                                     | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 12   | μF   |

|                       | C <sub>O</sub> filter capacitor ESR    | f = 3 MHz                       |                                       | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 300  | mΩ   |

| L <sub>O(VIO)</sub>   | Inductor                               |                                 |                                       | 2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      | μΗ   |

| DCR <sub>L</sub>      | L <sub>O</sub> inductor dc resistor    |                                 |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 125  | mΩ   |

| LDO1                  |                                        |                                 |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |      |

| C <sub>I(VCC6)</sub>  | Input capacitor                        | X5R or X7R dielectric           |                                       | 4.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      | μF   |

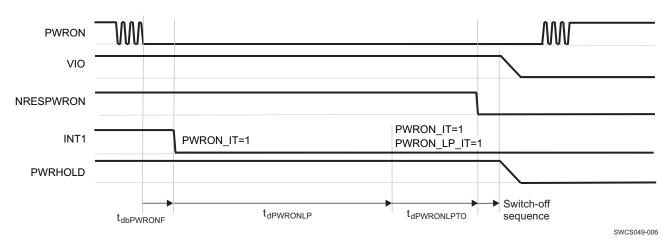

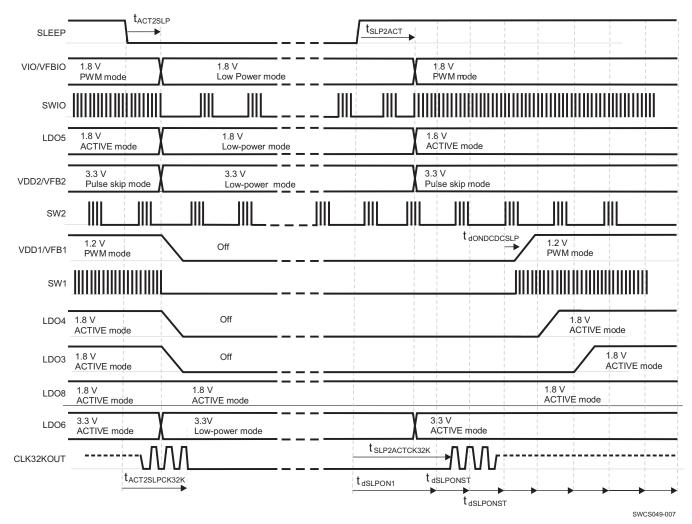

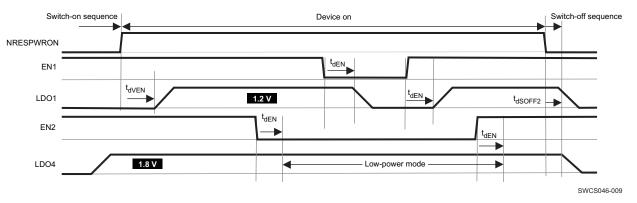

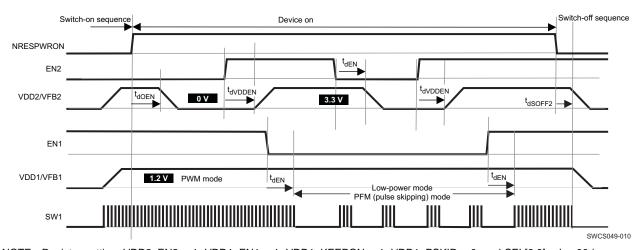

| C <sub>O(LDO1)</sub>  | Output filtering capacitor             |                                 | 0.8                                   | 2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.64 | μF   |