# Die on Carrier, Silicon Digital Attenuator, 2 dB LSB, 4-Bit, 10 MHz to 60 GHz

#### **FEATURES**

- ▶ Ultrawideband frequency range: 10 MHz to 60 GHz

- ▶ Attenuation range: 22 dB with 2 dB steps

- ▶ Bond pads for wire bond and ribbon bond

- ▶ Low insertion loss

- ▶ 1.3 dB typical up to 20 GHz

- ▶ 2.0 dB typical up to 44 GHz

- ▶ 2.7 dB typical up to 55 GHz

- ▶ Attenuation accuracy

- ▶ ±(0.3 + 1.0% of attenuation state) typical up to 20 GHz

- $\blacktriangleright$  ±(0.4 + 4.0% of attenuation state) typical up to 44 GHz

- ▶ ±(0.4 + 6.0% of attenuation state) typical up to 55 GHz

- ▶ Typical step error

- ▶ ±0.30 dB typical up to 20 GHz

- ▶ ±0.65 dB typical up to 44 GHz

- ▶ ±1.10 dB typical up to 55 GHz

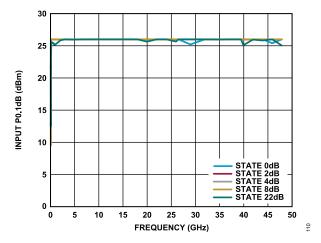

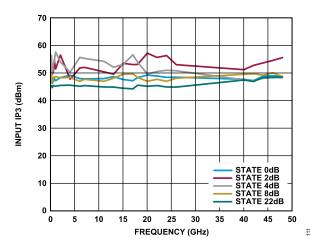

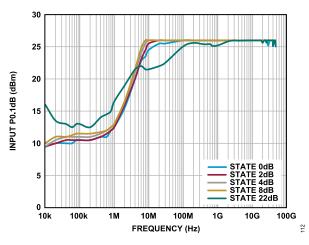

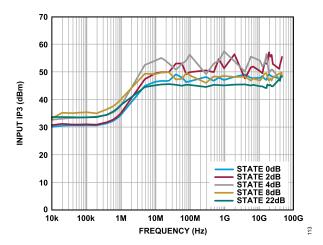

- ▶ High input linearity

- ▶ P0.1dB: 25.5 dBm typical

- ▶ IP3: 45 dBm typical

- ▶ High RF power handling

- ▶ 23 dBm steady state and hot switching, average

- ▶ 24 dBm steady state and hot switching, peak

- ▶ Tight distribution in relative phase

- ▶ No low frequency spurious signals

- ▶ Parallel mode control, CMOS/LVTTL compatible

- ▶ RF amplitude settling time (0.1 dB of final RF output): 175 ns

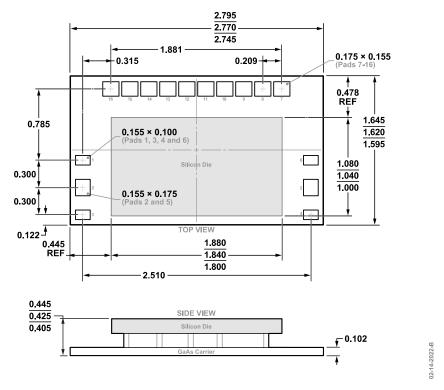

- ▶ 16-pad, 2.770 mm × 1.620 mm, die on carrier [CHIP]

#### **APPLICATIONS**

- Industrial scanners

- Test and instrumentation

- ► Cellular infrastructure: 5G millimeterwave

- Military radios, radars, electronic counter measures (ECMs)

- Microwave radios and very small aperture terminals (VSATs)

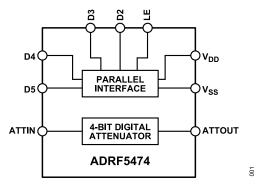

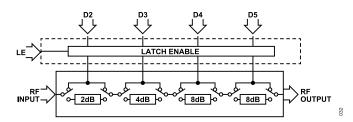

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

#### **GENERAL DESCRIPTION**

The ADRF5474 is a 4-bit digital attenuator with 22 dB attenuation control range in 2 dB steps manufactured in a silicon process attached on a gallium arsenide (GaAs) carrier substrate. The substrate incorporates the bond pads for chip and wire assembly, and the bottom of the device is metalized and connected to ground.

This device operates from 10 MHz to 60 GHz with better than 2.7 dB of insertion loss and excellent attenuation accuracy at 55 GHz. The ADRF5474 has a RF input power handling capability of 23 dBm average and 24 dBm peak for all states.

The ADRF5474 requires a dual-supply voltage of +3.3 V and -3.3 V. The device features parallel mode control, and complementary metal-oxide semiconductor (CMOS)-/low voltage transistor to transistor logic (LVTTL)-compatible controls.

The ADRF5474 is designed to match a characteristic impedance of 50 O.

# **TABLE OF CONTENTS**

| Features                                    | 1 |

|---------------------------------------------|---|

| Applications                                | 1 |

| Functional Block Diagram                    | 1 |

| General Description                         | 1 |

| Specifications                              | 3 |

| Electrical Specifications                   | 3 |

| Timing Specifications                       | 4 |

| Absolute Maximum Ratings                    | 5 |

| Thermal Resistance                          | 5 |

| Power Derating Curves                       | 5 |

| Electrostatic Discharge (ESD) Ratings       | 5 |

| ESD Caution                                 | 6 |

| Pad Configuration and Function Descriptions | 7 |

| Interface Schematics                        | 7 |

|                                             |   |

| Typical Performance Characteristics       | 8  |

|-------------------------------------------|----|

| Insertion Loss, Return Loss, State Error, |    |

| Step Error, and Relative Phase            | 8  |

| Input Power Compression and Third-Order   |    |

| Intercept                                 | 10 |

| Theory of Operation                       | 11 |

| Power Supply                              | 11 |

| RF Input and Output                       | 11 |

| Parallel Mode Interface                   | 12 |

| Applications Information                  | 13 |

| Die Assembly                              | 13 |

| Handling, Mounting and Epoxy Die Attach   | 13 |

| Outline Dimensions                        | 14 |

| Ordering Guide                            | 14 |

# **REVISION HISTORY**

5/2022—Revision 0: Initial Version

analog.com Rev. 0 | 2 of 14

# **SPECIFICATIONS**

# **ELECTRICAL SPECIFICATIONS**

$V_{DD}$  = 3.3 V,  $V_{SS}$  = -3.3 V, control voltages = 0 V or  $V_{DD}$ , die temperature ( $T_{DIE}$ ) = 25°C, and 50  $\Omega$  system, unless otherwise noted.

S-parameters are measured with microstrip launchers and 3 mil width ribbon bonds using ground-signal-ground (GSG) probes. The launchers are deembeded. See the Applications Information section for assembly details.

Table 1.

| Parameter                                               | Test Conditions/Comments                                          | Min | Тур                     | Max    | Unit    |

|---------------------------------------------------------|-------------------------------------------------------------------|-----|-------------------------|--------|---------|

| FREQUENCY RANGE                                         |                                                                   | 10  |                         | 60,000 | MHz     |

| INSERTION LOSS                                          | 10 MHz to 20 GHz                                                  |     | 1.3                     |        | dB      |

|                                                         | 20 GHz to 44 GHz                                                  |     | 2.0                     |        | dB      |

|                                                         | 44 GHz to 55 GHz                                                  |     | 2.7                     |        | dB      |

|                                                         | 55 GHz to 60 GHz                                                  |     | 4.0                     |        | dB      |

| RETURN LOSS                                             | ATTIN and ATTOUT, all attenuation states                          |     |                         |        |         |

|                                                         | 10 MHz to 20 GHz                                                  |     | 13                      |        | dB      |

|                                                         | 20 GHz to 44 GHz                                                  |     | 11                      |        | dB      |

|                                                         | 44 GHz to 55 GHz                                                  |     | 9                       |        | dB      |

|                                                         | 55 GHz to 60 GHz                                                  |     | 6                       |        | dB      |

| ATTENUATION                                             |                                                                   |     |                         |        |         |

| Range                                                   | Between minimum and maximum attenuation states                    |     | 22                      |        | dB      |

| Step Size                                               | Between any successive attenuation states                         |     | 2                       |        | dB      |

| Accuracy                                                | Referenced to insertion loss                                      |     |                         |        |         |

|                                                         | 10 MHz to 20 GHz                                                  |     | ±(0.3 + 1.0% of state)  |        | dB      |

|                                                         | 20 GHz to 44 GHz                                                  |     | ±(0.4 + 4.0% of state)  |        | dB      |

|                                                         | 44 GHz to 55 GHz                                                  |     | ±(0.4 + 6.0% of state)  |        | dB      |

|                                                         | 55 GHz to 60 GHz                                                  |     | ±(0.4 + 12.0% of state) |        | dB      |

| Step Error                                              | Between any successive state                                      |     |                         |        |         |

|                                                         | 10 MHz to 20 GHz                                                  |     | ±0.30                   |        | dB      |

|                                                         | 20 GHz to 44 GHz                                                  |     | ±0.65                   |        | dB      |

|                                                         | 44 GHz to 55 GHz                                                  |     | ±1.10                   |        | dB      |

|                                                         | 55 GHz to 60 GHz                                                  |     | ±1.30                   |        | dB      |

| RELATIVE PHASE                                          | Referenced to insertion loss                                      |     |                         |        |         |

|                                                         | 10 MHz to 20 GHz                                                  |     | 25                      |        | Degrees |

|                                                         | 20 GHz to 44 GHz                                                  |     | 60                      |        | Degrees |

|                                                         | 44 GHz to 55 GHz                                                  |     | 75                      |        | Degrees |

|                                                         | 55 GHz to 60 GHz                                                  |     | 85                      |        | Degrees |

| SWITCHING CHARACTERISTICS                               | All attenuation states at input power (P <sub>IN</sub> ) = 10 dBm |     |                         |        |         |

| Rise and Fall Time ( $t_{RISE}$ and $t_{FALL}$ )        | 10% to 90% of RF output                                           |     | 50                      |        | ns      |

| On and Off Time (t <sub>ON</sub> and t <sub>OFF</sub> ) | 50% triggered control to 90% of RF output                         |     | 100                     |        | ns      |

| RF Amplitude Settling Time                              |                                                                   |     |                         |        |         |

| 0.1 dB                                                  | 50% triggered control to 0.1 dB of final RF output                |     | 175                     |        | ns      |

| 0.05 dB                                                 | 50% triggered control to 0.05 dB of final RF output               |     | 225                     |        | ns      |

| Overshoot                                               |                                                                   |     | 2                       |        | dB      |

| Undershoot                                              |                                                                   |     | 0.75                    |        | dB      |

| RF Phase Settling Time                                  | Frequency = 40 GHz                                                |     |                         |        |         |

| 5°                                                      | 50% triggered control to 5° of final RF output                    |     | 105                     |        | ns      |

| 1°                                                      | 50% triggered control to 1° of final RF output                    |     | 120                     |        | ns      |

| INPUT LINEARITY <sup>1</sup>                            | 100 MHz to 50 GHz                                                 |     |                         |        |         |

| 0.1 dB Power Compression (P0.1dB)                       |                                                                   |     | 25.5                    |        | dbm     |

analog.com Rev. 0 | 3 of 14

## **SPECIFICATIONS**

Table 1.

| Parameter                        | Test Conditions/Comments                                                                                 | Min   | Тур  | Max      | Unit |

|----------------------------------|----------------------------------------------------------------------------------------------------------|-------|------|----------|------|

| Third-Order Intercept (IP3)      | Two-tone $P_{IN}$ = 12 dBm per tone, $\Delta f$ = 1 MHz, all attenuation states                          |       | 45   |          | dBm  |

| DIGITAL CONTROL INPUTS           | LE, D2, D3, D4, and D5                                                                                   |       |      |          |      |

| Voltage                          |                                                                                                          |       |      |          |      |

| Low (V <sub>INL</sub> )          |                                                                                                          | 0     |      | 0.8      | V    |

| High (V <sub>INH</sub> )         |                                                                                                          | 1.2   |      | 3.3      | V    |

| Current                          |                                                                                                          |       |      |          |      |

| Low (I <sub>INL</sub> )          |                                                                                                          |       | -10  |          | μA   |

| High (I <sub>INH</sub> )         |                                                                                                          |       | <1   |          | μA   |

| SUPPLY CURRENT                   |                                                                                                          |       |      |          |      |

| Positive Supply Current          |                                                                                                          |       |      |          |      |

| Bias Low                         | LE, D2, D3, D4, and D5 = 0 V                                                                             |       | 52   |          | μA   |

| Bias High                        | LE, D2, D3, D4, and D5 = 3.3 V                                                                           |       | 2    |          | μA   |

| Negative Supply Current          |                                                                                                          |       | -110 |          | μA   |

| RECOMMENDED OPERATING CONDITIONS |                                                                                                          |       |      |          |      |

| Supply Voltage                   |                                                                                                          |       |      |          |      |

| Positive (V <sub>DD</sub> )      |                                                                                                          | 3.15  |      | 3.45     | V    |

| Negative (V <sub>SS</sub> )      |                                                                                                          | -3.45 |      | -3.15    | V    |

| Digital Control Voltage          |                                                                                                          | 0     |      | $V_{DD}$ | V    |

| RF Power Handling <sup>2</sup>   | Frequency = 100 MHz to 50 GHz, T <sub>DIE</sub> <sup>3</sup> = 85°C, <sup>4</sup> all attenuation states |       |      |          |      |

| Input at ATTIN                   | Steady state, average                                                                                    |       |      | 23       | dBm  |

|                                  | Steady state, peak                                                                                       |       |      | 24       | dBm  |

|                                  | Hot switching, average                                                                                   |       |      | 23       | dBm  |

|                                  | Hot switching, peak                                                                                      |       |      | 24       | dBm  |

| Input at ATTOUT                  | Steady state, average                                                                                    |       |      | 15       | dBm  |

|                                  | Steady state, peak                                                                                       |       |      | 16       | dBm  |

|                                  | Hot switching, average                                                                                   |       |      | 15       | dBm  |

|                                  | Hot switching, peak                                                                                      |       |      | 16       | dBm  |

| $T_{DIE}^{3}$                    |                                                                                                          | -40   |      | +105     | °C   |

<sup>&</sup>lt;sup>1</sup> Input linearity performance degrades over frequency, see Figure 19 and Figure 22.

# **TIMING SPECIFICATIONS**

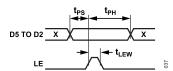

See Figure 24 for the timing diagrams.

Table 2.

| Parameter        | Description                           | Min | Тур | Max | Unit |

|------------------|---------------------------------------|-----|-----|-----|------|

| t <sub>LEW</sub> | Minimum LE pulse width, see Figure 24 |     | 10  |     | ns   |

| t <sub>PH</sub>  | Hold time, see Figure 24              |     | 10  |     | ns   |

| t <sub>PS</sub>  | Setup time, see Figure 24             |     | 2   |     | ns   |

analog.com Rev. 0 | 4 of 14

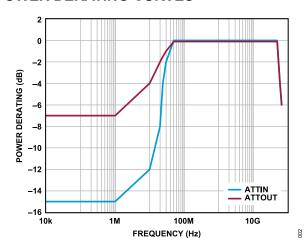

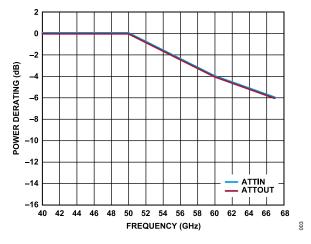

<sup>&</sup>lt;sup>2</sup> For power derating over frequency, see Figure 2 to Figure 3. Applicable for all ATTIN and ATTOUT power specifications.

$<sup>^{3}</sup>$  T<sub>DIE</sub> refers to the bottom of the die on carrier.

$<sup>^4</sup>$  For 105°C operation, the power handling degrades from the  $T_{DIE}$  = 85°C specifications by 3 dB.

#### **ABSOLUTE MAXIMUM RATINGS**

Table 3.

| Parameter                                                                                 | Rating                            |

|-------------------------------------------------------------------------------------------|-----------------------------------|

| Positive Supply Voltage                                                                   | -0.3 V to +3.6 V                  |

| Negative Supply Voltage                                                                   | -3.6 V to +0.3 V                  |

| Digital Control Inputs                                                                    |                                   |

| Voltage                                                                                   | -0.3 V to V <sub>DD</sub> + 0.3 V |

| Current                                                                                   | 3 mA                              |

| RF Power <sup>1</sup> (Frequency = 100 MHz to 50 GHz, $T_{\rm DIE}$ = 85°C <sup>2</sup> ) |                                   |

| Input at ATTIN                                                                            |                                   |

| Steady State, Average                                                                     | 24 dBm                            |

| Steady State, Peak                                                                        | 25 dBm                            |

| Hot Switching, Average                                                                    | 24 dBm                            |

| Hot Switching, Peak                                                                       | 25 dBm                            |

| Input at ATTOUT                                                                           |                                   |

| Steady State, Average                                                                     | 16 dBm                            |

| Steady State, Peak                                                                        | 17 dBm                            |

| Hot Switching, Average                                                                    | 16 dBm                            |

| Hot Switching, Peak                                                                       | 17 dBm                            |

| RF Power Under Unbiased Condition (V <sub>DD</sub> and                                    |                                   |

| $V_{SS} = 0 V$                                                                            |                                   |

| Input at ATTIN                                                                            | 17 dBm                            |

| Input at ATTOUT                                                                           | 9 dBm                             |

| Temperature                                                                               |                                   |

| Junction (T <sub>J</sub> )                                                                | 135°C                             |

| Storage                                                                                   | −55°C to +150°C                   |

| Processing                                                                                | 170°C                             |

| Continuous Power Dissipation (P <sub>DISS</sub> )                                         | 0.20 W                            |

- For power derating over frequency, see Figure 2 and Figure 3. Applicable for all ATTIN and ATTOUT power specifications.

- For 105°C operation, the power handling degrades from the T<sub>DIE</sub> = 85°C specifications by 3 dB.

Stresses at or above those listed under absolute maximum ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JC}$  is the junction to case bottom (channel to carrier bottom) thermal resistance.

Table 4. Thermal Resistance

| Package Type | $\theta_{JC}$ | Unit |

|--------------|---------------|------|

| C-16-5       | 250           | °C/W |

#### **POWER DERATING CURVES**

Figure 2. Power Derating vs. Frequency, Low Frequency Detail, T<sub>DIE</sub> = 85°C

Figure 3. Power Derating vs. Frequency, High Frequency Detail, T<sub>DIE</sub> = 85°C

# **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.

analog.com Rev. 0 | 5 of 14

# **ABSOLUTE MAXIMUM RATINGS**

# **ESD Ratings for ADRF5474**

Table 5. ADRF5474, 16-Pad Die on Carrier [CHIP]

| ESD Model              | Withstand Threshold (V)           |

|------------------------|-----------------------------------|

| Human Body Model (HBM) | ±250                              |

|                        | ±250 for ATTIN and ATTOUT Pads    |

|                        | ±2000 for Supply and Control Pads |

# **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. 0 | 6 of 14

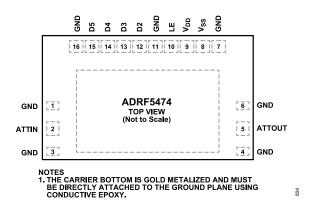

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 4. Pad Configuration

Table 6. Pad Function Descriptions

| Pad No.               | Mnemonic        | Description                                                                                                                                         |

|-----------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3, 4, 6, 7, 11, 16 | GND             | Ground. Bonding of these ground pads are optional. See the Applications Information section.                                                        |

| 2                     | ATTIN           | Attenuator Input. No dc blocking capacitor is necessary when the RF line potential is equal to 0 V dc. See Figure 5 for the interface schematic.    |

| 5                     | ATTOUT          | Attenuator Output. No dc blocking capacitor is necessary when the RF line potential is equal to 0 V dc. See Figure 5 for the interface schematic.   |

| 8                     | V <sub>SS</sub> | Negative Supply Input. See Figure 8 for the interface schematic.                                                                                    |

| 9                     | $V_{DD}$        | Positive Supply Input. See Figure 7 for the interface schematic.                                                                                    |

| 10                    | LE              | Latch Enable Input. See the Theory of Operation section for more information. See Figure 6 for the interface schematic.                             |

| 12                    | D2              | Parallel Control Input for 2 dB Attenuator Bit. See the Theory of Operation section for more information. See Figure 6 for the interface schematic. |

| 13                    | D3              | Parallel Control Input for 4 dB Attenuator Bit. See the Theory of Operation section for more information. See Figure 6 for the interface schematic. |

| 14                    | D4              | Parallel Control Input for 8 dB Attenuator Bit.See the Theory of Operation section for more information. See Figure 6 for the interface schematic.  |

| 15                    | D5              | Parallel Control Input for 8 dB Attenuator Bit. See the Theory of Operation section for more information. See Figure 6 for the interface schematic. |

|                       | Carrier Bottom  | The carrier bottom is gold metalized and must be directly attached to the ground plane using conductive epoxy.                                      |

# **INTERFACE SCHEMATICS**

Figure 5. ATTIN and ATTOUT Interface Schematic

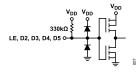

Figure 6. Digital Input Interface Schematic (LE, D2, D3, D4, and D5)

Figure 7. V<sub>DD</sub> Input Interface Schematic

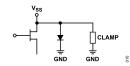

Figure 8. V<sub>SS</sub> Input Interface Schematic

analog.com Rev. 0 | 7 of 14

## TYPICAL PERFORMANCE CHARACTERISTICS

# INSERTION LOSS, RETURN LOSS, STATE ERROR, STEP ERROR, AND RELATIVE PHASE

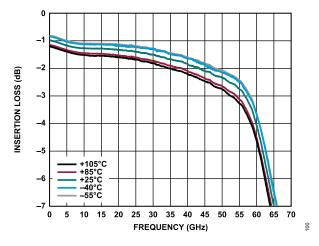

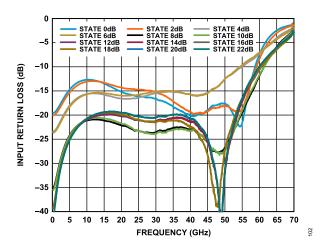

$V_{DD}$  = 3.3 V,  $V_{SS}$  = -3.3 V, control voltages = 0 V or  $V_{DD}$ ,  $T_{DIE}$  = 25°C, and a 50  $\Omega$  system, unless otherwise noted.

S-parameters are measured with microstrip launchers and 3 mil width ribbon bonds using GSG probes. The launchers are deembedded. See the Applications Information section for assembly details.

Figure 9. Insertion Loss vs. Frequency over Temperature

Figure 10. Input Return Loss vs. Frequency

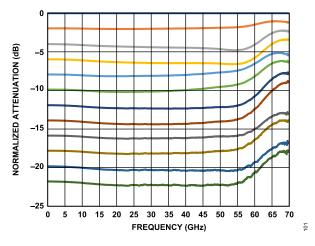

Figure 11. Normalized Attenuation vs. Frequency for All States

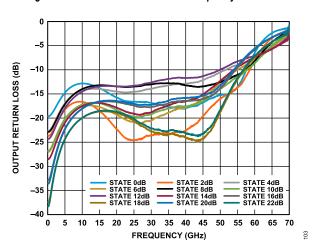

Figure 12. Output Return Loss vs. Frequency

analog.com Rev. 0 | 8 of 14

#### TYPICAL PERFORMANCE CHARACTERISTICS

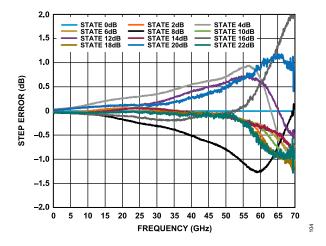

Figure 13. Step Error vs. Frequency

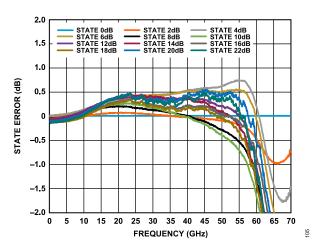

Figure 14. State Error vs. Frequency

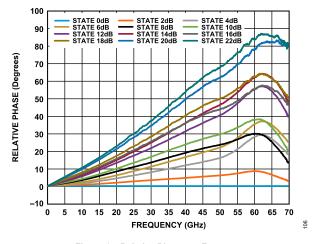

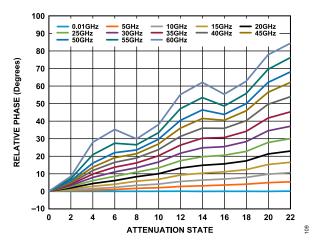

Figure 15. Relative Phase vs. Frequency

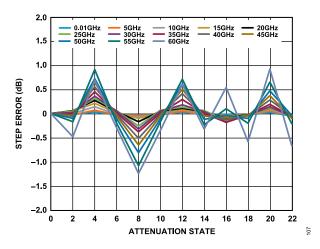

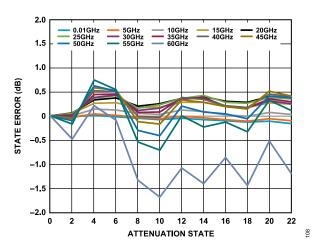

Figure 16. Step Error vs. Attenuation State over Frequency

Figure 17. State Error vs. Attenuation State over Frequency

Figure 18. Relative Phase vs. Attenuation State over Frequency

analog.com Rev. 0 | 9 of 14

# TYPICAL PERFORMANCE CHARACTERISTICS

# INPUT POWER COMPRESSION AND THIRD-ORDER INTERCEPT

$V_{DD}$  = 3.3 V,  $V_{SS}$  = -3.3 V, control voltages = 0 V or  $V_{DD}$ ,  $T_{DIE}$  = 25°C, and a 50  $\Omega$  system, unless otherwise noted.

Figure 19. Input P0.1dB vs. Frequency

Figure 20. Input IP3 vs. Frequency

Figure 21. Input P0.1dB vs. Frequency, Low Frequency Detail

Figure 22. Input IP3 vs. Frequency, Low Frequency Detail

analog.com Rev. 0 | 10 of 14

#### THEORY OF OPERATION

The ADRF5474 incorporates a 4-bit fixed attenuator array that offers an attenuation range of 22 dB in 2 dB steps. An integrated driver provides parallel mode control of the attenuator array.

The ADRF5474 has four digital control inputs, D2 (LSB) to D5 (MSB), to select the desired attenuation state in parallel mode, as shown in Figure 23. Internally, there are two 8 dB stages, and these stages can be controlled by the D4 and D5 pins.

#### **POWER SUPPLY**

The ADRF5474 requires a positive supply voltage applied to the  $V_{DD}$  pad and a negative supply voltage applied to the  $V_{SS}$  pad. Bypassing capacitors are recommended on the supply lines to filter high frequency noise.

The power-up sequence is as follows:

- 1. Connect GND.

- Power up the V<sub>DD</sub> and V<sub>SS</sub> voltages. Power up V<sub>SS</sub> after V<sub>DD</sub> to avoid current transients on V<sub>DD</sub> during ramp up.

- Power up the digital control inputs. The order of the digital control inputs is not important. However, powering the digital control inputs before the V<sub>DD</sub> voltage supply can inadvertently forward bias and damage the internal ESD structures. To avoid

this damage, use a series 1  $k\Omega$  resistor to limit the current flowing into the control pad.

4. Apply an RF input signal to ATTIN or ATTOUT.

The power-down sequence is the reverse order of the power-up sequence.

## **Power-Up State**

The ADRF5474 has an internal pull-up resistor (see Figure 6). The internal pull-up resistor sets the attenuator to the maximum attenuation state (22 dB) when the  $V_{DD}$  and  $V_{SS}$  voltages are applied.

#### RF INPUT AND OUTPUT

Both RF ports (ATTIN and ATTOUT) are dc-coupled to 0 V. No dc blocking is required at the RF ports when the RF line potential is equal to 0 V.

The ADRF5474 supports bidirectional operation at a lower power level. The power handling of the ATTIN and ATTOUT ports are different. Therefore, the bidirectional power handling is defined by the ATTOUT port. Refer to the RF input power specifications in Table 1.

Table 7. Truth Table

|                 | Digital Cor     | ntrol Input <sup>1</sup> |      |                        |

|-----------------|-----------------|--------------------------|------|------------------------|

| D5 <sup>2</sup> | D4 <sup>2</sup> | D3                       | D2   | Attenuation State (dB) |

| Low             | Low             | Low                      | Low  | 0 (reference)          |

| Low             | Low             | Low                      | High | 2.0                    |

| Low             | Low             | High                     | Low  | 4.0                    |

| Low             | Low             | High                     | High | 6.0                    |

| Low             | High            | Low                      | Low  | 8.0                    |

| Low             | High            | Low                      | High | 10.0                   |

| Low             | High            | High                     | Low  | 12.0                   |

| Low             | High            | High                     | High | 14.0                   |

| High            | High            | Low                      | Low  | 16.0                   |

| High            | High            | Low                      | High | 18.0                   |

| High            | High            | High                     | Low  | 20.0                   |

| High            | High            | High                     | High | 22.0                   |

<sup>1</sup> Any combination of the control voltage input states shown in this table provides an attenuation equal to the sum of the bits selected.

<sup>&</sup>lt;sup>2</sup> D4 and D5 both correspond to the 8 dB state. D4 has slightly better state accuracy at higher frequencies.

Figure 23. Simplified Circuit Diagram

analog.com Rev. 0 | 11 of 14

## THEORY OF OPERATION

#### PARALLEL MODE INTERFACE

The ADRF5474 has four digital control inputs, D2 (LSB) to D5 (MSB), to select the desired attenuation state in parallel mode, as shown in Table 7.

There are two modes of parallel operation: direct parallel and latched parallel.

# **Direct Parallel Mode**

To enable direct parallel mode, keep the LE pad high. To change the attenuation state, use the control voltage inputs (D2 to D5) directly. Direct parallel mode is for manual control of the attenuator.

#### **Latched Parallel Mode**

To enable latched parallel mode, the LE pad must be kept low when changing the control voltage inputs (D2 to D5) to set the attenuation state. When the desired state is set, toggle LE high to transfer the 4-bit data to the bypass switches of the attenuator array, and then toggle LE low to latch the change into the device until the next desired attenuation change (see Figure 24 and Table 2 for additional information).

Figure 24. Latched Parallel Mode Timing Diagram

analog.com Rev. 0 | 12 of 14

#### **APPLICATIONS INFORMATION**

#### **DIE ASSEMBLY**

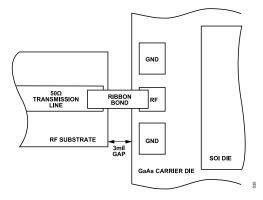

An assembly diagram of the ADRF5474 is shown in Figure 25.

Figure 25. Die Assembly Diagram

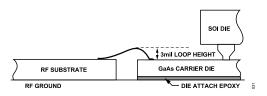

The ADRF5474 is designed to have the optimum RF input and output impedance match with 3 mil × 0.5 mil gold ribbon wire and 3 mil loop height typical. The bonding diagrams are shown in Figure 26 and Figure 27. Alternatively, using multiple wire bonds with equivalent inductance yields similar performance. For RF routing from the device, coplanar wave guide or microstrip transmission lines can be used. No impedance matching is required on the transmission line pad because the device is designed to match internally to the recommended ribbon bond. A spacing of 3 mils from the RF transmission line to the device edge is recommended for optimum performance.

DC pads can be connected using standard 1 mil diameter wire by keeping the wire lengths as short as possible to minimize the parasitic inductance. The dc pads are large enough to accommodate ribbon bonds, if preferred.

All bonds must be thermosonically bonded at a nominal stage temperature of 150°C, and a minimum amount of ultrasonic energy must be applied to achieve reliable bonds.

The device is metalized on the backside, and the ground connection can be done by attaching the device directly to the RF ground plane using a conductive epoxy. In this case, connecting the ground pads is optional but still recommended to ensure a solid ground connection.

Figure 26. Bonding Diagram Top View

Figure 27. Bonding Diagram Side View

# HANDLING, MOUNTING AND EPOXY DIE ATTACH

Keep devices in ESD protective sealed bags for shipment, and store all bare die in a dry nitrogen environment.

For manual picking, it is a common practice to use a pair of tweezers for GaAs devices. However, for die on carrier devices, the use of a vacuum tool is recommended to avoid any damage on the device substrate. Handle these devices in clean environment.

To attach the die with epoxy, apply an amount of epoxy to the mounting surface so that a thin epoxy fillet is observed around the perimeter of the chip after it is placed into position. Set epoxy cure temperatures per the recommendations of the manufacturer and the maximum ratings of the device to minimize accumulated mechanical stress after assembly.

Because both dies are attached with solder joints, users must follow best practices for the thermomechanical design of their module assemblies. The temperature expansion coefficient of the substrate material must match the thermal expansion coefficient of the GaAs and silicon (Si) die. Do not allow warpage or other mechanical deformation on the substrate. Set the die attach process and the epoxy cure temperatures to lower the accumulated stress after assembly.

analog.com Rev. 0 | 13 of 14

## **OUTLINE DIMENSIONS**

Figure 28. 16-Pad Die on Carrier [CHIP] (C-16-5) Dimensions shown in millimeters

## **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description          | Packing Information | Package<br>Option |

|--------------------|-------------------|------------------------------|---------------------|-------------------|

| ADRF5474BCZ        | –40°C to +105°C   | 16-Pad Die on Carrier [CHIP] | Waffle Pack, 50     | C-16-5            |

| ADRF5474BCZ-GP     | –40°C to +105°C   | 16-Pad Die on Carrier [CHIP] | Gel Pack, 50        | C-16-5            |

| ADRF5474BCZ-SX     | –40°C to +105°C   | 16-Pad Die on Carrier [CHIP] | Waffle Pack, 2      | C-16-5            |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.