#### **DESCRIPTION**

The PT16512 is 1/4 duty general-purpose LCD driver that can be used for frequency display in electronic tuners under the control of a microcontroller. The PT16512 can drive an LCD with up to 208 segments directly. The PT16512 can also control up to 8 general-purpose output ports.

#### **APPLICATION**

· Electronic equipment with LCD Display

#### **FEATURES**

- Switching between 1/2 bias and 1/3 bias drive techniques under serial data control.

- Up to 208 segments for 1/4 duty drive can be displayed.

- Serial data control of switching between the segment output port and the general-purpose output port functions.

- Serial data control of frame frequency for common and segment output waveforms.

- High generality, since display data is displayed directly without decoder intervention.

- Built-in OSC circuit

- The INHB pin can force the display to the off state.

- Programmable PWM signal output pins

- AEC-Q100 Grade1 Complaint for Automotive Applications

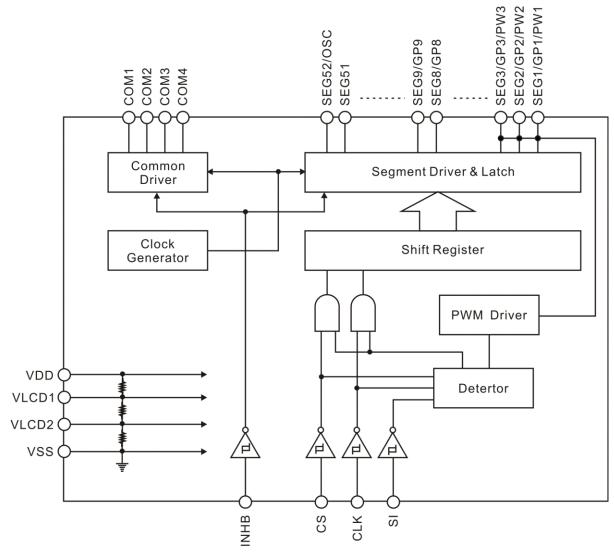

#### **BLOCK DIAGRAM**

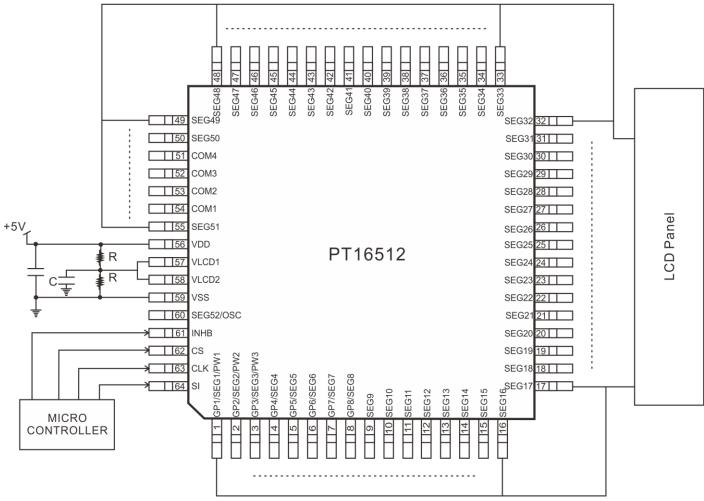

## **APPLICATION CIRCUIT 1**

#### 1/2 BIAS

Notes:

1.10K $\Omega$ >R>1K $\Omega$

3. The resistance value must be decided by the LCD panel size.

V1.2 2 May 2016

<sup>2.</sup>C>0.047µF

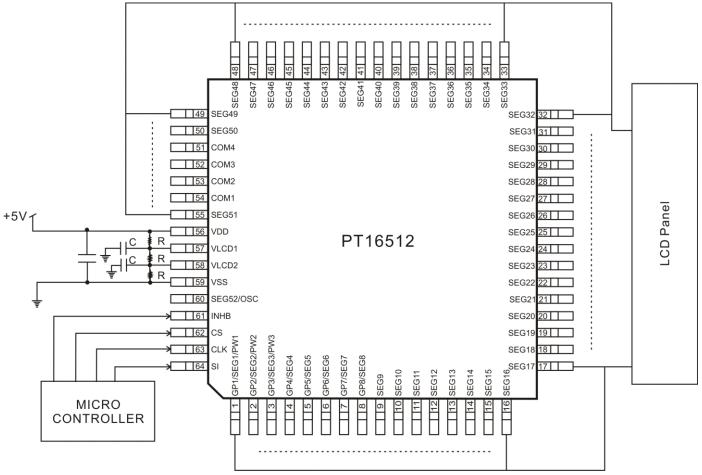

## **APPLICATION CIRCUIT 2**

#### 1/3 BIAS

#### Notes:

- $1.10 \text{K}\Omega > R > 1 \text{K}\Omega$

- 2.C>0.047µF

- 3. The resistance value must be decided by the LCD panel size.

#### **ORDER INFORMATION**

| Valid Part Number | Package Type  | Top Code   |

|-------------------|---------------|------------|

| PT16512-LQ        | 64 Pins, LQFP | PT16512-LQ |

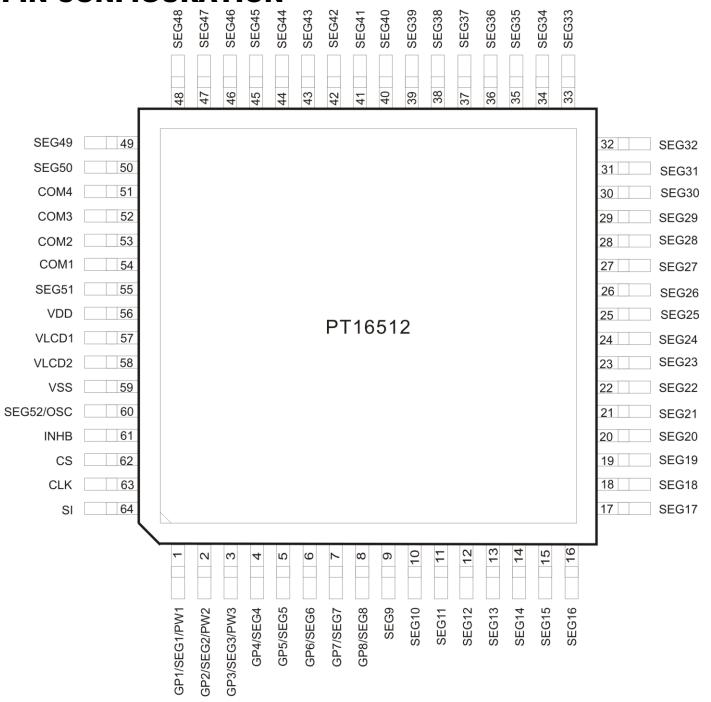

#### **PIN CONFIGURATION**

# **PIN DESCRIPTION**

| Pin Name                                | I/O | Active | Handling<br>when unused                                                                                    | Function                                                                                                                                                                                                                                                                                                                                     | Pin No.               |

|-----------------------------------------|-----|--------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| SEG1/GP1PW1 to<br>SEG3/GP3/PW3          | 0   | -      | Segment outputs for displaying the display data tran-<br>by serial data input. The pins SEG1/GP1/PW1 to SE |                                                                                                                                                                                                                                                                                                                                              | 1 to 3                |

| SEG4/GP4to<br>SEG8/GP8<br>SEG9 to SEG51 | 0   |        | Open                                                                                                       | can be used as general-purpose output ports when set up by the control data.                                                                                                                                                                                                                                                                 | 4 to 8<br>9 to 50, 55 |

| COM1 to COM4                            | 0   | -      | Open                                                                                                       | Common driver outputs. The frame frequency is fo Hz.                                                                                                                                                                                                                                                                                         | 51 to 54              |

| VDD                                     | 1   | -      | -                                                                                                          | Logic block power supply. Provide a voltage in the range 4.5 to 6.0V.                                                                                                                                                                                                                                                                        | 56                    |

| VLCD1                                   | _   | -      | Open                                                                                                       | LCD drive 2/3 bias voltage (middle level) supply. It is possible to supply the 2/3 $V_{DD}$ voltage to this pin externally. This pin must be shorted to $V_{LCD2}$ if 1/2 bias is used.                                                                                                                                                      | 57                    |

| VLCD2                                   | I   | -      | Open                                                                                                       | LCD drive 1/3 bias voltage (middle level) supply. It is possible to supply the 1/3 $V_{DD}$ voltage to this pin externally. This pin must be shorted to $V_{LCD1}$ if 1/2 bias is used.                                                                                                                                                      | 58                    |

| VSS                                     | -   | -      | -                                                                                                          | Ground pin. Connect to ground.                                                                                                                                                                                                                                                                                                               | 59                    |

| SEG52/OSC                               | I/O | -      | VDD                                                                                                        | Segment outputs for displaying the display data transferred by serial data input. The pin SEG52/OSC can be used external frequency input pin when set up by the control data.                                                                                                                                                                | 60                    |

| INHB                                    | I   | L      | GND                                                                                                        | Display off control input  INHB=low (Vss)off SEG1/GP1/PW1 to SEG8/GP8=low (Vss) (These pins are forcibly set to the segment output port function and fixed at the Vss level) SEG9 to SEG52=low (Vss) COM1 to COM4=low (Vss)  INHB=high (VDD)on  Note that serial data transfers can be performed when the display is forced off by this pin. | 61                    |

| CS                                      | I   | Н      |                                                                                                            | Serial data transfer inputs. These pins are connected to the                                                                                                                                                                                                                                                                                 | 62                    |

| CLK                                     | I   |        | GND                                                                                                        | control microprocessor. CS: Chip select                                                                                                                                                                                                                                                                                                      | 63                    |

| SI                                      | I   | -      |                                                                                                            | CLK: Synchronization clock SI: Transfer data                                                                                                                                                                                                                                                                                                 | 64                    |

#### **IMPORTANT NOTICE**

Princeton Technology Corporation (PTC) reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and to discontinue any product without notice at any time. PTC cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a PTC product. No circuit patent licenses are implied.

Princeton Technology Corp. 2F, 233-1, Baociao Road, Sindian Dist., New Taipei City 23145, Taiwan

Tel: 886-2-66296288 Fax: 886-2-29174598

http://www.princeton.com.tw