# HI-3110H, HI-3111H, HI-3112H

### Avionics CAN Controller with Integrated Transceiver and High Operating Temperature

March 2016

### **GENERAL DESCRIPTION**

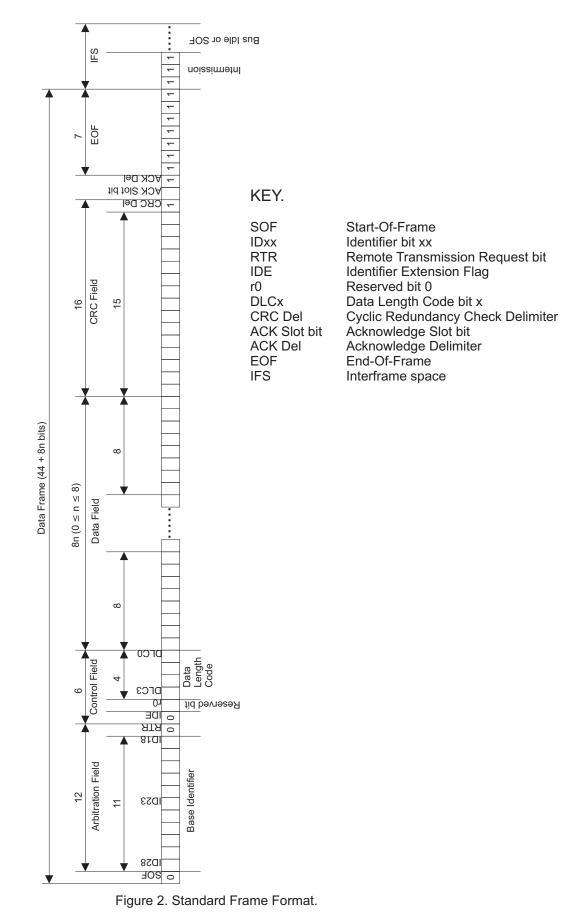

The HI-3110H is a standalone Controller Area Network (CAN) controller with built in transceiver optimized for use in high temperature avionics applications. The device is capable of operating at extended temperature ranges of -55°C to 175°C and provides a complete, integrated, costeffective solution for high temperature avionics applications implementing the CAN 2.0B specification. It can be configured to comply with both the ARINC 825 (General Standardization of CAN Bus Protocol for Airborne Use) and CANaerospace standards. The HI-3110H is capable of transmitting and receiving standard data frames, extended data frames and remote frames. The internal transceiver allows direct connection to the CAN bus without using external components and coupled with the host Serial Peripheral Interface (SPI), results in minimal board space.

The HI-3110H provides the optimum solution for high temperature avionics applications where minimum host (MCU) overhead is required, filtering unwanted messages using a maskable identifier filter and storing up to 8 messages in the receive FIFO. A flexible interrupt scheme allows real time servicing of the FIFO by the host, if required. Transmissions are handled using an 8 message transmit FIFO. A Transmit Enable pin can be used by the host to initiate a transmission. The device also provides monitor or listen-only mode, low power sleep mode, loopback mode for self-test and a re-transmission disable capability (necessary to implement TTCAN protocol).

The HI-3111H is a digital only version of the HI-3110H (no transceiver). This version provides a "protocol only" solution for customers who wish to use an external transceiver and may be used in situations where the customer requires galvanic isolation between the bus and digital protocol logic. The HI-3112H provides an option of a CLKOUT pin instead of a SPLIT pin, which may be used as the main system clock or as a clock input for other devices in the system.

The HI-3110H design has been independently validated by C&S group, GmbH, an ISO/IEC 17025 accredited test house. A copy of the test report is available from Holt on request.

### FEATURES

- Implements CAN version 2.0B with programmable bit rate up to 1Mbit/sec. ISO 11898-5 compliant.

- Extended Temperature Range -55°C to 175°C.

- Configurable to support ARINC 825 and CANaerospace Standards.

- Filtering on ID and first two data bytes for both Standard and Extended Identifiers.

- Permanent dominant timeout protection.

- Serial Peripheral Interface (SPI) (20MHz).

- Standard, Extended and Remote frames supported.

- 8 maskable identifier filters.

- · Loopback mode for self-test.

- Monitor (Listen-only) and Low Power Sleep Modes with automatic wake-up possible.

- 8-message Transmit and Receive FIFOs.

- Internal 16-bit free running counter for time tagging of transmitted or received messages.

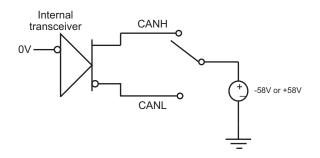

- Short Circuit Protection of -58V to + 58V on CAN\_H, CAN\_L and SPLIT pins (ISO 11898-5).

- Re-transmission disable capability.

- Transmit Enable pin.

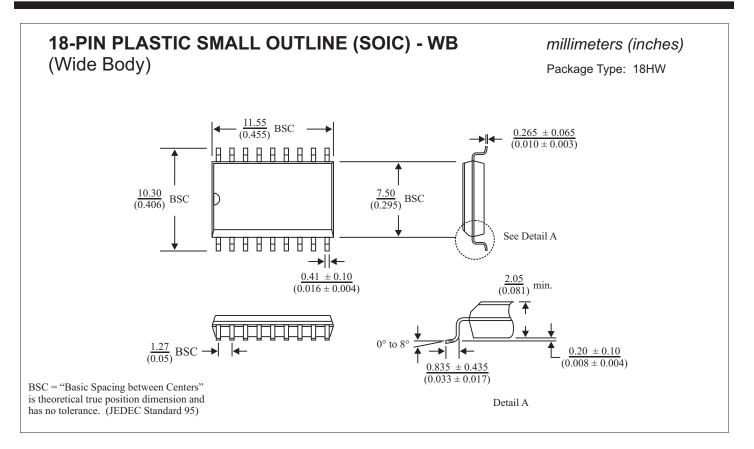

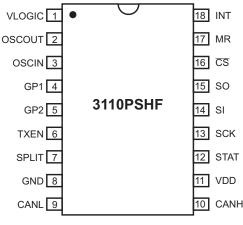

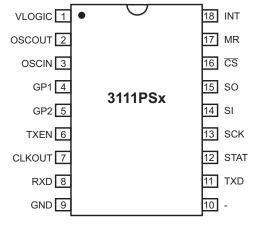

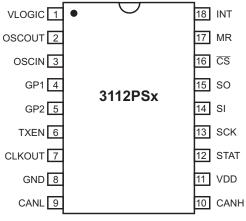

# **PIN CONFIGURATION (Top View)**

18-Pin Plastic SOIC - WB Package

Figure 1. HI-3110H Block Diagram

#### **PRIMARY FUNCTIONS OF HI-3110H LOGIC BLOCKS**

SPI PROTOCOL BLOCK

**REGISTERS BLOCK** Stores configuration data

**BIT TIMING BLOCK** Sets the data strobe and bit period

**TRANSMIT BLOCK** Manages transmission protocol 8 message FIFO Confirmation and time stamp of each message sent is available in the History FIFO

**RECEIVER BLOCK** Manages reception protocol

8 message FIFO with optional filters Handles data transfers between the host and the chip Forwards message data and optional time stamp to the host

> **ERROR BLOCK** Detects and records errors for protocol management

STATUS AND INTERRUPT Provides hardware and software options for managing communications

OSCILLATOR Configuration chooses either the crystal oscillator or and external clock

### TRANSCEIVER

Analog interface connects directly to the CAN bus

# **PIN DESCRIPTIONS**

| SIGNAL | FUNCTION | DESCRIPTION                                                                         | INTERNAL PULL UP / DOWN |

|--------|----------|-------------------------------------------------------------------------------------|-------------------------|

| SCK    | INPUT    | SPI Clock. Data is shifted into or out of the SPI interface using SCK               | 50K ohm pull-down       |

| CS     | INPUT    | Chip Select. Data is shifted into SI and out of SO when $\overline{CS}$ is low.     | 50K ohm pull-up         |

| SI     | INPUT    | SPI interface serial data input                                                     | 50K ohm pull-down       |

| SO     | OUTPUT   | SPI interface serial data output                                                    |                         |

| INT    | OUTPUT   | Active high. Programmable interrupt output                                          |                         |

| STAT   | OUTPUT   | Active high. Programmable status output.                                            |                         |

| TXEN   | INPUT    | Active high. Transmit Enable pin. When the TXEN pin is asserted, any message        | 100K ohm pull-down      |

|        |          | in the Transmit FIFO will be automatically loaded to the Transmit buffer and sent   |                         |

|        |          | if the bus is available. This pin is logically ORed with the TXEN and TX1M bits     |                         |

|        |          | in the CTRL1 register. When the TXEN pin is reset, messages loaded to the           |                         |

|        |          | FIFO will not be sent until TXEN or TX1M bits are set in the CTRL1 register.        |                         |

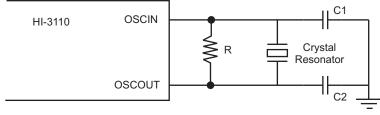

| OSCIN  | INPUT    | Crystal input. A parallel resonant crystal can be connected between OSCIN and       |                         |

|        |          | OSCOUT. If an external clock is used, it should be connected to the OSCIN pin       |                         |

|        |          | and the OSCOUT pin should be left floating. The internal oscillator should be       |                         |

|        |          | shut off by setting the OSCOFF bit in the CTRL1 register.                           |                         |

| OSCOUT | OUTPUT   | Crystal output. If an external clock is used, this pin should be left floating and  |                         |

|        |          | disabled by setting the OSCOFF bit in the CTRL1 register.                           |                         |

| GP1    | OUTPUT   | General purpose pin 1, which can be programmed to reflect the values of             |                         |

|        |          | interrupt and status flag bits.                                                     |                         |

| GP2    | OUTPUT   | General purpose pin 2, which can be programmed to reflect the values of             |                         |

|        |          | interrupt and status flag bits.                                                     |                         |

| CLKOUT | OUTPUT   | Clock output pin with programmable frequency divider.                               |                         |

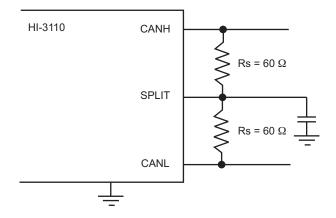

| SPLIT  | OUTPUT   | VDD/2 output bias (Powered off in Sleep Mode and when the common mode               |                         |

|        |          | bias is greater than 25V).                                                          |                         |

| CANH   | BUS I/O  | CAN bus line high.                                                                  |                         |

| CANL   | BUS I/O  | CAN bus line low.                                                                   |                         |

| MR     | INPUT    | Active High. Device Master Reset input pin. Asserting this pin resets all registers | 50K ohm pull-down       |

|        |          | and memory buffers to their default state at start-up.                              |                         |

| VDD    | POWER    | 5V supply voltage input.                                                            |                         |

| VLOGIC | POWER    | 3.3V supply voltage input. This supply is used to drive the host digital logic I/O. |                         |

|        |          | It can either be connected directly to VDD (+5V) or a +3.3V supply.                 |                         |

| GND    | POWER    | Supply voltage ground.                                                              |                         |

### **FUNCTIONAL OVERVIEW**

The HI-3110 is the first single chip product to integrate both the CAN (Controller Area Network) protocol and analog interface transceiver on a single IC. The protocol conforms to CAN version 2.0B and is compliant with ISO 11898-1:2003(E) specification. The transceiver is compliant with ISO 11898-5 specification.

Configuration options include an internal Loopback mode that does not disturb the bus, a Monitor only mode, and a Sleep mode that includes an option to either wake up automatically when data is present on the bus, or by host command. The following sections describe some of the key features.

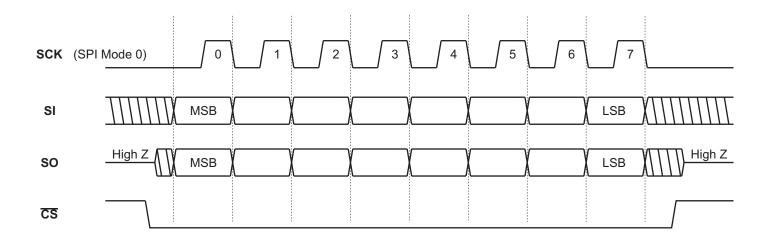

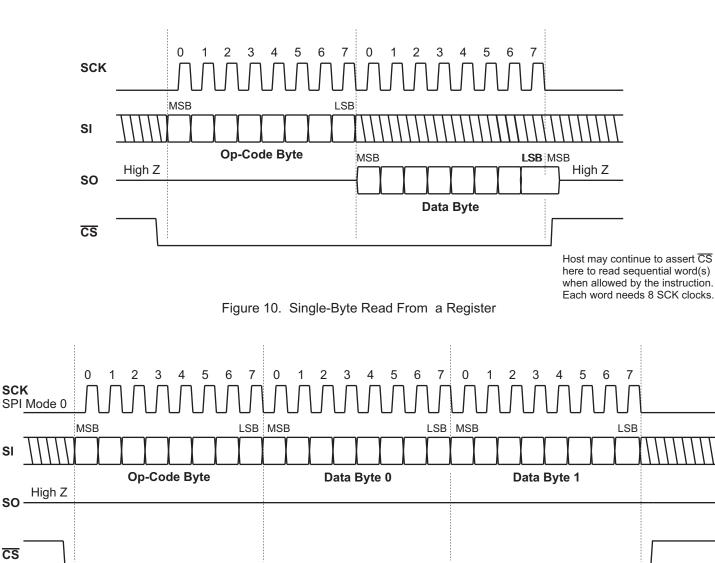

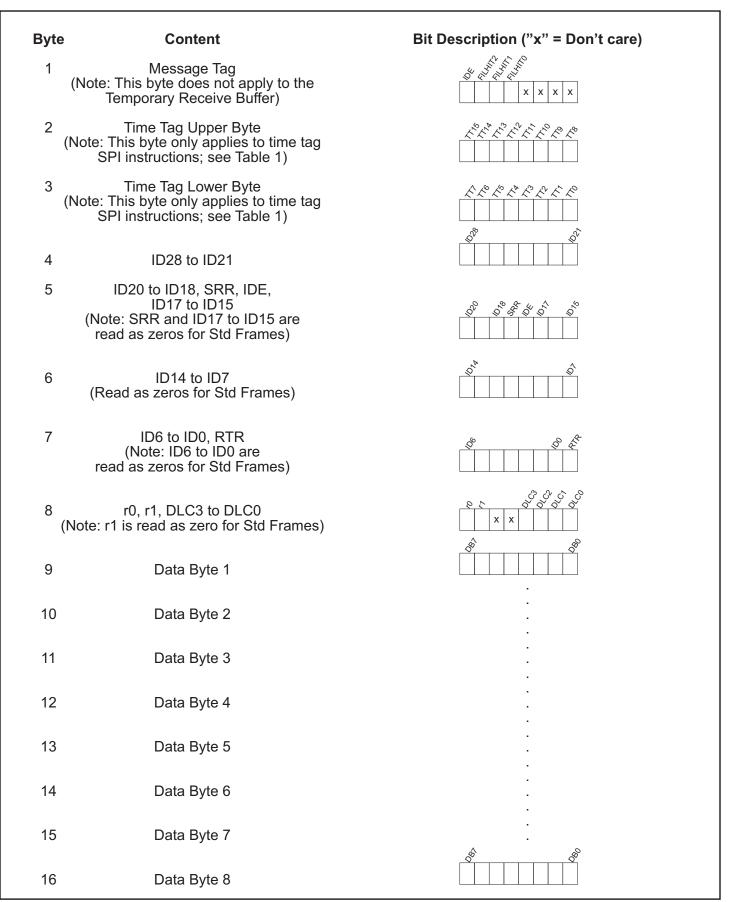

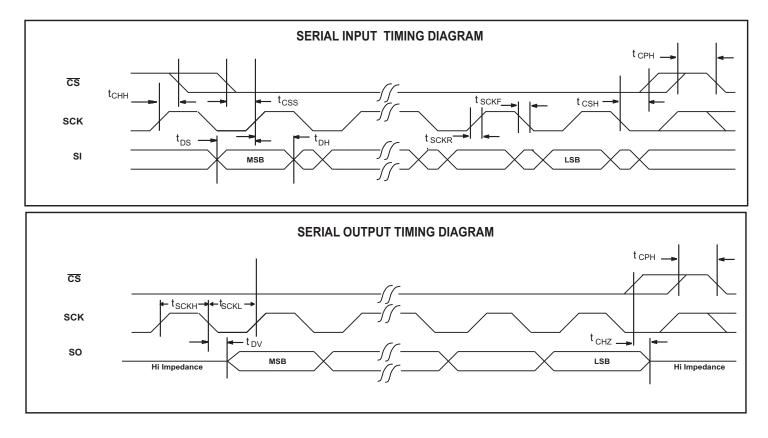

#### SPI and REGISTERS

To minimize the footprint, a 20 MHz standard four wire SPI (Serial Peripheral Interface) is provided to manage the flow of data between the host microcontroller and the HI-3110. Complete messages are loaded and retrieved with single SPI op codes. On the receive side, SPI op code options may be used to retrieve the whole message or just the data. An option to include a time tag or no time tag may also be specified. On the transmit side, each message can be assigned an identifier which allows monitoring of the Transmit History FIFO to confirm the successful completion of a transmission along with the time stamp. In addition the transmitter logic automatically assembles the message frame based on the data presented.

#### **BIT TIMING**

Bit timing is controlled with standard CAN options. These include control of the Resychronization Jump Width (SJW), Prop delay Phase Seg 1 (TSeg1), Phase Seg 2 (TSeg2), the number of samples, and the derivation of Tq from the system clock using a prescaler. The maximum bit rate is 1 MBit/sec. Upon reset, the chip automatically enters Initialization mode which allows programming of the Bit Timing before entering Normal mode.

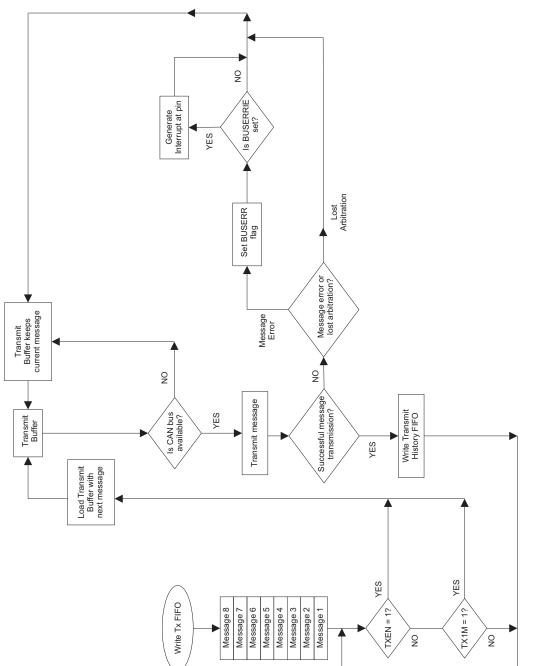

#### TRANSMITTER

The transmitter state machine automatically handles all CAN 2.0B protocol requirements. Messages for transmission are first loaded into a FIFO and transmission may start upon availability of data in the FIFO. Assertion of the TXEN pin or configuration bits in Control Register 1 allow either continuous transmission until the FIFO is empty or only one message from the FIFO at a time. One shot (no retry) transmission may also be enabled by setting the OSM and TX1M bits. SPI op codes are provided to clear the Transmit FIFO and to abort transmission.

#### RECEIVER

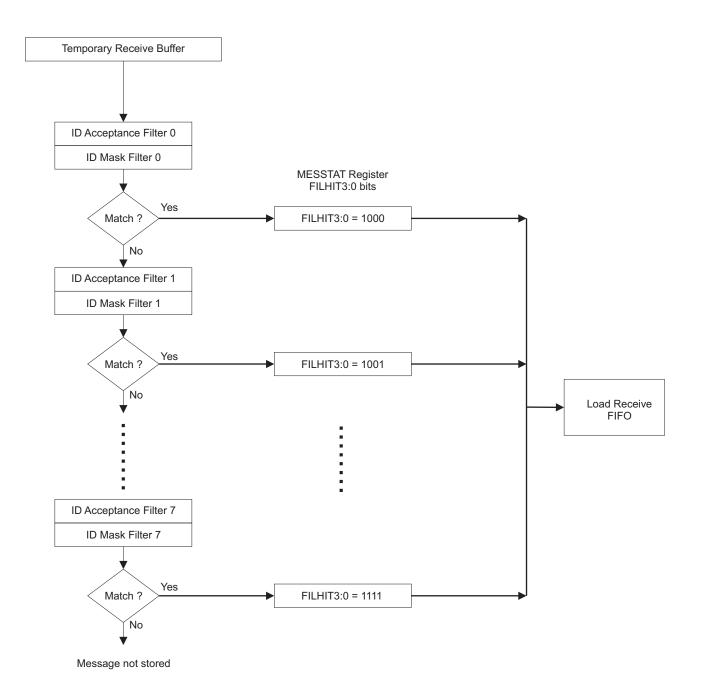

The receiver state machine automatically handles all CAN 2.0B protocol requirements. The receiver supports eight sets of filters and masks and each allows filtering of a full CAN ID (extended or not) and two bytes of data. Even when filtering is enabled, message data is always accessible as received via the Temporary Receive Buffer, and retrievable by SPI op codes 0x42 and 0x44.

If the Filter/Mask option is set (FILTON bit in Control Register 1), only messages that match one of the 8 stored data patterns are passed into the FIFO. Note that the Mask option allows certain bits of the programmed filter bits to be "don't care." If the Filter/Mask option is not set, then all valid messages are passed to the FIFO. When the FIFO is full (8 completed messages received), the next received message is not loaded in the FIFO.

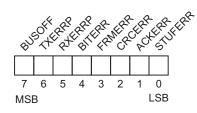

#### **ERROR CONTROL**

Errors are detected per ISO 11898-1:2003(E) and detections are counted and used by the protocol state machines. Active, Passive, and Bus Off conditions are managed per the CAN standard. A configuration bit is provided to allow automatic recovery from Bus Off.

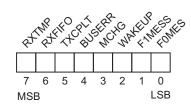

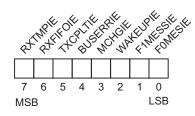

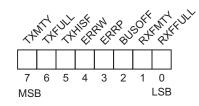

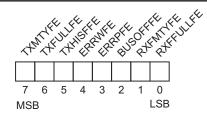

#### **STATUS and INTERRUPTS**

The Message Status Register, MESSTAT, provides information about the current state of the receiver and transmitter operation. In addition, the Interrupt Flag Register, INTF, monitors 8 operational conditions, any or all of which may be directed to the INT pin by enabling bits in the Interrupt Enable Register, INTE. Similarly, the Status Flag Register, STATF, bits reflect the status of selected FIFO and Error properties. Any or all of these conditions may be directed to the STAT pin by setting the enable bits in the Status Flag Enable Register, STATFE.

To provide additional hardwired flag options, the GP1 and GP2 pins may also be programmed to reflect any of the Interrupt or Status Flag bits.

#### **OSCILLATOR and TIME TAG**

A configuration bit allows a choice for the source of the system clock. Either the on-board crystal oscillator may be selected or an external clock may be provided at the OSCIN pin.

On product versions with the CLKOUT pin, a programmable division of the system clock is provided. The clock source for the 16 bit Time Tag Counter is derived from a separate programmable division of the system clock. SPI op codes provide for reading and resetting the Time Tag Counter.

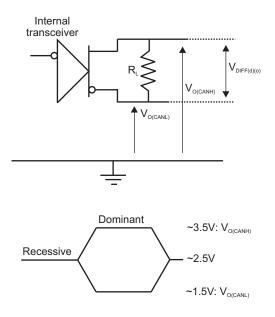

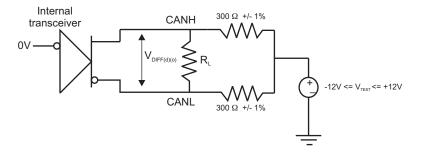

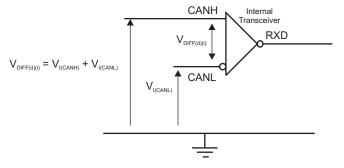

#### TRANSCEIVER

The HI-3110 contains an integrated transceiver operating from 5V and the line driver is capable of maintaining a detectable signal for bus lengths well in excess of recommended CAN 2.0B standards. The digital logic and IO can be powered from 3.3V or 5V.

#### **PROTECTION FEATURES**

The BUS and SPLIT pins are protected against ESD to over 4KV (HBM) and from shorts between -58V to +58V continuous, as specified in ISO 11898-5.

In addition, a Permanent Dominant Timeout protection is implemented by means of an independent counter monitoring the dominant transmission state and automatically shutting off the transmission if it exceeds typically 2ms.

### **MODES OF OPERATION**

The HI-3110 supports five modes of operation, namely, Initialization Mode, Normal Mode, Loopback Mode, Monitor Mode and Sleep Mode.

#### **INITIALIZATION MODE**

Initialization mode is used to configure the device before normal operation. **Bit timing registers and acceptance filters and masks can only be modified in this mode.** Initialization mode is the default mode following RESET and can also be activated by programming the MODE<2:0> bits to <1xx> in the CTRL0 register. Switching to Initialization mode resets the receiver and transmitter. During initialization mode, the error counters are held reset.

#### NORMAL MODE

Normal mode is the standard operating mode of the HI-3110. In this mode, the HI-3110 can transmit, receive and acknowledge messages from the CAN bus, handling all aspects of the CAN protocol. Normal mode is activated by programming the MODE<2:0> bits to <000> in the CTRL0 register.

#### LOOPBACK MODE

Loopback mode is used for self-test. The transceiver digital input is fed back to the receiver without being transmitted to the bus. Messages are transmitted from the transmit FIFO in the usual way and received by the receive FIFO as if they were received from a remote node on the bus.

Acceptance filters can be set up to accept or reject specific messages into the FIFO and all interrupt flags are set as

required in the usual way. While in this mode, any bus activity is ignored. Loopback is activated by programming the MODE<2:0> bits to <001> in the CTRL0 register.

#### MONITOR MODE

Monitor mode (also known as listen-only or silent mode) allows the HI-3110 to monitor all bus activity without disturbing the bus. No messages or dominant bits (such as ACK or active error frame bits) are transmitted to the bus while in this mode. Also, the error counters are reset and deactivated. Messages from the bus are received in the same way as Normal Mode and messages that are not acknowledged by another node on the bus are ignored i.e. any frame containing an error will be ignored. Acceptance filters can be set up to reject or accept specific messages into the FIFO and all interrupt flags are set as required in the usual way. Monitor mode is activated by programming the MODE<2:0> bits to <010> in the CTRL0 register.

#### SLEEP MODE

The HI-3110 can be placed in a low power sleep mode if there is no bus activity and the transmit FIFO is empty. In this mode, the internal oscillator and all analog circuitry (transceiver) are off, drawing typically less than  $20\mu$ A. Note that the SPI bus is active during sleep mode, so it is possible for the host to communicate with the HI-3110 while it is asleep (e.g. load transmit FIFOs). Sleep mode is exited by selecting an alternative mode of operation, or automatic wake up following bus activity can be enabled by setting the WAKEUP bit in the CTRL0 register - in this case a low power receiver monitors the bus for a detectable dominant bit. The device will wake up in Monitor Mode. Note that it will take a finite time for the oscillator and analog circuitry to come back on line. Since the internal oscillator takes a finite time to wake up, the message which caused the wake-up may not be stored.

Sleep mode is activated by programming the MODE<2:0> bits to <011> in the CTRL0 register. However, the actual mode change will only occur whenever the CAN bus is quiet. If the chip is transmitting, the mode change is delayed until the transmission is complete. If there is bus activity, the mode change is delayed until the receiver protocol control detects an inter-message gap.

# **CAN PROTOCOL OVERVIEW**

The HI-3110 supports Standard, Extended and Remote Frames, as defined in the CAN specification IS0 11898-1:2003(E) (also known as CAN 2.0B).

#### **BIT ENCODING**

CAN frames are encoded according to the Non-Return-To-Zero (NRZ) method with bit stuffing. NRZ means that the

generated bit level is constant during the total bit time and consecutive bits do not return to a neutral or rest condition. This means that a bit stream of "1s" or "0"s appears continuous on the bus. A logic "0" is called a dominant bit and a logic "1" is called a recessive bit.

Bit stuffing is used to ensure frequent enough transitions occur to achieve synchronization. Every time a transmitter detects five consecutive bits of the same polarity in the bit stream to be transmitted, it inserts a bit of opposite polarity into the actual transmitted bit stream.

This bit stuffing rule applies to the Start-of-Frame field, arbitration field, control field, data field and CRC sequence. The CRC delimiter, ACK field and End-Of-Frame fields are of fixed form and not stuffed (see below for definition of these fields). Furthermore, Error frames and Overload frames are also of fixed form and not stuffed.

An example of how the bits in a stuffed bit stream might look is shown below.

001010111111**0**0000**I**1100000**I**11000

0 = dominant bit, **O** = dominant stuffed bit.

1 = recessive bit, I = recessive stuffed bit.

#### **MESSAGE FRAMES**

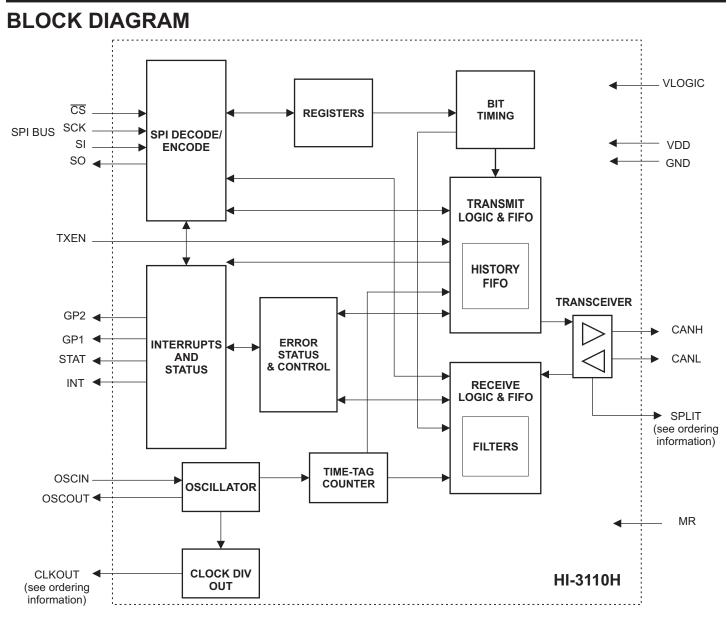

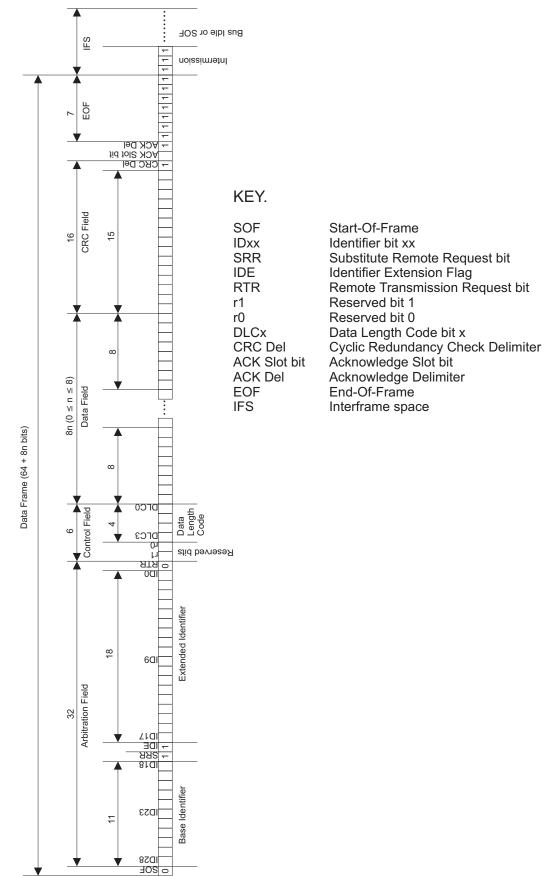

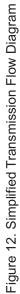

#### STANDARD DATA FRAME

The standard data frame is shown in figure 2. The frame starts with a Start-of-Frame (SOF) bit. This is a dominant bit that identifies the start of the data frame on the bus.

The SOF is followed by the 12-bit arbitration field. The arbitration field consists of an 11-bit identifer, ID28 - ID18, and the Remote Transmission Request (RTR) bit. The RTR bit is used to distinguish between a data frame (RTR bit dominant, logic 0) and a remote frame (RTR bit recessive, logic 1).

Following the arbitration field is the 6-bit control field. The first bit of the control field is the Identifier Extension flag bit (IDE). This is used to distinguish between standard and extended identifiers and must be dominant (logic 0) for standard data frames. The next bit, r0, is specified by the CAN protocol as a reserved bit for future expansion. This bit must be transmitted dominant, but receivers must be capable of receiving either a dominant or recessive bit. The final 4 bits of the control field make up the data length code (DLC). The binary value of this 4-bit field specifies the number of data bytes in the data payload (0 - 8 bytes). **Note:** All binary combinations greater than or equal to <1 0 0 0> specify 8 bytes of data.

After the control field is the data field, which contains a data payload equal to the number of bytes specified by the DLC (see note above).

The data field is followed by the 16-bit Cyclic Redundancy Check (CRC) field. This is used to check transmission errors by computing a 15-bit CRC sequence from the previous bit stream (SOF, arbitration field, control field and data field, excluding stuff bits). The last bit in the CRC field is the CRC delimiter bit (always recessive).

After the CRC field is the Acknowledge Field (ACK Field). The first bit is the ACK Slot bit. A transmitting node sends a recessive bit (logic 1) during the ACK slot. Any node which receives the message error-free acknowledges the reception by placing a dominant bit (logic 0) in the ACK slot, over-writing the recessive bit of the transmitter. The final bit in the ACK field is a recessive ACK delimiter bit. Therefore, the dominant ACK slot bit is surrounded on each side by a recessive bit.

Each data frame is delimited by an End-Of-Frame field (EOF). The EOF consists of seven recessive bits.

Following the EOF, there is a gap to the next frame called the Interframe Space (IFS). The IFS consists of two bit fields, Intermission and Bus-Idle. The Intermission consists of three recessive bits, however the following notes apply:

a) detection of a dominant bit on the bus at the third slot is interpreted as a SOF,

b) detection of a dominant bit in either the first or second slots results in generation of an overload frame (see below).

The bus idle period is of arbitrary length and consists of recessive bits. A dominant bit detected during this period is interpreted as a SOF.

#### EXTENDED DATA FRAME

The extended data frame is shown in figure 3. In this frame format, SOF is followed by a 32-bit arbitration field consisting of a 29-bit identifier, ID28 - ID0. The first 11 most significant bits of the ID are know as the base identifier. This is followed by the Substitute Remote Request (SRR) bit, which is defined as recessive. Following the SRR bit is the IDE bit, which is defined as recessive for extended data frames. Note that the SRR bit is in the same slot as the RTR bit of the standard frame and the IDE bits are also in corresponding slots. This means if standard and extended identifier data frames with identical base identifiers are transmitted simultaneously, the standard identifier data frame will win arbitration (see Bitwise Arbitration section below).

The SRR and IDE bits are followed by the remaining 18 bits of the identifier (extended ID) and the last bit of the arbitration field is the RTR bit. The RTR bit has the same function as in the standard frame format.

Following the arbitration field is the 6-bit control field. The first two bits, r1 and r0, are specified by the CAN protocol as reserved bits for future expansion. Both these bits must be transmitted dominant, but receivers must be able to receive all combinations of dominant or recessive bits. The final 4 bits of the control field is the data length code (DLC). The

binary value of this 4-bit field specifies the number of data bytes in the data payload (0 - 8 bytes). **Note:** All binary combinations greater than or equal to <1 0 0 0> specify 8 bytes of data.

The remaining fields of the extended data frame (Data field, CRC field, acknowledge field, EOF field and IFS field) are constructed in the same way as the standard frame format.

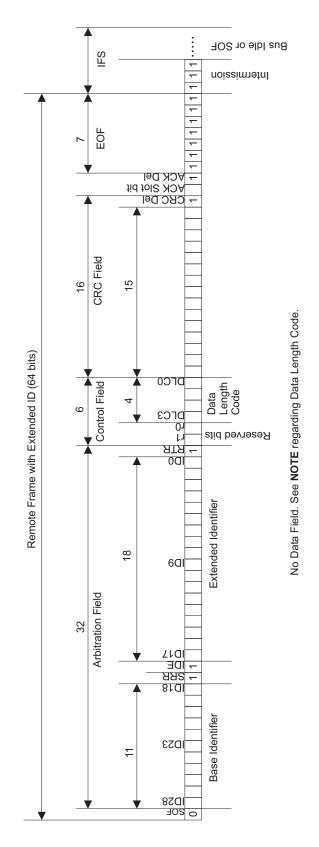

#### **REMOTE FRAME**

The remote frame is shown in figure 4. The function of remote frames is to allow a receiver which periodically receives certain types of data to request that data from the transmitting source. The identifier of the remote frame must be identical to the identifier of the requested transmitting node's data frame and the data length code (DLC) should be equal to the DLC of the requested data. **Simultaneous transmission of remote frames with the same identifier and different DLCs will lead to unresolvable collisions on the bus.** For this reason, ARINC 825 strongly discourages the use of remote frames.

The format of a remote frame is identical to the format of the corresponding data frame except the remote frame has no data payload. Remote frames and data frames are distinguished by a recessive RTR bit in the remote frame. This means if a receiver sends a remote frame and the sending node transmits at the same time, the sending node (with a dominant RTR bit) will win arbitration and the requesting node will receive the desired data immediately.

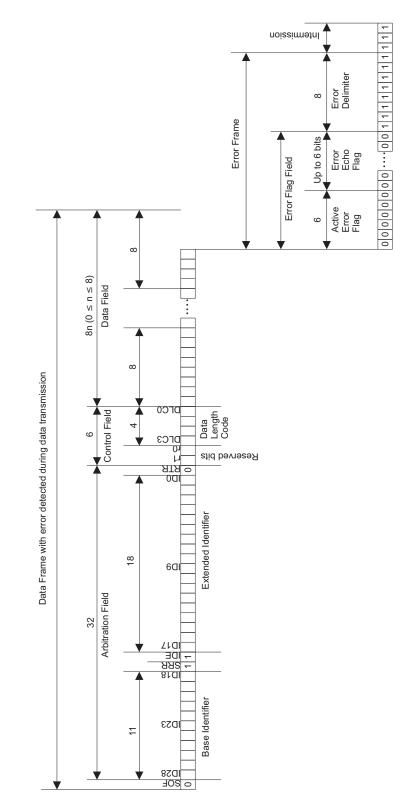

#### **ERROR FRAME**

The error frame is shown in figure 5. Any node detecting an error generates an error frame. The error frame consists of two fields, the error flag field and the error delimiter. The type of error flag field depends on the error status of the node, error-active or error-passive (see below). An error-active node generates an active error flag and an error-passive node generates a passive error flag.

Active Error Flag: An active error flag consists of 6 consecutive dominant bits. This condition violates the rule of bit-stuffing and causes all other nodes on the bus to generate error flags, known as echo error flags. Therefore, the error flag field will consist of the superposition of different error flags sent by individual nodes, resulting in a minimum of 6 and maximum of 12 consecutive dominant bits. The error flag field is followed by the error delimiter, consisting of 8 recessive bits.

**Passive Error Flag:** A passive error flag consists of 6 recessive bits. This is followed by the 8 recessive bits of the error delimiter. Therefore, an error frame sent by an error-passive node consists of 14 consecutive recessive bits. Since this will not disturb the bus, a transmitting node will continue to transmit unless it detects the error itself, or another error-active node detects the error.

cannot prevail over any other activity on the bus. Therefore, it must wait for 6 consecutive bits of equal polarity before completing the error flag. If the passive error flag is generated by a transmitter, the bit stuffing rule is violated and it will cause other nodes to generate error flags. Two exceptions to this rule are

a) the passive error flag starts during arbitration and another node prevails and begins transmitting, and

b) the error flag starts less than 6 bits before the end of the CRC sequence and the last bits of the CRC sequence all happen to be recessive.

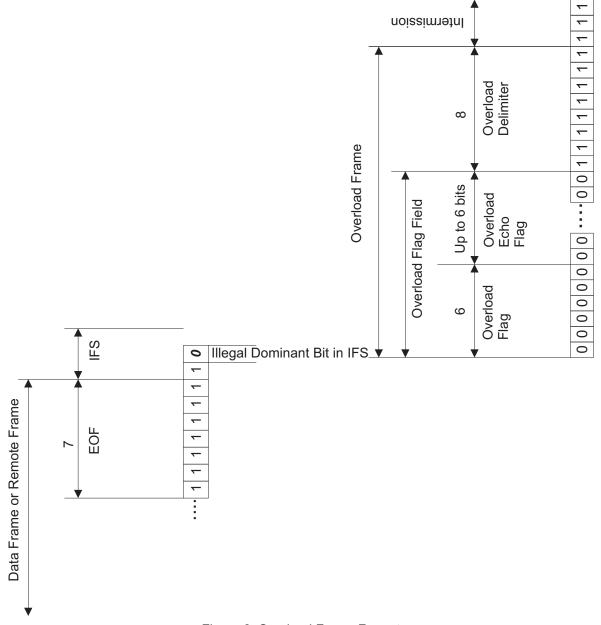

#### **OVERLOAD FRAME**

The overload frame is shown in figure 6. It has the same format as the active error frame, consisting of an overload flag field and an overload delimiter. The overload flag consists of 6 consecutive dominant bits. This condition violates the rule of bit-stuffing and causes all other nodes on the bus to generate echo flags, similar to the active error flag echos. Therefore, the overload flag field will consist of the superposition of different overload flags sent by individual nodes, resulting in a minimum of 6 and maximum of 12 consecutive dominant bits. The overload flag is followed by the overload delimiter, consisting of 8 recessive bits.

An overload frame, unlike an error frame, can only be generated during the interframe space. There are two types of overload frame:

#### 1) Reactive Overload Frame, resulting from

a) detection of a dominant bit during the first or second bit of intermission,

b) detection of a dominant bit at the last (seventh) bit of EOF in received frames, or

c) detection of a dominant bit at the last (eighth) bit of an error delimiter or overload delimiter.

The reactive overload frame is started one bit after detecting any of the above dominant bit conditions.

**2) Requested Overload Frame.** A node which is unable to begin reception of the next message due to internal conditions may request a delay by transmitting a maximum of two consecutive overload frames. The requested overload frame must be started at the first bit of an expected intermission.

**Note 1):** The HI-3110 will never initiate an overload frame unless reacting to one of the conditions in case 1) above. **Note 2):** Initiation of overload frames is prohibited by ARINC 825 since they increase the network loading.

Notes: If the passive error flag is generated by a receiver, it

# **Standard Data Frame**

### **Extended Data Frame**

Figure 3. Extended Frame Format.

# **Remote Frame**

Figure 4. Remote Frame Format (Extended Identifier).

# **Error Frame**

Figure 5. Error Frame Format.

# **Overload Frame**

Figure 6. Overload Frame Format

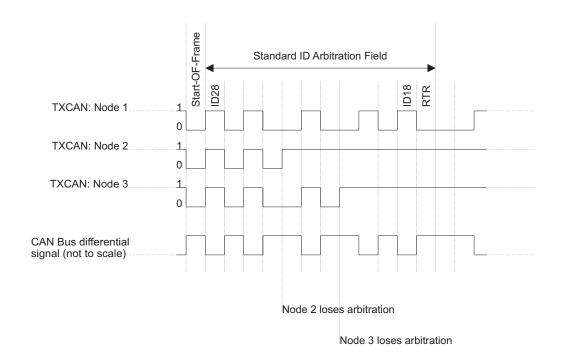

#### **BIT WISE ARBITRATION**

The CAN standard resolves data contention on the bus using a scheme called Carrier Sense Multiple Access/Collision Detection-Carrier Resolution (CSMA/CD-CR).

**Carrier Sense:** Each node waits for a period without bus activity (bus idle state) before attempting transmission.

**Multiple Access:** Every node on the bus has equal access to the bus for transmitting.

**Collision Detection:** Collisions occur if two nodes attempt to transmit at the same time.

**Collision Resolution:** Collisions are resolved by bitwise arbitration. Highest priority messages (lowest binary identifiers) are sent first without delay and lower-priority messages are automatically re-transmitted later. A dominant bit (logic 0) has priority over a recessive bit (logic 1).

Bitwise arbitration works by comparing each node's transmitted data bit by bit. All nodes are synchronized by adjusting individual bit times as a function of bit time quanta (see section on bit timing). Synchronization takes place on recessive to dominant edges. A Hard Synchronization at the start of each frame and subsequent re-synchronizations during a message frame ensures corresponding bits match in time during a given transmission cycle. When a node transmits a recessive bit on the bus, but detects a dominant bit on it's receiver, it realizes arbitration is lost and it immediately ceases transmission and becomes a receiver. It will then wait for the next bus idle state and attempt to retransmit. Eventually, lower priority messages will gain access to the bus. Figure 7 shows an example of how this works for a frame with a standard identifier.

Figure 7. Bitwise Arbitration.

### **BIT TIMING**

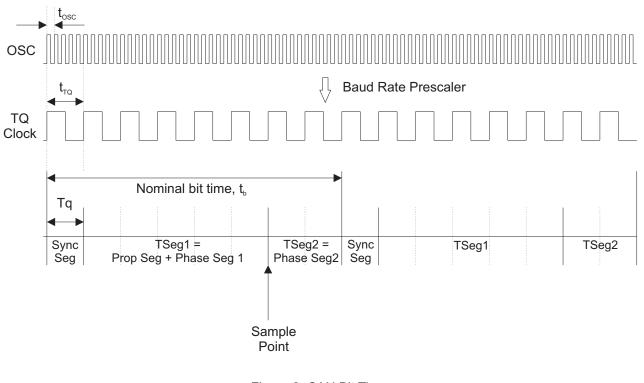

The CAN protocol supports a broad range of bit rates, from a few kHz up to 1MHz (**Note:** the minimum bit rate of the HI-3110 is limited to 40kHz by the permanent dominant timeout protection of the transceiver). Every node on the network has it's own clock generator (typically a quartz oscillator), however the bit rate must obviously be the same for every node on the bus. Therefore, each CAN node must be configurable to generate the nominal bit rate as a function of it's own oscillator frequency,  $f_{osc}$ . This is done by generating a time quanta (TQ) clock, whose period  $t_{\tau \alpha}$  is related to the oscillator frequency by a Baud Rate Prescaler value, BRP as follows:

$$t_{TQ} = 2 \cdot BRP/f_{OSC}$$

(1)

The TQ clock is used to construct the bit time in terms of time quanta, such that one time quantum, Tq, equals one TQ clock period,  $t_{ro}$ , as shown in figure 8 below.

The CAN system nominal bit rate (BR) is defined in terms of the nominal bit time,  $t_{o}$ , as

$$BR = 1/t_{\rm b}$$

(2)

Therefore, the nominal bit rate is related to the TQ clock period by the following relationship

BR =  $1/(t_{TQ} x \text{ (number of time quanta per bit)})$  (3)

The CAN standard divides the bit time into four segments, namely, synchronization segment (Sync Seg), propagation time segment (Prop Seg), phase buffer segment 1 (Phase Seg1) and phase buffer segment 2 (Phase Seg2). This is illustrated in figure 8. The HI-3110 fixes the Sync Seg at 1Tq. Prop Seg and Phase Seg1 are treated as one time segment, TSeg1, which is programmable from 2Tq to 16Tq. Phase Seg2 is a second time segment, TSeg2, which is programmable from 2Tq to 8Tq (**Note:** Not all combinations are valid, see below for examples).

#### Synchronization Segment (Sync Seg)

The Sync Seg is the first segment of the bit time and is used to synchronize the various nodes on the bus. A bit edge is expected to occur within the Sync Seg.

#### Propagation Time Segment (Prog Seg)

The Prog Seg is used to compensate for physical delays on the bus, which include signal propagation delay time on the bus and internal node delay times. For two nodes A and B communicating on the bus, Prog Seg must be greater than or equal to the sum of both nodes internal delays plus twice the bus line propagation delay between the two nodes.

Figure 8. CAN Bit Time

#### Phase Buffer Segment 1 and Phase Buffer Segment 2 (Phase Seg1 and Phase Seg2)

The phase buffer segments are used to compensate for phase errors on the bus. Phase Seg1 can be lengthened or Phase Seg2 can be shortened duringthe re-synchronization bit period automatically by the HI-3110 so that the bit time can be adjusted to account for phase errors. The upper limit by which the lengthening ( or shortening) can occur is set by the **re-synchronization jump width (SJW)**, explained in more detail below.

#### **Sample Point**

The sample point is the point in the bit time at which the bit logic level is interpreted. It is located at the end of Phase Seg1. The HI-3110 also allows three sample points to be taken. In this case, two other sample points are taken prior to the end of Phase Seg1 (at one-half TQ intervals) and the value of the bit is determined by a majority decision. Three sample points are typically only used at low bit rates. **Note:** ARINC 825 states that there shall be only one sample per bit, taken at the end of Phase Seg1.

The time required for the logic to determine the bit level of a sampled bit is known as the **information processing time (IPT)**. According to the standard, IPT can be up to 2Tq. Since Phase Seg2 occurs after the sample point, Phase Seg2 must be greater than or equal to the worst case IPT (2Tq).

#### Phase Errors (e)

If a bit edge occurs within the Sync Seg as expected, there is no phase error (e = 0). However, if an edge occurs outside Sync Seg, a phase error is deemed to have occurred. If the edge occurs after Sync Seg (edge occurs "late"), the phase error is positive (e > 0), whereas if the edge occurs before Sync Seg (edge occurs "early"), the phase error is negative (e < 0).

#### Synchronization

Synchronization is carried out only on recessive-todominant bit edges and is used to ensure the bit times of all nodes on the bus are synchronized. This is necessary for arbitration and message acknowledgment to function properly. Only one synchronization can occur per bit time.

**Hard synchronization** forces the bit edge to lie within the Sync Seg, regardless of the phase error. Hard synchronization only occurs on reception of the start of a

frame.

**Re-synchronization** results in the shortening or lengthening of the bit time such that the position of the sample point is shifted with respect to the edge causing the re-synchronization. **For e > 0**, Phase Seg 1 is lengthened by the magnitude of the phase error, up to a maximum of SJW. **For e < 0**, Phase Seg 2 is shortened by the magnitude of the phase error, up to a maximum of SJW.

#### **Examples**

#### 1) CAN bit rate (BR) = 125kHz, $f_{osc} = 12$ MHz.

Assume sample point (at end of TSeg1) will occur at 75% of bit time. Hence, for Sync Seg = 1Tq, TSeg1 = 5 Tq and TSeg2 = 2Tq. Therefore, total bit time will be 8Tq. Chose SJW = 1Tq.

For 125kHz, the bit time needs to be  $1/125kHz = 8\mu s$ . Hence,  $1Tq = 1\mu s$ . Using equation (1) => BRP = 6.

#### 2) CAN bit rate (BR) = 1MHz, $f_{osc}$ = 32MHz.

Assume sample point (at end of TSeg1) will occur at 75% of bit time. For Sync Seg = 1Tq, then TSeg1 = 11Tq and TSeg2 = 4Tq. Therefore, total bit time will be 16Tq. Chose SJW = 1Tq.

For 1MHz, the bit time needs to be 1/1MHz = 1µs. Hence, 1Tq = 62.5ns. Using equation (1) => BRP = 1.

**Note:** Choosing the sample point at 75% of the bit time is a requirement of ARINC 825. The oscillator frequency must be chosen such that a valid value of BRP (integer) can generate the TQ clock (e.g. in example 2 above, using a lower oscillator frequency than 32MHz results in BRP < 1).

### REGISTERS

This section describes the HI-3110 registers. All register bits are active high. Unless otherwise indicated, all registers are reset in software to the logic zero condition after Master Reset. For all registers, bit 7 is the most significant:

| REGISTER | R/W | DESCRIPTION                            | SPI WRITE | SPI READ |

|----------|-----|----------------------------------------|-----------|----------|

|          |     |                                        | OP-CODE   | OP-CODE  |

|          |     |                                        |           |          |

| CTRL0    | R/W | Control Register 0                     | 0x14      | 0xD2     |

| CTRL1    | R/W | Control Register 1                     | 0x16      | 0xD4     |

| BTR0     | R/W | Bit Timing Register 0                  | 0x18      | 0xD6     |

| BTR1     | R/W | Bit Timing Register 1                  | 0x1A      | 0xD8     |

| TEC      | R/W | Transmit Error Counter Register        | 0x26      | 0xEC     |

| REC      | R/W | Receive Error Counter Register         | 0x24      | 0xEA     |

| MESSTAT  | R   | Message Status Register                | N/A       | 0xDA     |

| ERR      | R   | Error Register                         | N/A       | 0xDC     |

| INTF     | R   | Interrupt Flag Register                | N/A       | 0xDE     |

| INTE     | R/W | Interrupt Enable Register              | 0x1C      | OxE4     |

| STATF    | R   | Status Flag Register                   | N/A       | 0xE2     |

| STATFE   | R/W | Status Flag Enable Register            | 0x1E      | 0xE6     |

| GPINE    | R/W | General Purpose Pins Enable Register   | 0x22      | 0xE8     |

| TIMERUB  | R   | Free-Running Timer Upper Byte Register | N/A       | 0xFA*    |

| TIMERLB  | R   | Free-Running Timer Lower Byte Register | N/A       | 0xFA*    |

**Note:** Free-running counter registers, TIMERUB:TIMERLB are read with a single SPI Op-code (0xFA) as a 16bit value in two SPI data bytes.

#### **Power-On-Reset**

Following power-on, the HI-3110 will automatically perform a Master Reset and return all registers to the default state. Following reset, the device will default to Initialization Mode to allow programming of Control and Bit Timing Registers (see following sections).

|            | Write, SPI Op<br>Read, SPI Op |            |                |                                                                                              | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|-------------------------------|------------|----------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>Bit</u> | <u>Name</u>                   | <u>R/W</u> | <u>Default</u> | Description                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7-5        | MODE2:0                       | R/W        | 1,0,0          | Mode select bits <2:0>.<br>These bits select the mod                                         | e of operation as follows.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|            |                               |            |                | 000: Normal Mode.<br>001: Loopback Mode.                                                     | Normal CAN operation.<br>The transceiver digital input is fed back to the receiver without<br>disturbing the bus. This mode can be used for test purposes,                                                                                                                                                                                                                                                                                                                                                                                     |

|            |                               |            |                | 010: Monitor Mode.                                                                           | allowing the HI-3110 to receive its own messages.<br>The HI-3110 can be set up to monitor bus activity without<br>transmitting to the bus (no ACK bits or error frames are sent in this<br>mode). Receive filters can be programmed in Initialization Mode to                                                                                                                                                                                                                                                                                  |

|            |                               |            |                | 011: Sleep Mode.                                                                             | buffer selected messages.<br>The HI-3110 can be placed in a low power sleep mode if there is no<br>bus activity and the transmit FIFO is empty. Sleep mode is exited<br>by selecting an alternative mode of operation, or automatic wake<br>up following bus activity can be enabled by setting the WAKEUP                                                                                                                                                                                                                                     |

|            |                               |            |                | 1xx: Initialization Mode.                                                                    | bit. The device will wake up in Monitor mode.<br>The device <b>must</b> be in this mode for bit timing and filter set-up.<br>This is the default following reset. The host exits initialization<br>mode by selecting an alternative mode of operation.                                                                                                                                                                                                                                                                                         |

| 4          | WAKEUP                        | R/W        | 0              | Wake-Up Enable.<br>When this bit is set, the HI<br>when it detects activity on<br>1 =<br>0 = | -3110 will automatically wake up from Sleep Mode to Monitor Mode<br>the bus.<br>Automatic wake-up enabled. When the device wakes up from<br>Sleep Mode, the WAKEUP bit will be set in the Interrupt Flag<br>Register, INTF. A hardware interrupt can be generated at the INT<br>pin by setting the WAKEUPIE bit in the Interrupt Enable Register.<br>Automatic wake-up not enabled. In this case, wake-up from Sleep<br>Mode is initiated by the host by selecting another mode of<br>operation. When WAKEUP = 0, all bus activity is ignored. |

| 3          | RESET                         | R/W        | 0              | written with $< 1 \times \times 0 \times \times x$                                           | 3110 reset to occur. Following reset, the CTRL0 register should be<br>>. This will clear the RESET bit and also avoid unpredictable<br>part is programmed to Initialization Mode, ready for set-up.                                                                                                                                                                                                                                                                                                                                            |

|            |                               |            |                | Areset may also be perfor<br>1 =<br>0 =                                                      | med by setting the MR pin or issuing the "MR" SPI command, 0x56.<br>Master Reset (same as MR pin = 1).<br>Normal Operation (same as MR pin = 0).                                                                                                                                                                                                                                                                                                                                                                                               |

| 2          | BOR                           | R/W        | 0              | consecutive recessive bit                                                                    | natic bus-off recovery is initiated following 128 occurrences of 11<br>s on the bus. The HI-3110 will become error-active with both its error<br>esume operation in Normal Mode.<br>Automatic bus-off recovery.<br>The host is responsible for bus-off recovery (default).                                                                                                                                                                                                                                                                     |

| 1-0        | TDIV1:0                       | R/W        | 0,0            | Time Tag Clock Division B<br>00 =<br>01 =<br>10 =<br>11 =                                    | its <1:0>. See TIMERUB and TIMERLB register descriptions.<br>No division (counts every bit clock).<br>Divide by 2 (counts every 2 bit clocks).<br>Divide by 4 (counts every 4 bit clocks).<br>Divide by 8 (counts every 8 bit clocks).                                                                                                                                                                                                                                                                                                         |

| (\         | ΟΝΤROL RE<br>Write, SPI Οβ<br>Read, SPI Οβ | o-code     | 0x16)   | <b>RL1</b><br>$ \begin{array}{c}                                     $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------|--------------------------------------------|------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>Bit</u> | <u>Name</u>                                | <u>R/W</u> | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7          | TXEN                                       | R/W        | 0       | Transmission Enable.<br>This bit is logically ORed with the TXEN pin. When this bit is asserted, each message in the<br>FIFO will be sequentially loaded to the transmit buffer and sent if the bus is available. If this bit<br>is not set, a transmission can be enabled by either the TXEN pin or the TX1M bit. If the TXEN<br>pin is pulled low during a transmission, the current message being transmitted will be<br>completed. Any additional messages in the FIFO will not be transmitted.<br>1 = Enable transmission and send any messages in FIFO (until<br>empty if TXEN is held set).<br>0 = Wait for transmission enable or TX1M bit set before sending next<br>message in FIFO. |

| 6          | TX1M                                       | R/W        | 0       | Enable transmission of only next message.<br>This bit is applicable only if TXEN = 0. It is reset automatically upon completion of a successful<br>transmission or by initiation of transmission if the OSM bit is set.<br>1 = Enable transmission of only next message in FIFO when TXEN = 0.<br>0 = Wait for transmission enable or TX1M bit set before sending next<br>message in FIFO.                                                                                                                                                                                                                                                                                                     |

| 5          | OSM                                        | R/W        | 0       | One-Shot Mode Enable.<br>OSM is intended to be used ONLY with the TX1M bit. If OSM is enabled and TX1M is set, the<br>controller transmits only once and does not attempt re-transmission upon loss of arbitration or<br>error. This feature is necessary to support the implementation of fixed time slots in the<br>Time-Triggered CAN standard (TTCAN). Note: <b>Un-transmitted messages will remain in</b><br><b>the FIFO.</b> If a new message is required on the next transmission cycle, the user must<br>first clear the FIFO with SPI command 0x54 and then reload the new message.                                                                                                   |

|            |                                            |            |         | <ul> <li>1 = Enable one-shot mode.</li> <li>0 = Messages will re-transmit according to CAN protocol.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4          | FILTON                                     | R/W        | 0       | Filter on enable.<br>This bit is set to turn on the HI-3110 CAN ID filtering mechanism. The default after reset is<br>FILTON = 0, meaning filtering is turned off and every valid CAN message is accepted into the<br>receive FIFO. Note: The device must be in initialization mode in order to program the<br>acceptance filters and masks.<br>1 = Enable CAN ID filtering.<br>0 = No CAN ID filtering (every valid message accepted into<br>receive FIFO).                                                                                                                                                                                                                                   |

| 3          | OSCOFF                                     | R/W        | 0       | Oscillator off. This bit should be set to a one if an external clock is used. In this case the external clock is connected to the OSCIN pin and OSCOUT should be left floating.<br>1 = Shuts off external OSCOUT pin.<br>0 = OSCOUT pin enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2          | Not used                                   | R/W        | 0       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1-0        | CLKDIV1:0                                  | R/W        | 00      | External CLKOUT division bits <1:0><br>00: Divide by 1.<br>01: Divide by 2.<br>10: Divide by 4.<br>11: Divide by 8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| BIT TIMING REGISTER 0: E<br>(Write, SPI Op-code 0x18)<br>(Read, SPI Op-code 0xD6) | STRO<br>$S^{N^{\circ}}S^{N^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R^{\circ}}S^{R$ |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BTR0 defines the value of the Re-s<br>anytime and written only in init mode       | ynchronization Jump Width (SJW) and the Baud Rate Prescaler (BRP). This register can be read $e$ (MODE<2:0> bits set to <1xx> in the CTRL0 register).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Bit Name R/W Defaul                                                               | t Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7-6 SJW1:0 R/W 0                                                                  | Re-synchronization Jump Width bits <1:0>.<br>These bits are used to compensate for phase shifts between different clock oscillators on the<br>bus. They define the maximum number of time quanta (Tq) a bit can be shortened or<br>lengthened to allow a node achieve re-synchronization to the edge of an incoming signal.<br>Note that one time quantum (Tq) is the single unit of time within a bit time (see Bit Timing<br>section).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                   | SJW bits <1:0><br>00: SJW = 1 Tq<br>01: SJW = 2 Tq<br>10: SJW = 3 Tq<br>11: SJW = 4 Tq                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                   | Note: ARINC 825 states that the Re-synchronization Jump Width shall be 1 Tq $$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |