# UNISONIC TECHNOLOGIES CO., LTD

LXXLD50 **CMOS IC**

## 0.8V REFERENCE ULTRA LOW DROPOUT LINEAR REGULATOR

#### DESCRIPTION

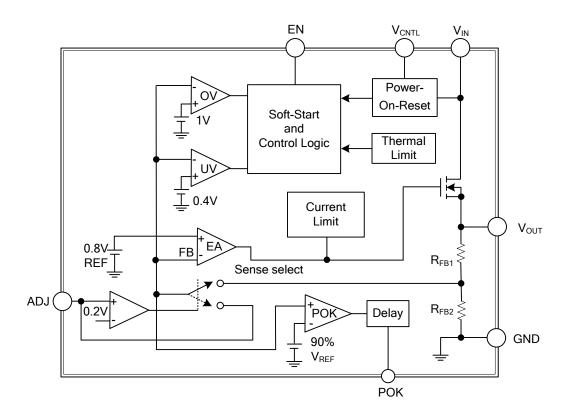

The UTC LXXLD50 is a 5A ultra low dropout linear regulator providing designers with well supply voltage for applications of NB and front-side-bus termination on motherboards.

A control voltage for the circuitry and a main supply voltage for power conversion are needed as supply voltages to reduce power dissipation and provide extremely low dropout.

The UTC LXXLD50 contains some function circuits. A Power-On-Reset (POR) circuit monitors both supply voltages to prevent undesired operations. A thermal shutdown and current limit circuits prevent this device from being damaged due to thermal and current over-loads. A POK indicates the output status with a pre-set time delay. It can control other converter for power sequence. The UTC LXXLD50 can be

enabled by other power system. Pulling and holding the EN pin below 0.3V shuts off the output.

The UTC LXXLD50 is ideal for applications, such as front side bus VTT (1.2V/5A), note book PC applications, and motherboard applications.

#### **FEATURES**

- \* Low Dropout V<sub>D</sub>=0.2V(Typ.)@ I<sub>OUT</sub>=5A

- \* Low ESR Output Capacitor

- \* V<sub>RFF</sub>=0.8V

- \* High Output Accuracy: ±1.5% Over Line, Load and Temperature

- \* Fast Transient Response

- \* 1.2V, 1.5V, 1.8V, 2.5V Output Options by Connecting ADJ to GND and Output Voltage can be Adjusted by External Resistors

- \* Power-On-Reset Monitoring both Supply Voltages (VCNTL and VIN Pins)

- \* Protection function: Internal Soft-Start

**Current-Limit Protection** Under-Voltage Protection

Thermal Shutdown with Hysteresis

Over-Voltage Protection

- \* Power-OK Output with a Delay Time

- \* Shutdown for Standby or Suspend Mode

- \* Lead Free Available (RoHS Compliant)

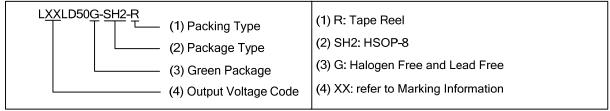

#### ORDERING INFORMATION

| Ordering Number | Package | Packing   |

|-----------------|---------|-----------|

| LXXLD50G-SH2-R  | HSOP-8  | Tape Reel |

Note: XX: Output Voltage, refer to Marking Information.

www.unisonic.com.tw 1 of 11

## MARKING INFORMATION

| PACKAGE | VOLTAGE CODE         | MARKING                                                           |

|---------|----------------------|-------------------------------------------------------------------|

| HSOP-8  | 25 : 2.5V<br>AD: ADJ | Voltage Code  Voltage Code  LXXLD50G  LXXLD50G  Lot Code  1 2 3 4 |

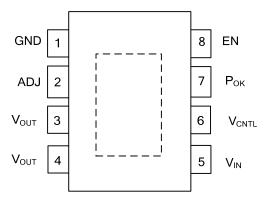

## ■ PIN CONFIGURATION

## ■ PIN DESCRIPTION

| PIN NO. | PIN NAME          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | GND               | Ground pin of the circuitry. All voltage levels are measured with respect to this pin.                                                                                                                                                                                                                                                                                                                                                                    |

| 2       | ADJ               | This pin, when grounded, sets the output voltage by the internal feedback resistors; If external feedback resistors are used, the output voltage will be $V_{OUT}$ =0.8· (1+R1/R2) (V) where R1 is connected from VOUT to ADJ with Kelvin sensing and R2 is connected from ADJ to GND. A bypass capacitor may be connected with R1in parallel to improve load transient response. The recommended R2 and R1 are in the range of $100$ ~ $10$ k $\Omega$ . |

| 3       | V <sub>OUT</sub>  | Output of the regulator. Please connect Pin 3 and 4 together using wide tracks. It is                                                                                                                                                                                                                                                                                                                                                                     |

| 4       | V <sub>OUT</sub>  | necessary to connect a output capacitor with this pin for closed-loop compensation and improving transient responses.                                                                                                                                                                                                                                                                                                                                     |

| 5       | V <sub>IN</sub>   | Main supply input pins for power conversions. The Exposed Pad provide a very low impedance input path for the main supply voltage. Please tie the Exposed Pad and VIN Pin (Pin 8) together to reduce the dropout voltage. The voltage at this pins is monitored for Power-On Reset purpose.                                                                                                                                                               |

| 6       | V <sub>CNTL</sub> | Power input pin of the control circuitry. Connecting this pin to a +5V (recommended) supply voltage provides the bias for the control circuitry. The voltage at this pin is monitored for Power-On Reset purpose.                                                                                                                                                                                                                                         |

| 7       | Рок               | Power-OK signal output pin. This pin is an open-drain output used to indicate status of output voltage by sensing FB voltage. This pin is pulled low when the rising FB voltage is not above the VPOK threshold or the falling FB voltage is below the VPNOK threshold, indicating the output is not OK.                                                                                                                                                  |

| 8       | EN                | Enable control pin. Pulling and holding this pin below 0.3V shuts down the output.  When re-enabled, the IC undergoes a new soft-start cycle. Left this pin open, an internal current source 10mA pulls this pin up to V <sub>CNTL</sub> voltage, enabling the regulator.                                                                                                                                                                                 |

## ■ BLOCK DIAGRAM

## ABSOLUTE MAXIMUM RATING

| PARAMETER                                       | SYMBOL            | RATINGS                       | UNIT     |

|-------------------------------------------------|-------------------|-------------------------------|----------|

| VCNTL Supply Voltage (V <sub>CNTL</sub> to GND) | $V_{CNTL}$        | -0.3 ~ 7                      | V        |

| VIN Supply Voltage (V <sub>IN</sub> to GND)     | $V_{IN}$          | -0.3 ~ 3.3                    | V        |

| EN and FB to GND                                | $V_{I/O}$         | -0.3 ~ V <sub>CNTL</sub> +0.3 | V        |

| POK to GND                                      | $V_{POK}$         | -0.3 ~ 7                      | <b>V</b> |

| Average Power Dissipation                       | $P_D$             | 3                             | W        |

| Peak Power Dissipation (<20mS)                  | P <sub>PEAK</sub> | 20                            | W        |

| Junction Temperature                            | $T_J$             | 150                           | °C       |

| Storage Temperature                             | T <sub>STG</sub>  | -65 ~ 150                     | °C       |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

## ■ THERMAL CHARACTERISTICS

| PARAMETER           | SYMBOL        | RATINGS | UNIT |

|---------------------|---------------|---------|------|

| Junction to Ambient | $\theta_{JA}$ | 40      | °C/W |

Note:  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. The exposed pad of SOP-8-P is soldered directly on the PCB.

#### ■ RECOMMENDED OPERATING CONDITIONS

| PARAMETER                        |                           | SYMBOL           | RATINGS                     | UNIT |

|----------------------------------|---------------------------|------------------|-----------------------------|------|

| V <sub>CNTL</sub> Supply Voltage |                           | $V_{CNTL}$       | 3.1 ~ 6                     | V    |

| V <sub>IN</sub> Supply Voltage   |                           | $V_{IN}$         | 1.1 ~ 3.3                   | V    |

|                                  | V <sub>CNTL</sub> =3.3±5% | V <sub>OUT</sub> | 0.8 ~ 1.2                   | V    |

| Output Voltage                   | V <sub>CNTL</sub> =5.0±5% |                  | +0.8 ~ V <sub>IN</sub> -0.2 | V    |

| V <sub>OUT</sub> Output Current  |                           | I <sub>OUT</sub> | 0 ~ 5                       | Α    |

| Operating Junction Temperature   |                           | TJ               | -25 ~ 125                   | °C   |

## ■ ELECTRICAL CHARACTERISTICS

(Refer to the typical application circuit. These specifications apply over,  $V_{CNTL}$  = 5V,  $V_{IN}$  = 1.5V,  $V_{OUT}$  = 1.2V or  $V_{IN}$  = 1.8V,  $V_{OUT}$  = 1.5V or  $V_{IN}$  = 2.1V,  $V_{OUT}$  = 1.8V or  $V_{IN}$  = 2.8V,  $V_{OUT}$  = 2.5V and  $T_A$  = 0 ~ 70°C, unless otherwise specified. Typical values refer to  $T_A$  = 25°C.)

| Specifica. Typical values refer to TA = 2          | 20 0.)                                | 1                                                                        |      |      |      |                  |

|----------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------|------|------|------|------------------|

| PARAMETER                                          | SYMBOL                                | TEST CONDITIONS                                                          | MIN  | TYP  | MAX  | UNIT             |

| SUPPLY CURRENT                                     |                                       |                                                                          |      |      |      |                  |

| V <sub>CNTL</sub> Supply Current                   | I <sub>CNTL</sub>                     | $EN = V_{CNTL}$                                                          | 0.4  | 1    | 8    | mΑ               |

| V <sub>CNTL</sub> Shutdown Current                 | I <sub>SD</sub>                       | EN = GND                                                                 |      | 200  | 380  | μΑ               |

| POWER-ON-RESET                                     |                                       |                                                                          |      |      |      |                  |

| V <sub>CNTL</sub> POR Threshold                    |                                       | V <sub>CNTL</sub> Rising                                                 | 2.7  | 2.9  | 3.1  | ٧                |

| V <sub>CNTL</sub> POR Hysteresis                   |                                       |                                                                          |      | 0.4  |      | V                |

| V <sub>IN</sub> POR Threshold                      |                                       | V <sub>IN</sub> Rising                                                   | 0.8  | 0.9  | 1.0  |                  |

| V <sub>IN</sub> POR Hysteresis                     |                                       |                                                                          |      | 0.5  |      | ٧                |

| OUTPUT VOLTAGE                                     |                                       |                                                                          |      |      | -    |                  |

| Reference Voltage                                  | $V_{REF}$                             | ADJ =V <sub>OUT</sub>                                                    |      | 8.0  |      | V                |

| Output Voltage Accuracy                            |                                       | I <sub>OUT</sub> =0A ~ 5A, T <sub>J</sub> = -25 ~125°C                   | -1.5 |      | +1.5 | %                |

| Line Regulation                                    |                                       | V <sub>CNTL</sub> =3.3 ~ 5.5V                                            |      | 0.06 | 0.3  | %                |

| Load Regulation                                    |                                       | I <sub>OUT</sub> =0A ~ 5A                                                |      | 0.06 | 0.15 | %                |

| DROPOUT VOLTAGE                                    |                                       |                                                                          |      |      | _    |                  |

| Drawa ut Valtaga                                   |                                       | I <sub>OUT</sub> = 5A, V <sub>CNTL</sub> =5V, T <sub>J</sub> = 25°C      |      | 0.2  | 0.25 | V                |

| Dropout Voltage                                    |                                       | I <sub>OUT</sub> = 5A, V <sub>CNTL</sub> =5V, T <sub>J</sub> = -50~125°C |      |      | 0.3  | V                |

| PROTECTION                                         |                                       |                                                                          |      |      | _    |                  |

|                                                    |                                       | V <sub>CNTL</sub> =5V, T <sub>J</sub> = 25°C                             | 7    | 8    | 9    | Α                |

| Current Limit                                      |                                       | V <sub>CNTL</sub> =5V, T <sub>J</sub> = -25 ~ 125°C                      | 6    |      |      | Α                |

| Current Limit                                      | I <sub>LIMIT</sub>                    | V <sub>CNTL</sub> =3.3V, T <sub>J</sub> = 25°C                           | 6.3  | 6.7  | 8.8  | Α                |

|                                                    |                                       | V <sub>CNTL</sub> =3.3V, T <sub>J</sub> = -25 ~ 125°C                    | 6    |      |      | Α                |

| Thermal Shutdown Temperature                       | T <sub>SD</sub>                       | T <sub>J</sub> Rising                                                    |      | 150  |      | °C               |

| Thermal Shutdown Hysteresis                        |                                       |                                                                          |      | 25   |      | °C               |

| Under-Voltage Threshold                            |                                       | ADJ Falling                                                              |      | 0.4  |      | V                |

| Over-Voltage Threshold                             | V <sub>OVP</sub> /V <sub>normal</sub> | Output Voltage up regulation voltage                                     |      | 125  |      | %                |

| ENABLE AND SOFT-START                              |                                       |                                                                          |      |      | _    |                  |

| EN Logic High Threshold Voltage                    |                                       | V <sub>EN</sub> Rising                                                   | 0.3  | 0.4  | 0.5  | V                |

| EN Hysteresis                                      |                                       |                                                                          |      | 30   |      | mV               |

| EN Pin Pull-Up Current                             |                                       | EN=GND                                                                   |      | 10   |      | μΑ               |

| Soft-Start Interval                                | Tss                                   |                                                                          |      | 1.2  |      | ms               |

| POWER OK AND DELAY                                 |                                       |                                                                          |      |      |      |                  |

| P <sub>OK</sub> Threshold Voltage for Power OK     | $V_{POK}$                             | V <sub>ADJ</sub> Rising                                                  | 90%  | 92%  | 94%  | $V_{REF}$        |

| P <sub>OK</sub> Threshold Voltage for Power Not OK | V <sub>PNOK</sub>                     | V <sub>ADJ</sub> Falling                                                 | 79%  | 81%  | 83%  | V <sub>REF</sub> |

| P <sub>OK</sub> Low Voltage                        |                                       | POK sinks 5mA                                                            |      | 0.2  | 0.4  | V                |

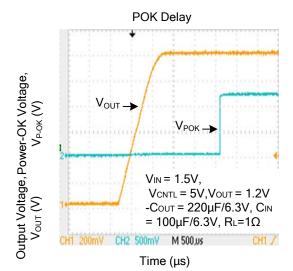

| P <sub>OK</sub> Delay Time                         | T <sub>DELAY</sub>                    |                                                                          | 1    | 1.5  | 10   | mS               |

| ADJ                                                |                                       |                                                                          |      |      |      |                  |

| Adjust Pin threshold                               |                                       |                                                                          | 0.1  | 0.2  | 0.4  | V                |

|                                                    |                                       |                                                                          |      |      |      |                  |

LXXLD50 cmos ic

#### ■ FUNCTIONAL DESCRIPTION

#### Power-On-Reset

A POR (Power-On-Reset) circuit is designed to monitor the two supply voltages at  $V_{CNTL}$  pin and  $V_{IN}$  pin to avoid the unexpected operations. During powering on process, the POR circuit would initiate a soft-start process after the two supply voltages above their rising POR threshold voltages. The POR function also pulls low the  $P_{OK}$  pin regardless the output voltage when the voltage at  $V_{CNTL}$  pin drops below its falling POR threshold.

#### **Internal Soft-Start**

The built-in soft-start circuit controls rise rate of the output voltage to limit the current surge at start-up. The soft-start interval is approximately 1.2mS (TYP.).

#### **Output Voltage Regulation**

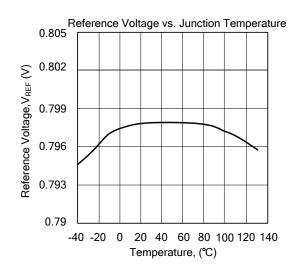

The error amplifier compares a temperature-compensated 0.8V reference with the feedback voltage, which is characterized with high bandwidth and DC gain to provide fast transient response and less load regulation.

The output voltage can be adjusted by an output NMOS to get the preset voltage. The difference which is amplified by the error amplifier provides load current from  $V_{IN}$  pin to  $V_{OUT}$  pin.

#### **Current-Limit**

The current-limit protection circuit is used to protect this device against the maximum current, which occurs in overload or short-circuit conditions. For the UTC **LXXLD50**, the current is monitored through the output NMOS.

#### **Under-Voltage Protection (UVP)**

The UTC **LXXLD50** monitors the voltage on internal feed back signal after soft-start process is finished. Thus, the Under-Voltage circuit is inactive during soft-start. When the voltage on FB signal goes below the under-voltage threshold, the UVP circuit shuts off the output immediately. Last for a period, this device starts a new soft-start to regulate output.

#### **Over-Voltage Protection (OVP)**

The UTC **LXXLD50** monitors the output voltage. When the voltage on V<sub>OUT</sub> pin goes high beyond normal regulation voltage by 25%, the OVP circuit shuts off the output immediately. After a while, the **LXXLD50** starts a new soft-start to regulate output.

#### Thermal Shutdown

The thermal shutdown protection circuit is designed to prevent the junction temperature beyond a certain value. If the junction temperature becomes higher than +150°C, the output NMOS is turned off through a thermal sensor, allowing the device to cool down. The regulator regulates the output again through initiation of a new soft-start cycle after the junction temperature cools by 25°C, resulting in a pulsed output during continuous thermal overload conditions.

The average junction temperature is reduced by the 25°C hysteresis during continuous thermal overload conditions, making this device use longer. Also, the power dissipation should be externally limited to ensure junction temperature under +125°C during normal operation.

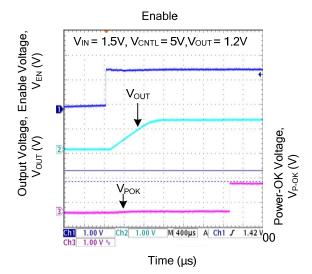

#### **Enable Control**

If the EN pin is applied to a logic low signal ( $V_{EN}$ < 0.3V), the output would be shut down. Following a shutdown, a logic high signal re-enables the output through initiation of a new soft-start cycle. Left open, this pin is pulled up by an internal current source (10 $\mu$ A Typical) to enable operation. For a low cost-effectiveness, an external transistor is not required.

### **Power-OK and Delay**

For the UTC **LXXLD50**, the Power-OK circuit indicates the status of the output voltage by monitoring the internal feedback voltage ( $V_{FB}$ ). When the feedback voltage becomes equal to the rising Power-OK threshold ( $V_{POK}$ ), an internal delay function starts to perform a delay time. At the end of the delay time, the IC shuts off the internal NMOS of the POK to indicate the output is OK. When the feedback voltage becomes equal to the falling Power-OK threshold ( $V_{PNOK}$ ), the IC immediately turns on the NMOS of the  $P_{OK}$  to indicate the output is not OK without a delay time.

#### APPLICATION INFORMATION

#### Power Sequencing

Less consideration could be taken into the power sequencing of  $V_{IN}$  and  $V_{CNTL}$ . But do not apply a voltage to  $V_{OUT}$  for a long time when the main voltage applied at  $V_{IN}$  is not present. The reason is the internal parasitic diode from  $V_{OUT}$  to  $V_{IN}$  conducts and dissipates power without protections due to the forward-voltage.

#### **Output Capacitor**

For the maximum device performance and improving system stability, transient response over temperature and current, a well-suitable output capacitor is needed. The selected output capacitor should be qualified perfect ESR (equivalent series resistance) and capacitor value for a better system stability and load transient.

The UTC **LXXLD50** is designed with a programmable feedback compensation adjusted by an external feedback network for the use of wide ranges of ESR and capacitance in all applications. The output capacitors can be ultra-low-ESR capacitors, such as ceramic chip capacitors; low-ESR bulk capacitors, such as solid Tantalum, POSCap, and Aluminum electrolytic capacitors, and their values can be increased without limit.

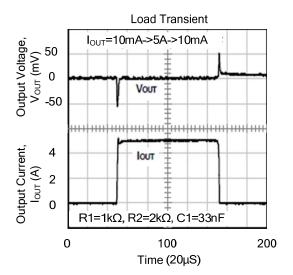

During load transients, the output capacitors, depending on the stepping amplitude and slew rate of load current, are used to reduce the slew rate of the current seen by the UTC **LXXLD50** and help the device to minimize the variations of output voltage for good transient response. Therefore, low-ESR bulk capacitors are universally to be expected for the applications with large stepping load current.

In addition, decoupling ceramic capacitors must be located to the load and GND as close as possible and the layout's impedance should be maintained minimum.

#### **Input Capacitor**

The input capacitors should be chosen properly due to supply current to protect the input rail against dropping during stepping load transients. Because the parasitic inductor from the voltage sources or other bulk capacitors to the VIN pin limit the slew rate of the surge currents. More parasitic inductance needs more input capacitance. More capacitance reduces the variations of the  $V_{IN}$  pin voltage.

For the UTC **LXXLD50**, input capacitors with low-ESR are not needed. Ultra-low-ESR capacitors (such as ceramic chip capacitors) are good options, and an aluminum electrolytic capacitor (>100 $\mu$ F, ESR <300m $\Omega$ ) is recommended as the input capacitor.

#### **Feedback Network**

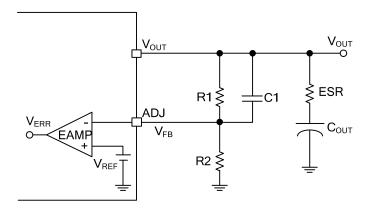

In the following, the feedback network between  $V_{\text{OUT}}$ , GND and FB pins is shown in Figure 1. It works with the internal error amplifier to provide proper frequency response for the linear regulator.

As seen in Figure 1, the ESR is the equivalent series resistance of the output capacitor. The  $C_{OUT}$  is ideal capacitance in the output capacitor. The  $V_{OUT}$  is the setting of the output voltage.

Figure 1.

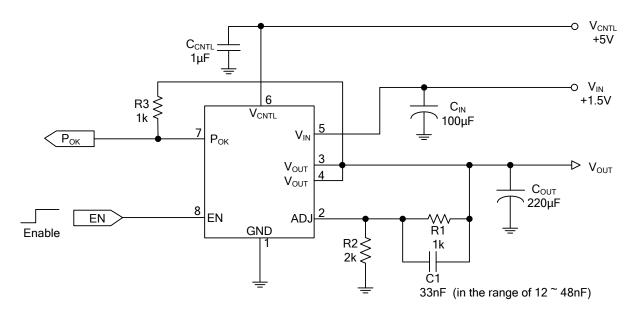

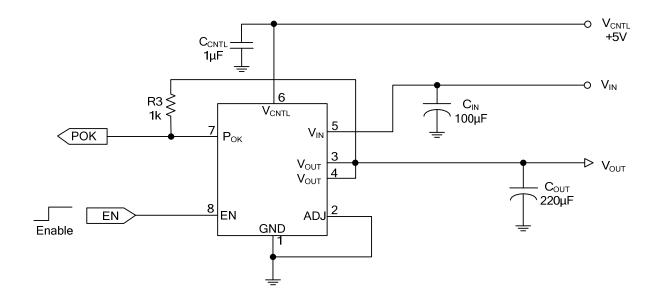

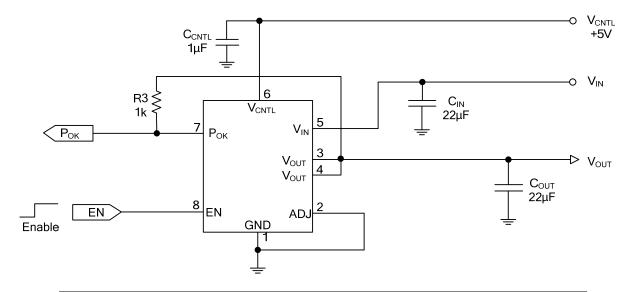

## ■ TYPICAL APPLICATION CIRCUIT

1. Using an Output Capacitor with ESR≥18mΩ

ADJ Mode

## Fixed Voltage Mode

LXXLD50 cmos ic

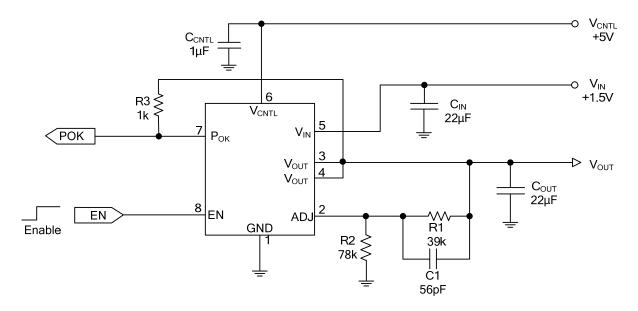

## ■ TYPICAL APPLICATION CIRCUIT (Cont.)

2. Using an MLCC as the Output Capacitor

## ADJ Mode

## Fixed Voltage Mode

| V <sub>OUT</sub> (V) | R1 (kΩ) | R2 (kΩ) | C1 (pF) |

|----------------------|---------|---------|---------|

| 1.05                 | 43      | 137.6   | 47      |

| 1.5                  | 27      | 30.86   | 82      |

| 1.8                  | 15      | 12      | 150     |

LXXLD50 cmos ic

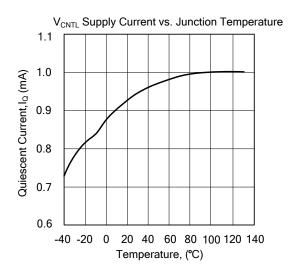

#### ■ TYPICAL CHARACTERISTICS

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice.