# Features

- Incorporates the ARM7TDMI<sup>®</sup> ARM<sup>®</sup> Thumb<sup>®</sup> Processor

- 72 MIPS at 80MHz

– EmbeddedICE™ In-circuit Emulation, Debug Communication Channel Support

Additional Embedded Memories

- One 256 Kbyte Internal ROM, Single-cycle Access at Maximum Matrix Speed

- 160 Kbytes of Internal SRAM, Single-cycle Access at Maximum Processor or

- Matrix Speed (Configured in blocks of 96 KB and 64 KB with separate AHB slaves) • External Bus Interface (EBI)

- Supports SDRAM, Static Memory, NAND Flash/SmartMedia $^{ extsf{B}}$  and CompactFlash $^{ extsf{B}}$

- USB 2.0 Full Speed (12 Mbits per second) Device Port

- On-chip Transceiver, 2,432-byte Configurable Integrated DPRAM

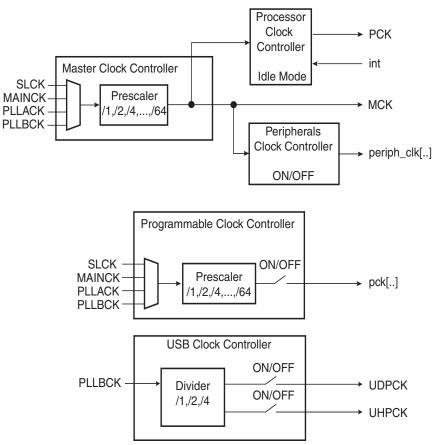

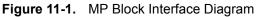

- Metal Programmable Block

- 450000 Gates Metal Programmable Logic for CAP7

- Two 4Kbytes Dual Port RAMs for buffer space

- High Connectivity for up to 4 AHB Masters and 4 dedicated/16 muxed Slaves for CAP7

- Up to twenty-eight AIC interrupt inputs

- Access to Atmel AHB/APB library

- Up to 90 dedicated I/Os

- Optional PIO controller for up to 32 of the available I/Os

- 10-bit Analog to Digital Converter (ADC)

- Up to 8 multiplexed channels

- 440 kSample / s

- Bus Matrix

- Six-layer, 32-bit Matrix, Allowing 15.4 Gbps of On-chip Bus Bandwidth

- Fully-featured System Controller, including

- Reset Controller, Shut Down Controller

- Twenty 32-bit Battery Backup Registers for a Total of 80 Bytes

- Clock Generator

- Advanced Power Management Controller (APMC)

- Advanced Interrupt Controller and Debug Unit

- Periodic Interval Timer, Watchdog Timer and Real-Time Timer

- Boot Mode Select Option and Remap Command

- Reset Controller

- Based on Two Power-on Reset Cells, Reset Source Identification and Reset Output Control

- Shut Down Controller

- Programmable Shutdown Pin Control and Wake-up Circuitry

- Clock Generator (CKGR)

- 32768Hz Low-power Oscillator on Battery Backup Power Supply, Providing a Permanent Slow Clock

- Internal 32kHz RC oscillator for fast start-up

- 8 to 16 MHz On-chip Oscillator, 50 to 100 MHz PLL, and 80 to 240 MHz PLL

- Advanced Power Management Controller (APMC)

- Very Slow Clock Operating Mode, Software Programmable Power Optimization Capabilities

- Four Programmable External Clock Output Signals

Customizable Microcontroller

# AT91CAP7S450A

# Preliminary Summary

5119DS-CAP-05/09

- Advanced Interrupt Controller (AIC)

- Individually Maskable, Eight-level Priority, Vectored Interrupt Sources

- Two External Interrupt Sources and one Fast Interrupt Source, Spurious interrupt protected

- Debug Unit (DBGU)

- 2-wire UART and Support for Debug Communication Channel, Programmable ICE Access Prevention

- Periodic Interval Timer (PIT)

- 20-bit interval Timer plus 12-bit interval Counter

- Watchdog Timer (WDT)

- Key-protected, Programmable Only Once, Windowed 16-bit Counter Running at Slow Clock

- Real-Time Timer (RTT)

- 32-bit Free-running Backup Counter Running at Slow Clock with 16-bit Prescaler

- One 32-bit Parallel Input/Output Controllers (PIOA)

- 32 Programmable I/O Lines Multiplexed with up to Two Peripheral I/Os each

- Input Change Interrupt Capability on Each I/O Line

- Individually Programmable Open-drain, Pull-up Resistor, Bus Holder and Synchronous Output

- Additional PIO Controllers can be added in the Metal Programmable Block

- 22 Peripheral DMA Controller Channels (PDC)

- Two Universal Synchronous/Asynchronous Receiver Transmitters (USART)

- Individual Baud Rate Generator, IrDA<sup>®</sup> Infrared Modulation/Demodulation, Manchester Encoding/Decoding

- Master/Slave Serial Peripheral Interface (SPI)

- 8- to 16-bit Programmable Data Length, External Peripheral Chip Select

- Synchronous Communications at up to 80Mbits/sec

- One Three-channel 16-bit Timer/Counters (TC)

- Three External Clock Inputs, Two multi-purpose I/O Pins per Channel

- Double PWM Generation, Capture/Waveform Mode, Up/Down Capability

- IEEE 1149.1 JTAG Boundary Scan on All Digital Pins

- Required Power Supplies:

- 1.08V to 1.32V for VDDCORE and VDDBU

- 1.08V to 1.32V for VDDOSC, VDDOSC32, and VDDPLLB

- 3.0V to 3.6V for VDDPLLA and VDDIO

- 3.0V to 3.6V for AVDD (ADC)

- Package Options: 144 LQFP, 176 LQFP, 208 PQFP, 144 LFBGA, 176TFBGA, 208 TFBGA, 225 LFBGA

# 1. Description

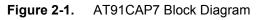

The AT91CAP7 semi-custom System on a Chip (SoC) provides Atmel's ASIC customers a microcontroller platform for rapid integration of their own Intellectual Property (IP) in metal programmable cells. Fabrication time is greatly reduced since only the metal layers will remain to be generated on the silicon. In addition to 450K gates of metal programmable logic, the AT91CAP7 includes an ARM7TDMI core with a high-speed bus (AHB), on-chip ROM and SRAM, a full-featured system controller, and various general-purpose peripheral subsystems. It is implemented in a 130 nm CMOS 1.2V process and supports 3.3V I/O.

# 2. Block Diagram

# 3. Signal Description

# Table 3-1. Signal Description by Peripheral

| Signal Name | Function                                              | Туре      | Active<br>Level | Comments                                                                                                                              |

|-------------|-------------------------------------------------------|-----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|

|             | Power Supplies                                        | 5         | I               |                                                                                                                                       |

| VDDCORE     | Core Chip Power Supply                                | Power     |                 | 1.08V to 1.32V                                                                                                                        |

| VDDBU       | Backup Power Supply, includes Backup<br>I/O and Logic | Power     |                 | 1.08V to 1.32V, required for all operational modes.                                                                                   |

| VDDIO       | I/O Lines Power Supply, except Backup<br>I/O          | Power     |                 | 3.0V to 3.6V                                                                                                                          |

| VDDPLLA     | PLL A Power Supply                                    | Power     |                 | 3.0V to 3.6V                                                                                                                          |

| VDDPLLB     | PLL B Power Supply                                    | Power     |                 | 1.08V to 1.32V                                                                                                                        |

| VDDOSC      | Oscillator Power Supply                               | Power     |                 | 1.08V to 1.32V                                                                                                                        |

| VDDOSC32    | Oscillator Power Supply                               | Power     |                 | 1.08V to 1.32V, required for all operational modes.                                                                                   |

| AVDD        | ADC Analog Power Supply                               | Power     |                 | 3.0V to 3.6V                                                                                                                          |

| GND         | VDDIO and VDDCORE Ground                              | Ground    |                 |                                                                                                                                       |

| GNDPLLA     | PLL Ground A                                          | Ground    |                 |                                                                                                                                       |

| GNDPLLB     | PLL Ground B                                          | Ground    |                 |                                                                                                                                       |

| GNDOSC      | Main Oscillator Ground                                | Ground    |                 |                                                                                                                                       |

| GNDOSC32    | 32 kHz Oscillator Ground                              | Ground    |                 |                                                                                                                                       |

| GNDBU       | Backup Ground                                         | Ground    |                 |                                                                                                                                       |

| AGND        | ADC Analog Ground                                     | Ground    |                 |                                                                                                                                       |

|             | Clocks, Oscillators an                                | d PLLs    |                 |                                                                                                                                       |

| XIN         | Main Oscillator Input                                 | Input     | Analog          | Connect to an external crystal<br>or drive with a 1.2V nominal<br>square wave clock input                                             |

| XOUT        | Main Oscillator Output                                | Output    | Analog          | Connect to external crystal or leave unconnected                                                                                      |

| XIN32       | Slow Clock Oscillator Input                           | Input     | Analog          | Connect to a 32768Hz crystal<br>or drive with a 1.2V, 32kHz<br>nominal square wave Input,<br>leave unconnected (32kHz RC<br>OSC only) |

| XOUT32      | Slow Clock Oscillator Output                          | Output    | Analog          | Connect to a 32768Hz crystal<br>or leave unconnected                                                                                  |

| PLLRCA      | PLL A Filter                                          | Input     | Analog          | Must connect to an<br>appropriate RC network for<br>proper PLL operation                                                              |

| PCK0 - PCK3 | Programmable Clock Output                             | Output    | Clock           | access via PIOA                                                                                                                       |

|             | Analog to Digital Cor                                 | verter    |                 |                                                                                                                                       |

| AD0         | ADC Input 0                                           | An. Input | Analog          | shared with MPIO82                                                                                                                    |

| Signal Name | Function                    | Туре        | Active<br>Level | Comments                                                                                                   |

|-------------|-----------------------------|-------------|-----------------|------------------------------------------------------------------------------------------------------------|

| AD1         | ADC Input 1                 | An. Input   | Analog          | shared with MPIO83                                                                                         |

| AD2         | ADC Input 2                 | An. Input   | Analog          | shared with MPIO84                                                                                         |

| AD3         | ADC Input 3                 | An. Input   | Analog          | shared with MPIO85                                                                                         |

| AD4         | ADC Input 4                 | An. Input   | Analog          | shared with MPIO86                                                                                         |

| AD5         | ADC Input 5                 | An. Input   | Analog          | shared with MPIO87                                                                                         |

| AD6         | ADC Input 6                 | An. Input   | Analog          | shared with MPIO88                                                                                         |

| AD7         | ADC Input 7                 | An. Input   | Analog          | shared with MPIO89                                                                                         |

| ADVREF      | ADC Voltage Reference Input | An. Input   | Analog          | Do not leave floating - Connect<br>to AVDD externally or another<br>analog voltage reference up to<br>3.3V |

| ADTRG       | ADC External Trigger        | Dig. Input  | High            | Tie to AGND externally if<br>enabled and not used - access<br>via PIOA                                     |

|             | Shutdown, Wa                | ke-up Logic |                 |                                                                                                            |

| SHDW        | Shut-Down Control           | Output      | High            | Driven at 0V only. Do not tie<br>over VDDBU                                                                |

| WKUP0WKUP0  | Wake-Up Input               | Input       |                 | Accept between 0V and VDDBU.                                                                               |

|             | ICE and                     | JTAG        |                 |                                                                                                            |

| ТСК         | Test Clock                  | Input       |                 | Pull-down resistor                                                                                         |

| TDI         | Test Data In                | Input       |                 | Pull-up resistor                                                                                           |

| TDO         | Test Data Out               | Output      |                 | Pull-up resistor                                                                                           |

| TMS         | Test Mode Select            | Input       |                 | Pull-up resistor                                                                                           |

| NTRST       | Test Reset Signal           | Input       | Low             | Pull-up resistor                                                                                           |

| JTAGSEL     | JTAG Selection              | Input       | High            | Pull-down resistor                                                                                         |

|             | Reset                       | Test        |                 |                                                                                                            |

| NRST        | Microcontroller Reset       | I/O         | Low             | Pull-up resistor<br>Accept between 0V and<br>VDDBU                                                         |

|             |                             |             |                 | Pull-down resistor                                                                                         |

| TST         | Chip Test Enable            | Input       | High            | Accept between 0V and VDDBU                                                                                |

| BMS         | Boot Mode Select            | Input       |                 | Pull-up resistor<br>1=embedded ROM<br>0=EBI CS0                                                            |

|             | Debug Uni                   | t - DBGU    | 1               |                                                                                                            |

| DRXD        | Debug Receive Data          | Input       |                 | access via PIOA                                                                                            |

| DTXD        | Debug Transmit Data         | Output      |                 | access via PIOA                                                                                            |

Table 3-1.

Signal Description by Peripheral (Continued)

## Table 3-1. Signal Description by Peripheral (Continued)

| Signal Name   | Function                       | Туре            | Active<br>Level | Comments                                               |

|---------------|--------------------------------|-----------------|-----------------|--------------------------------------------------------|

|               | Advanced Interrupt Co          | ontroller - AIC | 1               |                                                        |

| IRQ0 - IRQ1   | External Interrupt Inputs      | Input           | High            | access via PIOA                                        |

| FIQ           | Fast Interrupt Input           | Input           | High            | access via PIOA                                        |

|               | PIO Controller                 | - PIOA          |                 |                                                        |

| PA0 - PA31    | Parallel IO Controller A       | I/O             |                 | Pulled-up input at reset                               |

|               | External Bus Inter             | face - EBI      |                 |                                                        |

| D0 - D31      | Data Bus                       | I/O             |                 | Pulled-up input at reset;<br>access D16 - D31 via PIOA |

| A0 - A25      | Address Bus                    | Output          |                 | 0 at reset; access A23-A25 via<br>PIOA                 |

| NWAIT         | External Wait Signal           | Input           | Low             | access via PIOA                                        |

|               | Static Memory Cont             | roller - SMC    |                 |                                                        |

| NCS0 - NCS7   | Chip Select Lines              | Output          | Low             | access NCS4 - NCS7 via<br>PIOA                         |

| NWR0 -NWR3    | Write Signal                   | Output          | Low             |                                                        |

| NRD           | Read Signal                    | Output          | Low             |                                                        |

| NWE           | Write Enable                   | Output          | Low             |                                                        |

| NBS0 - NBS3   | Byte Mask Signal               | Output          | Low             |                                                        |

|               | CompactFlash S                 | Support         |                 |                                                        |

| CFCE1 - CFCE2 | CompactFlash Chip Enable       | Output          | Low             | access via PIOA                                        |

| CFOE          | CompactFlash Output Enable     | Output          | Low             |                                                        |

| CFWE          | CompactFlash Write Enable      | Output          | Low             |                                                        |

| CFIOR         | CompactFlash IO Read           | Output          | Low             |                                                        |

| CFIOW         | CompactFlash IO Write          | Output          | Low             |                                                        |

| CFRNW         | CompactFlash Read Not Write    | Output          |                 | access via PIOA                                        |

| CFCS0 - CFCS1 | CompactFlash Chip Select Lines | Output          | Low             | access via PIOA                                        |

|               | NAND Flash S                   | upport          |                 |                                                        |

| NANDCS        | NAND Flash Chip Select         | Output          | Low             |                                                        |

| NANDOE        | NAND Flash Output Enable       | Output          | Low             | access via PIOA                                        |

| NANDWE        | NAND Flash Write Enable        | Output          | Low             | access via PIOA                                        |

|               | SDRAM Cont                     | roller          |                 |                                                        |

| SDCK          | SDRAM Clock                    | Output          |                 |                                                        |

| SDCKE         | SDRAM Clock Enable             | Output          | High            |                                                        |

| SDCS          | SDRAM Controller Chip Select   | Output          | Low             |                                                        |

| BA0 - BA1     | Bank Select                    | Output          |                 |                                                        |

| Signal Name           | Function                           | Туре           | Active<br>Level | Comments        |

|-----------------------|------------------------------------|----------------|-----------------|-----------------|

| SDWE                  | SDRAM Write Enable                 | Output         | Low             |                 |

| RAS - CAS             | Row and Column Signal              | Output         | Low             |                 |

| SDA10                 | SDRAM Address 10 Line              | Output         |                 |                 |

|                       | Universal Synchronous Asynchronous | Receiver Trans | smitter USA     | RT              |

| SCKx                  | USARTx Serial Clock                | I/O            |                 | access via PIOA |

| TXDx                  | USARTx Transmit Data               | I/O            |                 | access via PIOA |

| RXDx                  | USARTx Receive Data                | Input          |                 | access via PIOA |

| RTSx                  | USARTx Request To Send             | Output         |                 | access via PIOA |

| CTSx                  | USARTx Clear To Send               | Input          |                 | access via PIOA |

|                       | Timer/Counter                      | - TC           |                 |                 |

| TCLKx                 | TC Channel x External Clock Input  | Input          |                 | access via PIOA |

| TIOAx                 | TC Channel x I/O Line A            | I/O            |                 | access via PIOA |

| TIOBx                 | TC Channel x I/O Line B            | I/O            |                 | access via PIOA |

|                       | Serial Peripheral Inte             | rface - SPI    |                 |                 |

| SPI_MISO              | Master In Slave Out                | I/O            |                 | access via PIOA |

| SPI_MOSI              | Master Out Slave In                | I/O            |                 | access via PIOA |

| SPI_SPCK              | SPI Serial Clock                   | I/O            |                 | access via PIOA |

| SPI_NPCS0             | SPI Peripheral Chip Select 0       | I/O            | Low             | access via PIOA |

| SPI_NPCS1 - SPI_NPCS3 | SPI Peripheral Chip Select         | Output         | Low             | access via PIOA |

|                       | USB Device P                       | ort            |                 |                 |

| DDM                   | USB Device Port Data -             | Analog         |                 |                 |

| DDP                   | USB Device Port Data +             | Analog         |                 |                 |

|                       | Metal Programmable E               | Block - MPB    |                 |                 |

| MPIO0 - MPIO89        | MPB general purpose I/O            | I/O            |                 |                 |

## Table 3-1. Signal Description by Peripheral (Continued)

# 4. Package and Pinout

The AT91CAP7 is available in a variety of RoHS-compliant packages. The following AT91CAP7 package options have pre-defined, fixed pinouts listed in various sections below:

- 225-ball LFBGA 13x13x1.4mm, 0.8 mm ball pitch

- 208-PQFP 28x28x3.4mm, 0.5 mm pin pitch

- 176-LQFP 20x20x1.4 mm, 0.5 mm pin pitch

- 144-LQFP 20x20x1.4 mm, 0.5 mm pin pitch.

The following packages are also available for AT91CAP7 on advance request. These package options may require custom BGA substrate design. The pinouts for these packages are not yet published but will be similar to their QFP counterparts listed above.

- 208-TFBGA 15x15x1.2mm, 0.8 mm ball pitch

- 176-TFBGA 10x10 12x12x1.2mm, 0.8 mm ball pitch

- 144-LFBGA 10x10x1.4mm, 0.8 mm ball pitch

#### Package Selection Guide 4.1

The following table summarizes the functions and interfaces available in each package.

| I/O Features              | 225 LFBGA  | 208 PQFP   | 176 LQFP   | 144 LQFP      |

|---------------------------|------------|------------|------------|---------------|

| MPIO pins available       | 82         | 44         | 33         | 16            |

| MPIO / ADC Channels       | 8          | 5          | 8          | 4             |

| Total PIOA pins available | 32         | 32         | 13         | 11            |

| EBI Data Bus Width        | 16 or 32   | 16 or 32   | 16         | 16            |

| EBI Address Bus Width     | 26         | 25         | 23         | 23            |

| SDRAM                     | yes        | yes        | yes        | no            |

| Static Memory             | yes (8 cs) | yes (8 cs) | yes (7 cs) | yes (5 cs)    |

| Compact Flash             | yes        | yes        | yes (1 ce) | yes (1 cs/ce) |

| NAND Flash                | yes        | yes        | yes        | yes           |

| Boot Mode Select          | yes        | yes        | yes        | yes           |

| ADC External Trigger      | yes        | yes        | yes        | yes           |

| Debug Unit                | yes        | yes        | yes        | yes           |

| USART0                    | yes        | yes        | yes        | yes           |

| USART1                    | yes        | yes        | no         | no            |

| SPI                       | yes (4 cs) | yes (4 cs) | yes (3 cs) | yes (1 cs)    |

| Timer I/O                 | yes        | yes        | no         | no            |

| External IRQ's            | 2          | 2          | 2          | 1             |

| External FIQ              | 1          | 1          | 1          | 1             |

| Main Clock Oscillator     | yes        | yes        | yes        | yes           |

| 32 kHz Oscillator         | yes        | yes        | yes        | yes           |

| External APMC Clocks      | 4          | 4          | no         | no            |

abla 1 1 AT01CAP7 Package Selection Guide

# 4.2 Mechanical Overview of the 225-ball LFBGA Package

Figure 4-1 shows the orientation of the 225-ball LFBGA Package. A detailed mechanical description is given in the Mechanical Characteristics section of the product datasheet.

| 15                                      | 14                | 13                | 12                | 11                | 10                                      | 9                 | 8                 | 7                 | 6                 | 5                 | 4                 | 3                 | 2                 | 1                |                               |

|-----------------------------------------|-------------------|-------------------|-------------------|-------------------|-----------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-------------------------------|

| 000000000000000000000000000000000000000 | 00000000000000000 | 00000000000000000 | 00000000000000000 | 00000000000000000 | 000000000000000000000000000000000000000 | 00000000000000000 | 00000000000000000 | 00000000000000000 | 00000000000000000 | 00000000000000000 | 00000000000000000 | 00000000000000000 | 00000000000000000 | 0000000000000000 | A B C D E F G H J K L M N P R |

|                                         |                   |                   |                   |                   |                                         |                   |                   |                   |                   |                   |                   |                   |                   |                  |                               |

### 4.3 225-ball LFBGA Package Pinout

Warning: This package pinout is preliminary and is subject to change.

Table 4-2.

AT91CAP7 Pinout for 225-ball LFBGA Package

| Pin | Signal Name |

|-----|-------------|-----|-------------|-----|-------------|-----|-------------|

| A1  | MPIO81      | D13 | MPIO01      | H10 | VDDC        | M7  | PA22        |

| A2  | PA9         | D14 | MPIO75      | H11 | D5          | M8  | MPIO89/AD7  |

| A3  | PA8         | D15 | MPIO34      | H12 | PA3         | M9  | PA14        |

| A4  | MPIO45      | E1  | A3          | H13 | PA2         | M10 | MPIO70      |

| A5  | MPIO25      | E2  | A4          | H14 | A9          | M11 | GNDPLLA     |

| A6  | PA4         | E3  | MPIO80      | H15 | A10         | M12 | TDO         |

| A7  | MPIO13      | E4  | MPIO56      | J1  | D7          | M13 | TDI         |

| A8  | MPIO23      | E5  | BMS         | J2  | D6          | M14 | PA28        |

| A9  | MPIO20      | E6  | PA10        | J3  | MPIO31      | M15 | NWR0        |

| A10 | MPIO43      | E7  | NCS2        | J4  | D8          | N1  | MPIO61      |

| A11 | MPIO41      | E8  | MPIO09      | J5  | DDP         | N2  | MPIO64      |

| A12 | MPIO40      | E9  | MPIO08      | J6  | D2          | N3  | VDDBU       |

| A13 | MPIO03      | E10 | MPIO05      | J7  | GND         | N4  | XOUT32      |

| A14 | MPIO76      | E11 | MPIO39      | J8  | GND         | N5  | MPIO85/AD3  |

| A15 | A18         | E12 | MPIO00      | J9  | GND         | N6  | AVDD        |

| B1  | A6          | E13 | MPIO35      | J10 | A12         | N7  | PA20        |

| B2  | MPIO49      | E14 | MPIO32      | J11 | MPIO17      | N8  | PA13        |

| B3  | MPIO48      | E15 | SDA10       | J12 | PA0         | N9  | MPIO67      |

| B4  | MPIO46      | F1  | SDWE        | J13 | PA1         | N10 | NRD         |

| B5  | PA5         | F2  | A2          | J14 | MPIO19      | N11 | PLLRCA      |

| B6  | MPIO24      | F3  | MPIO55      | J15 | A8          | N12 | XIN         |

| B7  | MPIO15      | F4  | SDRAMCKE    | K1  | MPIO29      | N13 | VDDPLLA     |

Table 4-2. AT91CAP7 Pinout for 225-ball LFBGA Package (Continued)

| n   | Signal Name |   | Pin | Signal Name | Pin | Signal Name | Pin | Signal I |

|-----|-------------|---|-----|-------------|-----|-------------|-----|----------|

| 38  | MPIO11      | 1 | F5  | MPIO53      | К2  | MPIO30      | N14 | PA29     |

| B9  | MPIO22      |   | F6  | A0          | К3  | MPIO60      | N15 | NRST     |

| B10 | MPIO44      |   | F7  | VDDIO       | K4  | MPIO59      | P1  | D4       |

| B11 | MPIO06      |   | F8  | MPIO26      | K5  | MPIO62      | P2  | D3       |

| B12 | MPIO04      |   | F9  | VDDIO       | K6  | WKUP0       | P3  | SHDW     |

| B13 | MPIO37      |   | F10 | A19         | K7  | VDDIO       | P4  | TST      |

| B14 | MPIO74      |   | F11 | MPIO36      | K8  | VDDC        | P5  | MPIO82/  |

| B15 | A20         |   | F12 | MPIO33      | К9  | VDDIO       | P6  | MPIO87/  |

| C1  | MPIO52      |   | F13 | A14         | K10 | XOUT        | P7  | PA21     |

| C2  | NCS3        |   | F14 | A16         | K11 | PA25        | P8  | PA16     |

| C3  | MPIO50      |   | F15 | A15         | K12 | TMS         | P9  | PA11     |

| C4  | MPIO79      | 1 | G1  | MPIO28      | K13 | PA24        | P10 | MPIO68   |

| C5  | PA7         | 1 | G2  | SDRAMCLK    | K14 | MPIO16      | P11 | GNDOSC   |

| C6  | MPIO27      |   | G3  | A1          | K15 | MPIO18      | P12 | NWR1     |

| C7  | PA6         |   | G4  | D14         | L1  | MPIO57      | P13 | VDDOSC   |

| C8  | MPIO12      |   | G5  | D15         | L2  | MPIO58      | P14 | TCK      |

| C9  | MPIO21      |   | G6  | VDDC        | L3  | D1          | P15 | PA27     |

| C10 | MPIO07      |   | G7  | GND         | L4  | MPIO65      | R1  | JTAGSEL  |

| C11 | MPIO38      |   | G8  | GND         | L5  | VDDOSC32    | R2  | ADVREF   |

| C12 | MPIO78      |   | G9  | GND         | L6  | GNDBU       | R3  | MPIO84/A |

| C13 | A22         |   | G10 | VDDIO       | L7  | MPIO86/AD4  | R4  | MPIO88/A |

| C14 | A21         |   | G11 | RAS         | L8  | NCS1        | R5  | AGND     |

| C15 | A17         |   | G12 | N/C         | L9  | PA17        | R6  | PA23     |

| D1  | MPIO54      |   | G13 | A11         | L10 | GNDPLLB     | R7  | PA19     |

| D2  | A5          |   | G14 | CAS         | L11 | PA31        | R8  | PA15     |

| D3  | A7          |   | G15 | A13         | L12 | NTRST       | R9  | PA12     |

| D4  | NCS0        |   | H1  | D10         | L13 | MPIO73      | R10 | MPIO66   |

| D5  | MPIO51      |   | H2  | D9          | L14 | PA30        | R11 | MPIO69   |

| D6  | MPIO47      |   | H3  | D13         | L15 | PA18        | R12 | MPIO71   |

| D7  | NWR3        |   | H4  | D11         | M1  | DDM         | R13 | MPIO72   |

| D8  | MPIO14      |   | H5  | D12         | M2  | MPIO63      | R14 | VDDPLLE  |

| D9  | MPIO10      |   | H6  | VDDIO       | M3  | D0          | R15 | PA26     |

| D10 | MPIO42      |   | H7  | GND         | M4  | XIN32       |     |          |

| D11 | MPIO77      |   | H8  | GND         | M5  | GNDOSC32    |     |          |

| D12 | MPIO02      |   | H9  | GND         | M6  | MPIO83/AD1  |     |          |

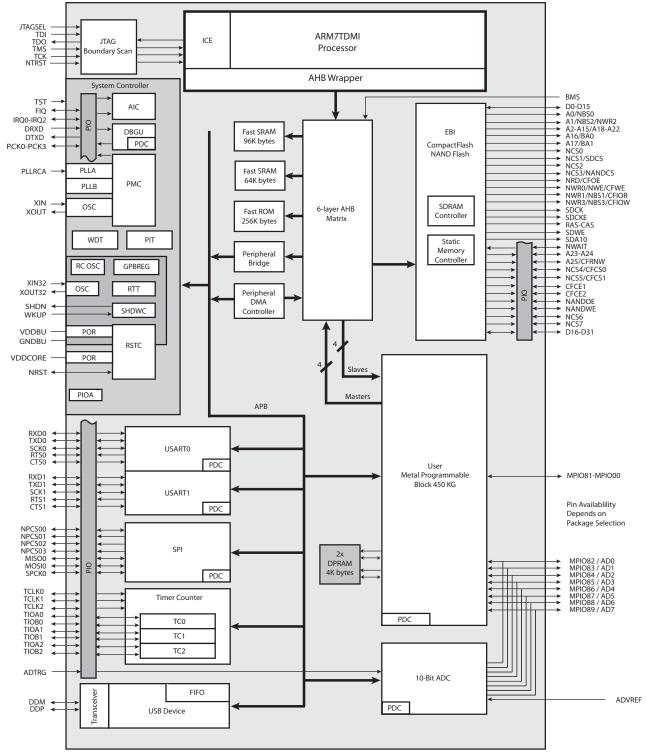

## 4.4 Mechanical Overview of the 208-pin PQFP Package

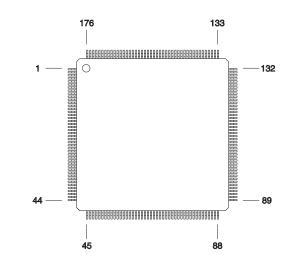

Figure 4-2 shows the orientation of the 208-pin PQFP Package. A detailed mechanical description is given in the Mechanical Characteristics section of the product datasheet.

## 4.5 208-pin PQFP Package Pinout

Warning: The package pinout is preliminary and is subject to change.

Table 4-3.

AT91CAP7 Pinout for 208-pin PQFP Package

| Pin | Signal Name |

|-----|-------------|-----|-------------|-----|-------------|-----|-------------|

| 1   | NTRST       | 53  | MPIO01      | 105 | A7          | 157 | VDDOSC32    |

| 2   | TDI         | 54  | MPIO02      | 106 | GND         | 158 | XIN32       |

| 3   | PA31        | 55  | VDDIO       | 107 | VDDIO       | 159 | XOUT32      |

| 4   | TDO         | 56  | GND         | 108 | A6          | 160 | GNDOSC32    |

| 5   | PA30        | 57  | MPIO03      | 109 | A5          | 161 | VDDBU       |

| 6   | TMS         | 58  | MPIO04      | 110 | VDDCORE     | 162 | SHDW        |

| 7   | PA29        | 59  | MPIO05      | 111 | MPIO55      | 163 | WKUP0       |

| 8   | тск         | 60  | MPIO41      | 112 | A4          | 164 | JTAGSEL     |

| 9   | PA28        | 61  | MPIO06      | 113 | MPIO56      | 165 | TST         |

| 10  | GND         | 62  | MPIO42      | 114 | GND         | 166 | GNDBU       |

| 11  | PA27        | 63  | MPIO07      | 115 | NCS2        | 167 | ADVREF      |

| 12  | VDDIO       | 64  | MPIO43      | 116 | A3          | 168 | MPIO82/AD0  |

| 13  | PA26        | 65  | GND         | 117 | SDRAMCKE    | 169 | MPIO83/AD1  |

| 14  | NRST        | 66  | GND         | 118 | A2          | 170 | MPIO84/AD2  |

| 15  | PA25        | 67  | MPIO44      | 119 | SDWE        | 171 | MPIO85/AD3  |

| 16  | NWR0        | 68  | VDDIO       | 120 | VDDIO       | 172 | MPIO86/AD4  |

Table 4-3.

AT91CAP7 Pinout for 208-pin PQFP Package (Continued)

| Pin | Signal Name |

|-----|-------------|-----|-------------|-----|-------------|-----|-------------|

| 17  | PA24        | 69  | MPIO20      | 121 | SDRAMCLK    | 173 | AVDD        |

| 18  | PA0         | 70  | MPIO08      | 122 | A1          | 174 | AGND        |

| 19  | MPIO16      | 71  | MPIO21      | 123 | MPIO28      | 175 | GND         |

| 20  | PA1         | 72  | MPIO09      | 124 | GND         | 176 | PA23        |

| 21  | MPIO17      | 73  | MPIO22      | 125 | A0          | 177 | VDDIO       |

| 22  | VDDCORE     | 74  | MPIO10      | 126 | D15         | 178 | PA22        |

| 23  | MPIO18      | 75  | MPIO23      | 127 | D14         | 179 | GND         |

| 24  | GND         | 76  | VDDCORE     | 128 | D13         | 180 | PA21        |

| 25  | MPIO19      | 77  | VDDIO       | 129 | D12         | 181 | NCS1        |

| 26  | PA2         | 78  | MPIO11      | 130 | D11         | 182 | PA20        |

| 27  | PA3         | 79  | GND         | 131 | D10         | 183 | VDDCORE     |

| 28  | A8          | 80  | MPIO12      | 132 | D9          | 184 | PA19        |

| 29  | A9          | 81  | MPIO13      | 133 | D8          | 185 | PA18        |

| 30  | VDDIO       | 82  | MPIO14      | 134 | D7          | 186 | PA17        |

| 31  | A10         | 83  | MPIO15      | 135 | GND         | 187 | PA16        |

| 32  | A11         | 84  | PA4         | 136 | D6          | 188 | PA15        |

| 33  | A12         | 85  | NWR3        | 137 | VDDIO       | 189 | PA14        |

| 34  | A13         | 86  | PA5         | 138 | D5          | 190 | PA13        |

| 35  | A14         | 87  | MPIO24      | 139 | MPIO29      | 191 | PA12        |

| 36  | VDDCORE     | 88  | GND         | 140 | GND         | 192 | PA11        |

| 37  | GND         | 89  | MPIO25      | 141 | MPIO30      | 193 | GND         |

| 38  | GND         | 90  | PA6         | 142 | MPIO31      | 194 | VDDCORE     |

| 39  | CAS         | 91  | MPIO26      | 143 | MPIO57      | 195 | GND         |

| 40  | A15         | 92  | PA7         | 144 | VDDCORE     | 196 | NWR1        |

| 41  | RAS         | 93  | MPIO27      | 145 | MPIO58      | 197 | NRD         |

| 42  | A16         | 94  | VDDIO       | 146 | GND         | 198 | VDDIO       |

| 43  | SDA10       | 95  | MPIO45      | 147 | MPIO59      | 199 | VDDPLLB     |

| 44  | VDDIO       | 96  | VDDCORE     | 148 | DDM         | 200 | GNDPLLB     |

| 45  | A17         | 97  | MPIO46      | 149 | DDP         | 201 | GNDOSC      |

| 46  | A18         | 98  | PA8         | 150 | MPIO60      | 202 | XIN         |

| 47  | A19         | 99  | PA9         | 151 | VDDIO       | 203 | XOUT        |

| 48  | A20         | 100 | GND         | 152 | D4          | 204 | VDDOSC      |

| 49  | A21         | 101 | PA10        | 153 | D3          | 205 | VDDPLLA     |

| 50  | GND         | 102 | NCS3        | 154 | D2          | 206 | GNDPLLA     |

| 51  | A22         | 103 | NCS0        | 155 | D1          | 207 | PLLRCA      |

| 52  | MPIO00      | 104 | BMS         | 156 | D0          | 208 | GNDPLLA     |

# 4.6 Mechanical Overview of the 176-pin LQFP Package

Figure 4-3 shows the orientation of the 176-pin LQFP Package. A detailed mechanical description is given in the Mechanical Characteristics section of the product datasheet.

### Figure 4-3. 176-pin LQFP Pinout (Top View)

# 4.7 176-pin LQFP Package Pinout

Warning: The package pinout is preliminary and is subject to change.

| ı  | Signal Name | Pin | Signal Name | Pin | Signal Name | Pin | Signal Nam |

|----|-------------|-----|-------------|-----|-------------|-----|------------|

|    | NTRST       | 45  | MPIO01      | 89  | A7          | 133 | VDDOSC32   |

| 2  | TDI         | 46  | MPIO02      | 90  | GND         | 134 | XIN32      |

| 3  | TDO         | 47  | VDDIO       | 91  | VDDIO       | 135 | XOUT32     |

| 4  | TMS         | 48  | GND         | 92  | A6          | 136 | GNDOSC32   |

| 5  | тск         | 49  | MPIO03      | 93  | A5          | 137 | VDDBU      |

| 6  | GND         | 50  | MPIO04      | 94  | VDDCORE     | 138 | SHDW       |

| 7  | VDDIO       | 51  | MPIO05      | 95  | A4          | 139 | WKUP0      |

| 8  | NRST        | 52  | MPIO06      | 96  | GND         | 140 | JTAGSEL    |

| 9  | NWR0        | 53  | MPIO07      | 97  | A3          | 141 | TST        |

| 10 | PA0         | 54  | GND         | 98  | SDRAMCKE    | 142 | GNDBU      |

| 11 | MPIO16      | 55  | VDDIO       | 99  | A2          | 143 | ADVREF     |

| 12 | PA1         | 56  | MPIO20      | 100 | SDWE        | 144 | MPIO82/AD  |

| 13 | MPIO17      | 57  | MPIO8       | 101 | VDDIO       | 145 | MPIO83/AD  |

| 14 | VDDCORE     | 58  | MPIO21      | 102 | SDRAMCLK    | 146 | MPIO84/AD  |

| 15 | MPIO18      | 59  | MPIO09      | 103 | A1          | 147 | MPIO85/AD  |

| 16 | GND         | 60  | MPIO22      | 104 | MPIO28      | 148 | MPIO86/AD  |

| 17 | MPIO19      | 61  | MPIO10      | 105 | GND         | 149 | MPIO87/AD  |

| 18 | PA2         | 62  | MPIO23      | 106 | A0          | 150 | MPIO88/AD  |

Table 4-4.

AT91CAP7 Pinout for 176-pin LQFP Package

| Table 4-4. | AT91CAP7 Pinout for 176-pin LQFP Package (Continued) |

|------------|------------------------------------------------------|

|------------|------------------------------------------------------|

| Pin | Signal Name |

|-----|-------------|-----|-------------|-----|-------------|-----|-------------|

| 19  | PA3         | 63  | VDDCORE     | 107 | D15         | 151 | MPIO89/AD7  |

| 20  | A8          | 64  | MPIO11      | 108 | D14         | 152 | AVDD        |

| 21  | A9          | 65  | GND         | 109 | D13         | 153 | AGND        |

| 22  | VDDIO       | 66  | MPIO12      | 110 | D12         | 154 | GND         |

| 23  | A10         | 67  | MPIO13      | 111 | D11         | 155 | VDDIO       |

| 24  | A11         | 68  | MPIO14      | 112 | D10         | 156 | GND         |

| 25  | A12         | 69  | MPIO15      | 113 | D9          | 157 | NCS1        |

| 26  | A13         | 70  | PA4         | 114 | D8          | 158 | VDDCORE     |

| 27  | A14         | 71  | NWR3        | 115 | D7          | 159 | PA12        |

| 28  | VDDCORE     | 72  | PA5         | 116 | GND         | 160 | PA11        |

| 29  | GND         | 73  | MPIO24      | 117 | D6          | 161 | GND         |

| 30  | CAS         | 74  | GND         | 118 | D5          | 162 | VDDCORE     |

| 31  | A15         | 75  | MPIO25      | 119 | MPIO29      | 163 | GND         |

| 32  | RAS         | 76  | PA6         | 120 | GND         | 164 | NWR1        |

| 33  | A16         | 77  | MPIO26      | 121 | MPIO30      | 165 | NRD         |

| 34  | SDA10       | 78  | PA7         | 122 | MPIO31      | 166 | VDDIO       |

| 35  | VDDIO       | 79  | MPIO27      | 123 | VDDCORE     | 167 | VDDPLLB     |

| 36  | MPIO32      | 80  | VDDIO       | 124 | GND         | 168 | GNDPLLB     |

| 37  | A17         | 81  | VDDCORE     | 125 | DDM         | 169 | GNDOSC      |

| 38  | A18         | 82  | PA8         | 126 | DDP         | 170 | XIN         |

| 39  | A19         | 83  | PA9         | 127 | VDDIO       | 171 | XOUT        |

| 40  | A20         | 84  | GND         | 128 | D4          | 172 | VDDOSC      |

| 41  | A21         | 85  | PA10        | 129 | D3          | 173 | VDDPLLA     |

| 42  | GND         | 86  | NCS3        | 130 | D2          | 174 | GNDPLLA     |

| 43  | A22         | 87  | NCS0        | 131 | D1          | 175 | PLLRCA      |

| 44  | MPIO00      | 88  | BMS         | 132 | D0          | 176 | GNDPLLA     |

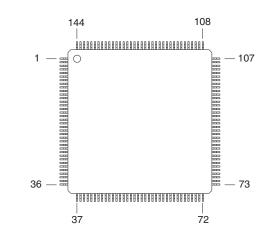

## 4.8 Mechanical Overview of the 144-pin LQFP Package

Figure 4-4 shows the orientation of the 144-pin LQFP Package. A detailed mechanical description is given in the Mechanical Characteristics section of the product datasheet.

#### **Figure 4-4.** 144-pin LQFP Pinout (Top View)

### 4.9 144-pin LQFP Package Pinout

Warning: This package pinout is preliminary and is subject to change.

Table 4-5.

AT91CAP7 Pinout for 144-pin LQFP Package

| Pin | Signal Name | Pin | Signal Name | Pin | Signal Name | Pin | Signal Nam |

|-----|-------------|-----|-------------|-----|-------------|-----|------------|

| 1   | NTRST       | 37  | MPIO01      | 73  | A7          | 109 | VDDOSC32   |

| 2   | TDI         | 38  | MPIO02      | 74  | GND         | 110 | XIN32      |

| 3   | TDO         | 39  | VDDIO       | 75  | VDDIO       | 111 | XOUT32     |

| 4   | TMS         | 40  | GND         | 76  | A6          | 112 | GNDOSC32   |

| 5   | тск         | 41  | MPIO03      | 77  | A5          | 113 | VDDBU      |

| 6   | GND         | 42  | MPIO04      | 78  | VDDCORE     | 114 | SHDW       |

| 7   | VDDIO       | 43  | MPIO05      | 79  | A4          | 115 | WKUP0      |

| 8   | NRST        | 44  | MPIO06      | 80  | GND         | 116 | JTAGSEL    |

| 9   | NWR0        | 45  | MPIO07      | 81  | A3          | 117 | TST        |

| 10  | PA0         | 46  | GND         | 82  | A2          | 118 | GNDBU      |

| 11  | PA1         | 47  | VDDIO       | 83  | VDDIO       | 119 | ADVREF     |

| 12  | VDDCORE     | 48  | MPIO8       | 84  | A1          | 120 | MPIO82/AD  |

| 13  | GND         | 49  | MPIO09      | 85  | GND         | 121 | MPIO83/AD  |

| 14  | PA2         | 50  | MPIO10      | 86  | A0          | 122 | MPIO84/AD  |

| 15  | PA3         | 51  | VDDCORE     | 87  | D15         | 123 | MPIO85/AD  |

| 16  | A8          | 52  | MPIO11      | 88  | D14         | 124 | AVDD       |

| 17  | A9          | 53  | GND         | 89  | D13         | 125 | AGND       |

| 18  | VDDIO       | 54  | MPIO12      | 90  | D12         | 126 | GND        |

| 19  | A10         | 55  | MPIO13      | 91  | D11         | 127 | VDDIO      |

| Pin | Signal Name |

|-----|-------------|-----|-------------|-----|-------------|-----|-------------|

| 20  | A11         | 56  | MPIO14      | 92  | D10         | 128 | GND         |

| 21  | A12         | 57  | MPIO15      | 93  | D9          | 129 | VDDCORE     |

| 22  | A13         | 58  | PA4         | 94  | D8          | 130 | GND         |

| 23  | A14         | 59  | NWR3        | 95  | D7          | 131 | VDDCORE     |

| 24  | VDDCORE     | 60  | PA5         | 96  | D6          | 132 | NWR1        |

| 25  | GND         | 61  | GND         | 97  | D5          | 133 | NRD         |

| 26  | A15         | 62  | PA6         | 98  | GND         | 134 | VDDIO       |

| 27  | A16         | 63  | PA7         | 99  | VDDCORE     | 135 | VDDPLLB     |

| 28  | VDDIO       | 64  | VDDIO       | 100 | GND         | 136 | GNDPLLB     |

| 29  | A17         | 65  | VDDCORE     | 101 | DDM         | 137 | GNDOSC      |

| 30  | A18         | 66  | PA8         | 102 | DDP         | 138 | XIN         |

| 31  | A19         | 67  | PA9         | 103 | VDDIO       | 139 | XOUT        |

| 32  | A20         | 68  | GND         | 104 | D4          | 140 | VDDOSC      |

| 33  | A21         | 69  | PA10        | 105 | D3          | 141 | VDDPLLA     |

| 34  | GND         | 70  | NCS3        | 106 | D2          | 142 | GNDPLLA     |

| 35  | A22         | 71  | NCS0        | 107 | D1          | 143 | PLLRCA      |

| 36  | MPIO00      | 72  | BMS         | 108 | D0          | 144 | GNDPLLA     |

Table 4-5.

AT91CAP7 Pinout for 144-pin LQFP Package (Continued)

# 5. Power Considerations

### 5.1 **Power Supplies**

The AT91CAP7 has several types of power supply pins:

- VDDCORE pins: Power the core, including the processor, the embedded memories and the peripherals; voltage ranges from 1.08V and 1.32V (1.2V nominal). The associated ground pins for this supply and the VDDIO supply are the GND pins.

- VDDIO pins: Power the non-backup I/O lines; voltage ranges between 3.0V and 3.6V (3.3V nominal). The associated ground pins for this supply and the VDDCORE supply are the GND pins.

- VDDBU pin: Powers the RC oscillator, Backup I/O and part of the System Controller; voltage ranges from 1.08V and 1.32V, (1.2V nominal). The associated ground pin for this supply is the GNDBU pin. Required for all operational modes.

- VDDPLLA pin: Powers the PLLA cell; voltage ranges from 3.0V and 3.6V (3.3V nominal). The associated ground pin for this supply is the GNDPLLA pin.

- VDDPLLB pin: Powers the PLLB cell and related internal loop filter cell; voltage ranges from 1.08V and 1.32V (1.2V nominal). The associated ground pin for this supply is the GNDPLLB pin.

- VDDOSC pins: Powers the Main Oscillator cell; voltage ranges from 1.08V and 1.32V (1.2V nominal). The associated ground pin for this supply is the GNDOSC pin.

- VDDOSC32 pins: Powers the 32 kHz oscillator cell; voltage ranges from 1.08V and 1.32V (1.2V nominal). The associated ground pin for this supply is the GNDOSC32 pin. Required for all operational modes.

- AVDD pin: Powers the 10-bit Analog to Digital Converter and associated cells; voltage ranges from 3.0V and 3.6V (3.3V nominal). The associated ground pin for this supply is the AGND pin.

### 5.2 **Power Consumption**

Note: The following figures are preliminary figures based on prototype silicon. They are subject to change for the production silicon.

The AT91CAP7 consumes about 600  $\mu$ A of static current on VDDCORE at typical conditions (1.2V, 25°C).

On VDDBU, the current does not exceed 30 µA at typical conditions.

For dynamic power consumption, the AT91CAP7 consumes about 0.33 mW/MHz of power or 275  $\mu$ A/MHz of current on VDDCORE at typical conditions (1.2V, 25°C) and with the ARM subsystem running full-performance algorithm with on-chip memories, and no peripherals active.

### 5.3 Power Supply Isolation

All power supplies must be active in normal operation. CAP7 supports a low power backup mode in which most of the core including the processor can be powered down. In backup mode, it is mandatory to keep VDDBU and VDDOSC32 active; all other supplies must be inactive.

# 6. I/O Line Considerations

### 6.1 JTAG Port Pins

TMS and TDI are Schmitt trigger inputs with pull-up resistors. TCK is a Schmitt trigger input with pull-down resistor.

TDO is an output, driven at up to VDDIO, with a pull-up resistor.

The JTAGSEL pin is used to select the JTAG boundary scan when asserted at a high level. It integrates a permanent pull-down resistor of about 100kohm to GNDBU, so that it can be left unconnected for normal operations.

The NTRST signal is described in the Reset Pins paragraph. JTAGSEL is supplied with VDDBU, all other JTAG signals are supplied with VDDIO.

### 6.2 Test Pin

The TST pin is used for manufacturing test purposes when asserted high. It integrates a permanent pull-down resistor of about 100 k $\Omega$  to GNDBU, so that it can be left unconnected for normal operations. Driving this line at a high level leads to unpredictable results.

This pin is supplied with VDDBU.

### 6.3 Reset Pins

NRST is an open-drain output integrating a non-programmable pull-up resistor. It can be driven with voltage at up to VDDIO.

NTRST is an input which allows reset of the JTAG Test Access port. It has no action on the processor for both ARM core and boundary scan.

As the product integrates power-on reset cells, which manages the processor and the JTAG reset, the NRST and NTRST pins can be left unconnected.

The NRST and NTRST pins both integrate a permanent pull-up resistor of 100 k $\Omega$  minimum to VDDIO.

### 6.4 PIO Controllers

All the I/O lines which are managed by a PIO Controller integrate a programmable pull-up resistor of 100 k $\Omega$  minimum. Programming of this pull-up resistor is performed independently for each I/O line through the PIO Controllers.

After reset, all the I/O lines default as inputs with pull-up resistors enabled, except those which are multiplexed with the External Bus Interface signals that must be enabled as Peripheral at reset. This is explicitly indicated in the column "Reset State" of the PIO Controller multiplexing tables.

### 6.5 Shut Down Logic pins

The SHDW pin is an output only, which is driven by the Shut Down Controller only at low level. It can be tied high with an external pull-up resistor at VDDBU only.

# 7. Processor and Architecture

### 7.1 ARM7TDMI Processor

- RISC Processor Based on ARMv4T Von Neumann Architecture

- Runs at up to 80 MHz, providing up to 72 MIPS

- Two instruction sets

- ARM high-performance 32-bit Instruction Set

- Thumb high code density 16-bit Instruction Set

- Three-stage pipeline architecture

- Instruction Fetch (F)

- Instruction Decode (D)

- Execute (E)

#### 7.2 Debug and Test Features

- Integrated embedded in-circuit emulator

- Two watchpoint units

- Test access port accessible through a JTAG protocol

- Debug communication channel

- Debug Unit

- Two-pin UART

- Debug communication channel interrupt handling

- Chip ID and EXTended Chip ID Register

- · IEEE1149.1 JTAG Boundary-scan on all digital pins, except reset, backup reset, and test pins

#### 7.3 Bus Matrix

- · 6 Layers Matrix, handling requests from 6 masters

- Programmable Arbitration strategy

- Fixed-priority Arbitration

- Round-Robin Arbitration, either with no default master, last accessed default master or fixed default master

- Burst Management

- Breaking with Slot Cycle Limit Support

- Undefined Burst Length Support

- One Address Decoder provided per Master

- Three different slaves may be assigned to each decoded memory area: one for internal boot, one for external boot, one after remap

- Boot Mode Select

- Non-volatile Boot Memory can be internal or external

- Selection is made by BMS pin sampled at reset

- Remap Command

- Allows Remapping of an Internal SRAM in Place of the Boot Non-Volatile Memory

- Allows Handling of Dynamic Exception Vectors

#### 7.3.1 Matrix Masters

The Bus Matrix of the AT91CAP7 manages six Masters, which means that each master can perform an access concurrently with others, as long as the slave it accesses is available.

Each Master has its own decoder, which is defined specifically for each master. In order to simplify the addressing, all the masters have the same decoding. There are four independent masters available for the Metal Programmable Block (MP Block).

| Table 7-1. | List of | Bus | Matrix | Masters |

|------------|---------|-----|--------|---------|

|------------|---------|-----|--------|---------|

| Master 0 | ARM7TDMI                  |

|----------|---------------------------|

| Master 1 | Peripheral DMA Controller |

| Master 2 | MP Block Master A         |

| Master 3 | MP Block Master B         |

| Master 4 | MP Block Master C         |

| Master 5 | MP Block Master D         |

#### 7.3.2 Matrix Slaves

The Bus Matrix of the AT91CAP7 manages ten Slaves. Each Slave has its own arbiter, thus allowing to program a different arbitration per Slave.

There are four independent slaves available for the Metal Programmable Block (MP Block).

| Slave 0 | Internal SRAM 96 Kbytes                        |

|---------|------------------------------------------------|

| Slave 1 | Internal SRAM 64 Kbytes                        |

| Slave 2 | Internal ROM 256 Kbytes                        |

| Slave 3 | MP Block Slave A                               |

| Slave 4 | MP Block Slave B                               |

| Slave 5 | MP Block Slave C                               |

| Slave 6 | MP Block Slave D                               |

| Slave 7 | MP Block Slave for ARM control of AHB masters* |

| Slave 8 | External Bus Interface                         |

| Slave 9 | Peripheral Bridge                              |

Table 7-2.List of Bus Matrix Slaves

\* **Note:** Slave7 may only be accessed by the ARM7TDMI master and can be used to access control and status registers for AHB master devices in the metal programmable block that do not also have APB connections for this purpose.

#### 7.4 Peripheral DMA Controller

- Acting as one Matrix Master

- Allows data transfers from/to peripheral to/from any memory space without any intervention of the processor.

- · Next Pointer Support, avoids strong real-time constraints on buffer management.

- 22 channels

- Two for each USART

- Two for the Debug Unit

- Two for the Serial Peripheral Interface

- One for the Analog to Digital Converter (ADC)

- 13 for peripherals implemented in the Metal Programmable Block

## 8. Memories

#### 8.1 Embedded Memories

- · 256 Kbyte Fast ROM

- Single Cycle Access at full matrix speed

- 96 Kbyte Fast SRAM

- Single Cycle Access at full matrix speed

- 64 Kbyte Fast SRAM

- Single Cycle Access at full matrix speed

- Two 4 Kbyte DPRAMs

- Accessed from the Metal Programmable Block

### 8.2 Memory Mapping

A first level of address decoding is performed by the Bus Matrix, i.e., the implementation of the Advanced High performance Bus (AHB) for its Master and Slave interfaces with additional features.

Decoding breaks up the 4G bytes of address space into 16 banks of 256M bytes. The banks 1 to 9 are directed to the EBI that associates these banks to the external chip selects NCS0 to NCS7. The bank 0 is reserved for the addressing of the internal memories, and a second level of decoding provides 1M byte of internal memory area. The bank 15 is reserved for the peripherals and provides access to the Advanced Peripheral Bus (APB).

Other areas are unused and performing an access within them provides an abort to the master requesting such an access.

#### Figure 8-1. AT91CAP7 Product Memory Mapping

| 256M Bytes                     | 0x0000 0000<br>0x0FFF FFFF | Internal Memories                            |

|--------------------------------|----------------------------|----------------------------------------------|

| 8 x 256M Bytes<br>2,048M bytes | 0x1000 0000<br>0x8FFF FFFF | External Bus Interface<br>Chip Select 0 to 7 |

| 6 x 256M Bytes<br>1,536M Bytes | 0x9000 0000                | Undefined<br>(Abort)                         |

|                                | 0xEFFF FFFF                |                                              |

| 256M Bytes                     | 0xF000 0000<br>0xFFFF FFFF | Internal Peripherals                         |

Each Master has its own bus and its own decoder, thus allowing a different memory mapping per Master. However, in order to simplify the mappings, all the masters have a similar address decoding.

Regarding Master 0 (ARM7TDMI), two different Slaves are assigned to the memory space decoded at address 0x0: one for internal boot and one for external boot.

### 8.3 Internal Memory Mapping

#### 8.3.1 Internal 160-kBytes Fast SRAM

The AT91CAP7 embeds 160-Kbytes of high-speed SRAM configured in blocks of 96 KB and 64KB. When accessed from the AHB, each SRAM block is independently single cycle accessible at full matrix speed (MCK).

#### 8.3.2 Boot Memory

The remappable memory area is between 0x0 and 0x000F FFFF.

If BMS is detected at logic 0, the boot memory is the memory connected on the Chip Select 0 of the External Bus Interface. The default configuration for the Static Memory Controller, byte select mode, 16-Bit data bus, Read/Write controlled by Chip Select, allows the device to boot on 16Bit nonvolatile memory.

If BMS is detected at logic 1, the boot memory is the embedded ROM.

#### 8.4 Boot Program

The internal 256 KB ROM is metal-programmable and each AT91CAP7 customer may develop their own boot program using their own code or a combination of their own code and routines available from Atmel.

#### 8.5 External Memories Mapping

The external memories are accessed through the External Bus Interface. Each Chip Select line has a 256-MByte memory area assigned.

#### Figure 8-2. AT91CAP7 External Memory Mapping

| 256M Bytes | 0x1000 0000 | Bank 0   | EBI NCS0    |                  |

|------------|-------------|----------|-------------|------------------|

|            | 0x1FFF FFFF | bunko    |             |                  |

| 256M Bytes | 0x2000 0000 | Bank 1   | EBI_NCS1 or |                  |

| 250W Bytes | 0x2FFF FFFF | Dank i   | EBI_SDCS    |                  |

|            | 0x3000 0000 | Bank 2   |             |                  |

| 256M Bytes | 0x3FFF FFFF | DdHK Z   | EBI_NCS2    |                  |

| 1          | 0x4000 0000 | Devela 2 |             | SmartMedia or    |

| 256M Bytes | 0x4FFF FFFF | Bank 3   | EBI_NCS3    | NAND Flash EBI   |

|            | 0x5000 0000 | Davila 4 |             | CompactFlash EBI |

| 256M Bytes | 0x5FFF FFFF | Bank 4   | EBI_NCS4    | Slot 0           |

| 25 CM D. + | 0x6000 0000 | Davida C |             | CompactFlash EBI |

| 256M Bytes | 0x6FFF FFFF | Bank 5   | EBI_NCS5    | Slot 1           |

|            | 0x7000 0000 |          |             |                  |

| 256M Bytes | 0x7FFF FFFF | Bank 6   | EBI_NCS6    |                  |

| <b>-</b>   | 0x8000 0000 |          | EBI NCS7    |                  |

| 256M Bytes | 0x8FFF FFFF | Bank 7   | 201(05)     |                  |

### 8.6 External Bus Interface

- Optimized for Application Memory Space support

- · Integrates two External Memory Controllers:

- Static Memory Controller

- SDRAM Controller

- Additional logic for NANDFlash and CompactFlash<sup>™</sup>

- Optional Full 32-bit External Data Bus

- Up to 26-bit Address Bus (up to 64MBytes linear per chip select)

- Up to 6 chips selects, Configurable Assignment:

- Static Memory Controller on NCS0

- SDRAM Controller or Static Memory Controller on NCS1

- Static Memory Controller on NCS2

- Static Memory Controller on NCS3, Optional NAND Flash support

- Static Memory Controller on NCS4 NCS5, Optional CompactFlash<sup>M</sup> support

### 8.6.1 Static Memory Controller

- 8-, 16- or 32-bit Data Bus

- Multiple Access Modes supported

- Byte Write or Byte Select Lines

- Asynchronous read in Page Mode supported (4- up to 32-byte page size)

- · Multiple device adaptability

- Compliant with LCD Module

- Control signals programmable setup, pulse and hold time for each Memory Bank

- Multiple Wait State Management

- Programmable Wait State Generation

- External Wait Request

- Programmable Data Float Time

- Slow Clock mode supported

#### 8.6.2 SDRAM Controller

- Supported devices:

- Standard SDRAM

- Numerous configurations supported

- 2K, 4K, 8K Row Address Memory Parts

- SDRAM with two or four Internal Banks

- SDRAM with 16- or 32-bit Data Path

- Programming facilities

- Word, half-word, byte access

- Automatic page break when Memory Boundary has been reached

- Multi-bank Ping-pong Access

- Timing parameters specified by software

- Automatic refresh operation, refresh rate is programmable

- Energy-saving capabilities

- Self-refresh, power down and deep power down modes supported

- Error detection

- Refresh Error Interrupt

- SDRAM Power-up Initialization by software

- CAS Latency of 1, 2 and 3 supported

- Auto Precharge Command not used

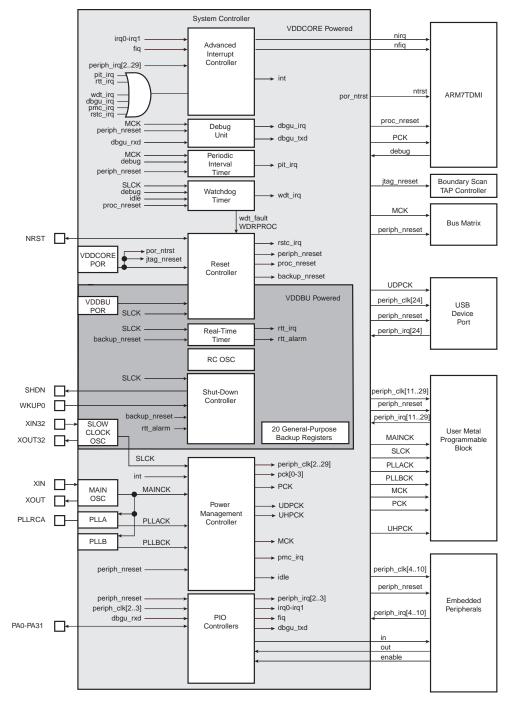

# 9. System Controller

The System Controller is a set of peripherals, which allow handling of key elements of the system, such as power, resets, clocks, time, interrupts, watchdog, etc.

The System Controller User Interface also includes control registers for configuring the AHB Matrix and the chip configuration. The chip configuration registers allow setting the EBI chip select assignment for external memories.

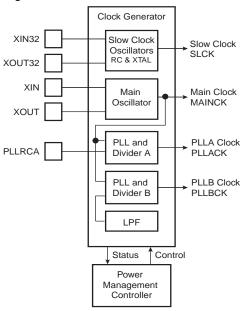

# 9.1 System Controller Block Diagram

### 9.2 System Controller Mapping

The System Controller's peripherals are all mapped within the highest 16K bytes of address space, between addresses 0xFFFF C000 and 0xFFFF FFFF.

However, all the registers of System Controller are mapped on the top of the address space. This allows addressing all the registers of the System Controller from a single pointer by using the standard ARM instruction set since the Load/Store instructions have an indexing mode of +/-4kbytes. Figure 9-2 shows where the User Interfaces for the System Controller peripherals fit into the memory map (relative to bus matrix and EBI (SMC, SDRAMC).

| Figure 9-2. | System Controller Ma              | pping        |                                            |                                     |

|-------------|-----------------------------------|--------------|--------------------------------------------|-------------------------------------|

|             | 0xFFFF C000                       |              | Peripheral Name                            | Size                                |

|             | ł                                 | Reserved     |                                            |                                     |

|             | 0xFFFF E9FF                       |              |                                            |                                     |

|             | 0xFFFF EA00                       | SDRAMC       | SDRAM Controller                           | 512 bytes/128 words                 |

|             | 0xFFFF EBFF                       |              |                                            |                                     |

|             | 0xFFFF EC00                       | SMC          | Static Memory Controller                   | 512 bytes/128 words                 |

|             | 0xFFFF EDFF<br>0xFFFF EE00        |              |                                            | ,                                   |

|             |                                   | MATRIX       | Matrix                                     | 512 bytes/128 words                 |

|             | 0xFFFF EFFF<br>0xFFFF F000        |              |                                            |                                     |

|             |                                   | AIC          | Advanced Interrupt Controller              | 512 bytes/128 words                 |

|             | 0xFFFF F1FF<br><b>0xFFFF F200</b> |              |                                            |                                     |

|             |                                   | DBGU         | Debug Unit                                 | 512 bytes/128 words                 |

|             | 0xFFFF F3FF<br><b>0xFFFF F400</b> |              |                                            |                                     |

|             |                                   | PIOA         | Parallel I/O Controller A                  | 512 bytes/128 words                 |

|             | 0xFFFF F5FF<br><b>0xFFFF F600</b> | DIOD         |                                            | 540 h. to a /400                    |

|             |                                   | PIOB         | Parallel I/O Controller B                  | 512 bytes/128 words                 |

|             | 0xFFFF F7FF<br><b>0xFFFF F800</b> |              |                                            |                                     |

|             |                                   | Deserved     | Deserved                                   |                                     |

|             |                                   | Reserved     | Reserved                                   |                                     |

|             | 0xFFFF FBFF                       |              |                                            |                                     |

|             | 0xFFFF FC00                       | PMC          | Power Management Controller                | 512 bytes/128 words                 |

|             | 0xFFFF FCFF<br><b>0xFFFF FD00</b> | 0070         |                                            |                                     |

|             | 0xFFFF FD10                       | RSTC         | Reset Controller                           | 16 bytes/4 words                    |

|             | 0xFFFF FD20                       | SHDC         | Shut-Down Controller                       | 16 bytes/4 words                    |

|             | 0xFFFF FD30                       | RTT          | Real-Time Timer<br>Periodic Interval Timer | 16 bytes/4 words                    |

|             | 0xFFFF FD40                       | PIT          |                                            | 16 bytes/4 words                    |

|             | 0xFFFF FD50                       | WDT<br>OSCMR | Watchdog Timer<br>Oscillator Mode Register | 16 bytes/4 words<br>2 bytes/1 words |

|             | 0xFFFF FD60                       | USCIVIN      | Oscillator Mode Register                   | (3words reserved)                   |

|             |                                   | GPBR         | General-Purpose Backup Registers           | 80 bytes/20 words                   |

|             | 0xFFFF FDB0                       |              |                                            |                                     |

|             |                                   | Reserved     | Reserved                                   |                                     |

|             | 0xFFFF FFFF                       | Ť            |                                            |                                     |

|             |                                   |              |                                            |                                     |

### 9.3 Reset Controller

- Based on two Power-on-Reset cells

- one on VDDBU and one on VDDCORE

- Status of the last reset

- Either general reset (VDDBU rising), wake-up reset (VDDCORE rising), software reset, user reset or watchdog reset

- · Controls the internal resets and the NRST pin output

- Allows shaping a reset signal for the external devices

### 9.4 Shut Down Controller

- Shut-Down and Wake-Up logic

- Software programmable assertion of the SHDW open-drain pin

- De-assertion Programmable on a WKUP0 pin level change or on alarm

### 9.5 Clock Generator

- Embeds the Low Power, fast start-up 32kHz RC Oscillator

- Provides the default Slow Clock SLCK to the system

- The SLCK is required for AT91CAP7 to start-up because it is the default clock for the ARM7TDMI at power-up.

- Embeds the Low Power 32768Hz Slow Clock Oscillator

- Requires an external 32768Hz crystal

- Optional Slow Clock SLCK source when a real-time timebase is required

- Embeds the Main Oscillator

- Requires an external crystal. For systems using the USB features, 12MHz is recommended.

- Oscillator bypass feature

- Supports 8 to 16MHz crystals. 12 MHz crystal is required if using the USB features of AT91CAP7.

- Generates input reference clock for the two PLLs.

- Embeds PLLA primarily for generating processor and master clocks. For full-speed operation on the ARM7TDMI processor, this PLL should be programmed to generate a 160 MHz clock that must then be divided in half to generate the 80 MHz PCK and related clocks.

- PLLA outputs an 80 to 240MHz clock

- Requires an external RC filter network

- PLLA has a 1MHz minimum input frequency

- Integrates an input divider to increase output accuracy

- Embeds PLLB primarily for generating a 96 MHz clock that is divided down to generate the USB related clocks.

- PLLB and its internal low-pass filter (LPF) are tuned especially for generating a 96 MHz clock with a 12 MHz input frequency

- 12 MHz minimum input frequency

- Integrates an input divider to increase output accuracy

#### Figure 9-3. Clock Generator Block Diagram

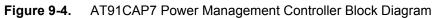

### 9.6 Power Management Controller

- The Power Management Controller provides the following clocks as shown in Figure 7 below:

- the Processor Clock PCK

- the Master Clock MCK, in particular to the Matrix and the memory interfaces

- the USB Device Clock UDPCK

- independent peripheral clocks (periph\_clk), typically at the frequency of MCK

- four programmable clock outputs: PCK0 to PCK3

- · Five flexible operating modes:

- Normal Mode, processor and peripherals running at a programmable frequency

- Idle Mode, processor stopped waiting for an interrupt

- Slow Clock Mode, processor and peripherals running at low frequency

- Standby Mode, mix of Idle and Backup Mode, peripheral running at low frequency, processor stopped waiting for an interrupt

- Backup Mode, Main Power Supplies off, VDDBU and VDDOSC32 on

### 9.7 Periodic Interval Timer

- Includes a 20-bit Periodic Counter

- Includes a 12-bit Interval Overlay Counter

- Real Time OS or Linux/WinCE compliant tick generator

### 9.8 Watchdog Timer

- 16-bit key-protected only-once-Programmable Counter

- Windowed, prevents the processor to be in a dead-lock on the watchdog access

### 9.9 Real-Time Timer

- · One Real-Time Timer, allowing backup of time

- 32-bit Free-running, back-up Counter

- Integrates a 16-bit programmable prescaler running on the embedded 32.768Hz oscillator

- Alarm Register capable to generate a wake-up of the system through the Shut Down Controller

### 9.10 General-Purpose Backed-up Registers

• Twenty 32-bit backup general-purpose registers

#### 9.11 Advanced Interrupt Controller

- · Controls the interrupt lines (nIRQ and nFIQ) of the ARM Processor

- Thirty-two individually maskable and vectored interrupt sources

- Source 0 is reserved for the Fast Interrupt Input (FIQ)

- Source 1 is reserved for system peripherals (PIT, RTT, PMC, DBGU, etc.)

- Programmable Edge-triggered or Level-sensitive Internal Sources

- Programmable Positive/Negative Edge-triggered or High/Low Level-sensitive

- Two External Sources plus the Fast Interrupt signal

- 8-level Priority Controller

- Drives the Normal Interrupt of the processor

- Handles priority of the interrupt sources 1 to 31

- Higher priority interrupts can be served during service of lower priority interrupt

- Vectoring

- Optimizes Interrupt Service Routine Branch and Execution

- One 32-bit Vector Register per interrupt source

- Interrupt Vector Register reads the corresponding current Interrupt Vector

- Protect Mode

- Easy debugging by preventing automatic operations when protect models are enabled

- Fast Forcing

- Permits redirecting any normal interrupt source on the Fast Interrupt of the processor

#### 9.12 Debug Unit

- Composed of two functions

- Two-pin UART

- Debug Communication Channel (DCC) support

- Two-pin UART

- Implemented features are 100% compatible with the standard Atmel USART

- Independent receiver and transmitter with a common programmable Baud Rate Generator

- Even, Odd, Mark or Space Parity Generation

- Parity, Framing and Overrun Error Detection

- Automatic Echo, Local Loopback and Remote Loopback Channel Modes

- Support for two PDC channels with connection to receiver and transmitter

- Debug Communication Channel Support

- Offers visibility of and interrupt trigger from COMMRX and COMMTX signals from the ARM Processor's ICE Interface

### 9.13 Chip Identification

Chip ID: 837709xx (0x1000 0011 0111 0111 0000 1001 010x xxxx). This value is stored in the Chip ID Register (DBGU\_CIDR) in the Debug Unit. The last 5 bits of the register are reserved for a chip version number.