Sample &

Buy

TEXAS INSTRUMENTS

# LMV710-N, LMV711-N, LMV715-N

SNOS519K - APRIL 2000 - REVISED AUGUST 2016

# LMV71x-N Low-Power, RRIO Operational Amplifiers With High Output Current Drive and Shutdown Option

# 1 Features

- Low Offset Voltage: 3 mV (Maximum)

- Gain-Bandwidth Product: 5 MHz (Typical)

- Slew Rate: 5 V/µs (Typical)

- Space-Saving Packages: 5-Pin and 6-Pin SOT-23

- Turnon Time From Shutdown: <10 μs

- Industrial Temperature Range: -40°C to 85°C

- Supply Current in Shutdown Mode: 0.2 µA (Typical)

- Ensured 2.7-V and 5-V Performance

- Unity Gain Stable

- Rail-to-Rail Input and Output

- Capable of Driving  $600-\Omega$  Load

# 2 Applications

- Wireless Phones

- GSM, TDMA, and CDMA Power Amp Controls

- AGC and RF Power Detectors

- Temperature Compensation

- Wireless LAN

- Bluetooth

- HomeRF

# 3 Description

The LMV710-N, LMV711-N, and LMV715-N are BiCMOS operational amplifiers with a CMOS input stage. These devices have greater than RR input common mode voltage range, rail-to-rail output and high output current drive. They offer a bandwidth of 5 MHz and a slew rate of 5 V/ $\mu$ s.

On the LMV711 and LMV715, a separate shutdown pin can be used to disable the device and reduces the supply current to 0.2  $\mu$ A (typical). They also feature a turnon time of less than 10  $\mu$ s. It is an ideal solution for power-sensitive applications, such as cellular phone, pager, palm computer, and so forth. In addition, once the LMV715 is in shutdown the output is tri-stated.

The LMV710 is offered in the space-saving, 5-pin SOT-23 package. The LMV711 and LMV715 are offered in the space saving 6-pin SOT-23 package.

The LMV71x-N devices are designed to meet the demands of low power, low cost, and small size required by cellular phones and similar battery-powered portable electronics.

| Device | Information <sup>(1)</sup> |

|--------|----------------------------|

|--------|----------------------------|

| PART NUMBER          | PACKAGE    | BODY SIZE (NOM)   |

|----------------------|------------|-------------------|

| LMV710-N             | SOT-23 (5) | 2.92 mm × 1.50 mm |

| LMV711-N<br>LMV715-N | SOT-23 (6) | 2.92 mm × 1.50 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

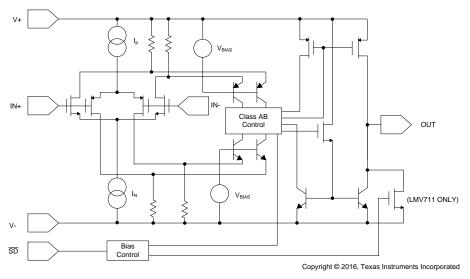

# Simplified Schematic – LMV711

2

# **Table of Contents**

| 1 | Feat | ures 1                               |

|---|------|--------------------------------------|

| 2 | Арр  | lications1                           |

| 3 |      | cription1                            |

| 4 | Rev  | ision History 2                      |

| 5 | Pin  | Configuration and Functions          |

| 6 | Spe  | cifications                          |

|   | 6.1  | Absolute Maximum Ratings 4           |

|   | 6.2  | ESD Ratings 4                        |

|   | 6.3  | Recommended Operating Conditions 4   |

|   | 6.4  | Thermal Information 4                |

|   | 6.5  | Electrical Characteristics – 2.7 V 5 |

|   | 6.6  | Electrical Characteristics - 3.2 V 6 |

|   | 6.7  | Electrical Characteristics – 5 V 6   |

|   | 6.8  | Typical Characteristics 8            |

| 7 | Deta | ailed Description 14                 |

|   | 7.1  | Overview 14                          |

|   | 7.2  | Functional Block Diagram 14          |

|   | 7.3  | Feature Description 14               |

|   |      |                                      |

|    | 7.4  | Device Functional Modes                         | 16 |

|----|------|-------------------------------------------------|----|

| 8  | App  | lication and Implementation                     | 19 |

|    | 8.1  | Application Information                         | 19 |

|    | 8.2  | Typical Applications                            | 19 |

| 9  | Pow  | er Supply Recommendations                       | 22 |

| 10 | Laye | out                                             | 22 |

|    | 10.1 | Layout Guidelines                               | 22 |

|    | 10.2 | Layout Example                                  | 22 |

| 11 | Dev  | ice and Documentation Support                   | 23 |

|    | 11.1 | Device Support                                  | 23 |

|    | 11.2 | Documentation Support                           | 23 |

|    | 11.3 | Related Links                                   | 23 |

|    | 11.4 | Receiving Notification of Documentation Updates | 23 |

|    | 11.5 | Community Resources                             | 23 |

|    | 11.6 | Trademarks                                      | 23 |

|    | 11.7 | Electrostatic Discharge Caution                 | 24 |

|    | 11.8 | Glossary                                        | 24 |

| 12 |      | hanical, Packaging, and Orderable<br>mation     | 24 |

|    |      |                                                 |    |

# **4** Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

# Changes from Revision J (March 2013) to Revision K

| Cł | nanges from Revision J (March 2013) to Revision K                                                                                                                                                                                                                                    | Page |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|    | Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section. | 1    |

www.ti.com

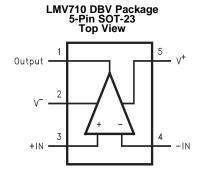

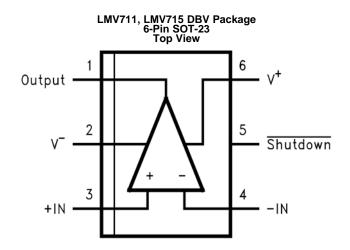

# 5 Pin Configuration and Functions

#### Pin Functions

|                | PIN     |         | TYPE <sup>(1)</sup> | DESCRIPTION             |

|----------------|---------|---------|---------------------|-------------------------|

| NAME           | DBV (5) | DBV (6) | ITPE''              | DESCRIPTION             |

| +IN            | 3       | 3       | I                   | Noninverting input      |

| –IN            | 4       | 4       | I                   | Inverting input         |

| Output         | 1       | 1       | 0                   | Output                  |

| Shutdown       | —       | 5       | I                   | Active low enable input |

| V <sup>+</sup> | 5       | 6       | Р                   | Positive supply input   |

| V <sup>-</sup> | 2       | 2       | Р                   | Supply negative input   |

(1) I = Input, O = Output, P = Power

SNOS519K-APRIL 2000-REVISED AUGUST 2016

www.ti.com

#### Specifications 6

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)(2)</sup>

|                                                          | MIN                     | MAX                     | UNIT |

|----------------------------------------------------------|-------------------------|-------------------------|------|

| Differential input voltage                               | ±Supply voltage         |                         |      |

| Voltage at input or output pin                           | (V <sup>-</sup> ) - 0.4 | (V <sup>+</sup> ) + 0.4 | V    |

| Supply voltage (V <sup>+</sup> - V <sup>-</sup> )        |                         | 5.5                     | V    |

| Output short circuit to V <sup>+</sup>                   | See <sup>(3)</sup>      |                         |      |

| Output short circuit to V <sup>−</sup>                   | See <sup>(4)</sup>      |                         |      |

| Current at input pin                                     |                         | ±10                     | mA   |

| Mounting temperature, infrared or convection (20 sec)    |                         | 235                     | °C   |

| Junction temperature, T <sub>J(MAX)</sub> <sup>(5)</sup> |                         | 150                     | °C   |

| Storage temperature, T <sub>stg</sub>                    | -65                     | 150                     | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and (2) specifications.

Shorting circuit output to V<sup>+</sup> will adversely affect reliability. Shorting circuit output to V<sup>-</sup> will adversely affect reliability. (3)

(4)

The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A) / R_{\theta JA}$ . All numbers apply for packages soldered directly into a PCB. (5)

# 6.2 ESD Ratings

|                                            |                                   |                                          | VALUE | UNIT |  |

|--------------------------------------------|-----------------------------------|------------------------------------------|-------|------|--|

| V                                          | Electrostatio discharge           | Human-body model (HBM) <sup>(1)(2)</sup> | ±2000 | V    |  |

| V <sub>(ESD)</sub> Electrostatic discharge | Machine model (MM) <sup>(3)</sup> | ±100                                     | v     |      |  |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. (1)

Human-body model, 1.5 k $\Omega$  in series with 100 pF. (2)

(3) Machine model,  $0 \Omega$  in series with 100 pF.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                | MIN | MAX | UNIT |

|----------------|-----|-----|------|

| Supply voltage | 2.7 | 5   | V    |

| Temperature    | -40 | 85  | °C   |

#### Thermal Information 6.4

|                       |                                              | LMV710-N     | LMV711-N     | LMV715-N     |      |

|-----------------------|----------------------------------------------|--------------|--------------|--------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DBV (SOT-23) | DBV (SOT-23) | DBV (SOT-23) | UNIT |

|                       |                                              | 5 PINS       | 6 PINS       | 6 PINS       |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 265          | 265          | 265          | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 131.6        | 139          | 156.6        | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 35.1         | 38.5         | 32.8         | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 22.2         | 28.6         | 34           | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 34.5         | 37.9         | 32.2         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | _            | _            |              | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application (1)report.

# 6.5 Electrical Characteristics – 2.7 V

$T_J = 25^{\circ}C$ , V<sup>+</sup> = 2.7 V, V<sup>-</sup> = 0 V, V<sub>CM</sub> = 1.35 V, and R<sub>L</sub> > 1 M $\Omega$  (unless otherwise noted)

|                     | PARAMETER                                  | TEST C                                                     | CONDITIONS                                            | MIN <sup>(1)</sup>  | TYP <sup>(2)</sup> | MAX <sup>(1)</sup> | UNIT |  |

|---------------------|--------------------------------------------|------------------------------------------------------------|-------------------------------------------------------|---------------------|--------------------|--------------------|------|--|

|                     | Input offect veltors                       | V <sub>CM</sub> = 0.85 V and                               | $T_J = 25^{\circ}C$                                   |                     | 0.4                | 3                  |      |  |

| V <sub>OS</sub>     | Input offset voltage                       | $V_{CM} = 1.85 V$                                          | $T_J = -40^{\circ}C$ to $85^{\circ}C$                 |                     |                    | 3.2                | mV   |  |

| в                   | Input bias current                         |                                                            |                                                       |                     | 4                  |                    | pА   |  |

|                     | Common-mode                                |                                                            | $T_J = 25^{\circ}C$                                   | 50                  | 75                 |                    | ٩D   |  |

| CMRR                | rejection ratio                            | $0 \text{ V} \leq \text{V}_{\text{CM}} \leq 2.7 \text{ V}$ | $T_J = -40^{\circ}C$ to $85^{\circ}C$                 | 45                  |                    |                    | dB   |  |

|                     |                                            | $2.7 \text{ V} \leq \text{V}^+ \leq 5 \text{ V},$          | $T_J = 25^{\circ}C$                                   | 70                  | 110                |                    |      |  |

| PSRR                | Power supply rejection ratio               | $V_{CM} = 0.85 V$                                          | $T_J = -40^{\circ}C$ to $85^{\circ}C$                 | 68                  |                    |                    | dB   |  |

|                     |                                            | $2.7 \text{ V} \leq \text{V}^+ \leq 5 \text{ V},$          | $T_J = 25^{\circ}C$                                   | 70                  | 95                 |                    | uВ   |  |

|                     |                                            | V <sub>CM</sub> = 1.85 V                                   | $T_J = -40^{\circ}C$ to $85^{\circ}C$                 | 68                  |                    |                    |      |  |

| Vari                | Input common-mode                          | For CMRR ≥ 50 dB                                           | V-                                                    | -0.2                | -0.3               |                    | V    |  |

| V <sub>CM</sub>     | voltage range                              |                                                            | V+                                                    |                     | 3                  | 2.9                | v    |  |

|                     |                                            | Sourcing, V <sub>O</sub> = 0 V                             | $T_J = 25^{\circ}C$                                   | 15                  | 28                 |                    |      |  |

|                     | Output abort airquit aurrant               | Sourcing, $v_0 = 0$ v                                      | $T_J = -40^{\circ}C$ to $85^{\circ}C$                 | 12                  |                    |                    | mA   |  |

| I <sub>SC</sub>     | Output short-circuit current               | Sinking $V_{-} = 2.7 V_{-}$                                | $T_J = 25^{\circ}C$                                   | 25                  | 40                 |                    | ШA   |  |

|                     |                                            | Sinking, $V_0 = 2.7 V$                                     | $T_J = -40^{\circ}C$ to $85^{\circ}C$                 | 22                  |                    |                    |      |  |

|                     |                                            | $R_{L} = 10 \text{ k}\Omega \text{ to } 1.35 \text{ V}$    | $T_J = 25^{\circ}C$                                   | 2.62                | 2.68               |                    |      |  |

| Vo                  |                                            | VID = 100 mV                                               | $T_J = -40^{\circ}C$ to $85^{\circ}C$                 | 2.6                 |                    |                    |      |  |

|                     | Output swing                               | Rı =                                                       | $R_L = 10 \text{ k}\Omega \text{ to } 1.35 \text{ V}$ | $T_J = 25^{\circ}C$ |                    | 0.01               | 0.12 |  |

|                     |                                            | VĪD = −100 mV                                              | $T_J = -40^{\circ}C$ to $85^{\circ}C$                 |                     |                    | 0.15               | V    |  |

|                     |                                            | $R_L = 600 \Omega$ to 1.35 V<br>VID = 100 mV               | $T_J = 25^{\circ}C$                                   | 2.52                | 2.55               |                    | V    |  |

|                     |                                            |                                                            | $T_J = -40^{\circ}C$ to $85^{\circ}C$                 | 2.5                 |                    |                    |      |  |

|                     |                                            | $R_{\rm L} = 600 \ \Omega$ to 1.35 V                       | $T_J = 25^{\circ}C$                                   |                     | 0.05               | 0.23               |      |  |

|                     |                                            | VĪD = −100 mV                                              | $T_J = -40^{\circ}C$ to $85^{\circ}C$                 |                     |                    | 0.3                |      |  |

| V <sub>O</sub> (SD) | Output voltage level in<br>shutdown mode   | LMV711 only                                                |                                                       |                     | 50                 | 200                | mV   |  |

| I <sub>O</sub> (SD) | Output leakage current in<br>shutdown mode | LMV715 only                                                |                                                       |                     | 1                  |                    | pА   |  |

| C <sub>O</sub> (SD) | Output capacitance in shutdown mode        | LMV715 only                                                |                                                       |                     | 32                 |                    | pF   |  |

|                     |                                            | ON mode                                                    | $T_J = 25^{\circ}C$                                   |                     | 1.22               | 1.7                | mA   |  |

| Is                  | Supply current                             | ON mode                                                    | $T_J = -40^{\circ}C$ to $85^{\circ}C$                 |                     |                    | 1.9                | ША   |  |

|                     |                                            | Shutdown mode, $V_{SD} = 0$                                | ) V                                                   |                     | 0.002              | 10                 | μA   |  |

|                     |                                            | Sourcing, $R_L = 10 k\Omega$ ,                             | $T_J = 25^{\circ}C$                                   | 80                  | 115                |                    |      |  |

|                     |                                            | $V_0 = 1.35$ V to 2.3 V                                    | $T_J = -40^{\circ}C$ to $85^{\circ}C$                 | 76                  |                    |                    |      |  |

|                     |                                            | Sinking, $R_L = 10 k\Omega$ ,                              | $T_J = 25^{\circ}C$                                   | 80                  | 113                |                    |      |  |

| ^                   |                                            | $V_0 = 0.4 \text{ V}$ to 1.35 V                            | $T_J = -40^{\circ}C$ to $85^{\circ}C$                 | 76                  |                    |                    | dB   |  |

| A <sub>V</sub>      | Large signal voltage                       | Sourcing, $R_L = 600 \Omega$ ,                             | $T_J = 25^{\circ}C$                                   | 80                  | 110                |                    |      |  |

|                     |                                            | $V_0 = 1.35$ V to 2.2 V                                    | $T_J = -40^{\circ}C$ to $85^{\circ}C$                 | 76                  |                    |                    |      |  |

|                     |                                            | Sinking, $R_{L} = 600 \Omega$ ,                            | $T_J = 25^{\circ}C$                                   | 80                  | 100                |                    |      |  |

|                     |                                            | $V_0 = 0.5 \text{ V}$ to 1.35 V                            | $T_J = -40^{\circ}C$ to $85^{\circ}C$                 | 76                  |                    |                    |      |  |

| SR                  | Slew rate <sup>(3)</sup>                   |                                                            |                                                       |                     | 5                  |                    | V/µs |  |

| GBWP                | Gain-bandwidth product                     |                                                            |                                                       |                     | 5                  |                    | MHz  |  |

| φ <sub>m</sub>      | Phase margin                               |                                                            |                                                       |                     | 60                 |                    | ٥    |  |

| T <sub>ON</sub>     | Turnon time from shutdown                  |                                                            |                                                       |                     | <10                |                    | μs   |  |

(1) All limits are specified by testing or statistical analysis.

(2) Typical values represent the most likely parametric norm.

(3) Number specified is the slower of the positive and negative slew rates.

Copyright © 2000–2016, Texas Instruments Incorporated

RUMENTS

AS

# Electrical Characteristics – 2.7 V (continued)

$T_{\rm J}$  = 25°C, V<sup>+</sup> = 2.7 V, V<sup>-</sup> = 0 V, V<sub>CM</sub> = 1.35 V, and R<sub>L</sub> > 1 M\Omega (unless otherwise noted)

|     | PARAMETER                                  | TEST CONDITIONS | MIN <sup>(1)</sup> | TYP <sup>(2)</sup> | MAX <sup>(1)</sup> | UNIT   |

|-----|--------------------------------------------|-----------------|--------------------|--------------------|--------------------|--------|

| V   | Chutdown nin voltogo rongo                 | ON mode         | 2.4                | 1.5                | 2.7                | V      |

| VSD | V <sub>SD</sub> Shutdown pin voltage range | Shutdown mode   | 0                  | 1                  | 0.8                | v      |

| en  | Input-referred voltage noise               | f = 1 kHz       |                    | 20                 |                    | nV/√Hz |

# 6.6 Electrical Characteristics – 3.2 V

$T_{\rm J}$  = 25°C, V^+ = 3.2 V, V^- = 0 V, and V\_{\rm CM} = 1.6 V (unless otherwise noted)

|    | PARAMETER    | TEST CONDITIONS         |                                                                  | MIN <sup>(1)</sup> | TYP <sup>(2)</sup> | MAX <sup>(1)</sup> | UNIT |

|----|--------------|-------------------------|------------------------------------------------------------------|--------------------|--------------------|--------------------|------|

| Vo |              | L 6.5 mA                | $T_J = 25^{\circ}C$                                              | 2.95               | 3                  |                    |      |

|    | Output Swing | I <sub>O</sub> = 6.5 mA | $T_{\rm J} = -40^{\circ} \rm C \ to \ 85^{\circ} \rm C \qquad 2$ | 2.92               |                    |                    | V    |

|    | Output Swing |                         | $T_J = 25^{\circ}C$                                              |                    | 0.01               | 0.18               | v    |

|    |              |                         | $T_J = -40^{\circ}C$ to $85^{\circ}C$                            |                    |                    | 0.25               |      |

(1) All limits are specified by testing or statistical analysis.

(2) Typical values represent the most likely parametric norm.

# 6.7 Electrical Characteristics – 5 V

| $T_{J} = 25^{\circ}C, V^{+} = 5 V, V^{-} = 0 V, V_{CM} = 2.5 V, and R_{L} > 1 M\Omega$ (unl | ess otherwise noted) |

|---------------------------------------------------------------------------------------------|----------------------|

|---------------------------------------------------------------------------------------------|----------------------|

| PARAMETER           |                                            | TEST CONDITIONS                                      |                                       | MIN <sup>(1)</sup> | TYP <sup>(2)</sup> | MAX <sup>(1)</sup> | UNIT |

|---------------------|--------------------------------------------|------------------------------------------------------|---------------------------------------|--------------------|--------------------|--------------------|------|

| Vos                 | Input offset voltage                       | V <sub>CM</sub> = 0.85 V and                         | $T_J = 25^{\circ}C$                   |                    | 0.4                | 3                  | m\/  |

| VOS                 |                                            | V <sub>CM</sub> = 1.85 V                             | $T_J = -40^{\circ}C$ to $85^{\circ}C$ |                    |                    | 3.2                |      |

| I <sub>B</sub>      | Input bias current                         |                                                      |                                       |                    | 4                  |                    | pА   |

| CMRR                | Common-mode rejection ratio                | $0 V \le V_{CM} \le 5 V$                             | $T_J = 25^{\circ}C$                   | 50                 | 70                 |                    | dB   |

| CIVIRR              |                                            |                                                      | $T_J = -40^{\circ}C$ to $85^{\circ}C$ | 48                 |                    |                    |      |

|                     |                                            | 2.7 V $\leq$ V <sup>+</sup> $\leq$ 5 V,              | $T_J = 25^{\circ}C$                   | 70                 | 110                |                    |      |

| PSRR                | Power supply rejection ratio               | $V_{CM} = 0.85 V$                                    | $T_J = -40^{\circ}C$ to $85^{\circ}C$ | 68                 |                    |                    | dB   |

| FORK                |                                            | 2.7 V $\leq$ V <sup>+</sup> $\leq$ 5 V,              | $T_J = 25^{\circ}C$                   | 70                 | 95                 |                    |      |

|                     |                                            | V <sub>CM</sub> = 1.85 V                             | $T_J = -40^{\circ}C$ to $85^{\circ}C$ | 68                 |                    |                    |      |

| V                   | Input common-mode voltage range            | For CMRR ≥ 50 dB                                     | V-                                    | -0.2               | -0.3               |                    | v    |

| V <sub>CM</sub>     |                                            |                                                      | V+                                    |                    | 5.3                | 5.2                |      |

|                     | Output short-circuit current               | Sourcing, $V_0 = 0 V$                                | $T_J = 25^{\circ}C$                   | 25                 | 35                 |                    | mA   |

|                     |                                            |                                                      | $T_J = -40^{\circ}C$ to $85^{\circ}C$ | 21                 |                    |                    |      |

| I <sub>SC</sub>     |                                            | Sinking, V <sub>O</sub> = 5 V                        | $T_J = 25^{\circ}C$                   | 25                 | 40                 |                    |      |

|                     |                                            |                                                      | $T_J = -40^{\circ}C$ to $85^{\circ}C$ | 21                 |                    |                    |      |

|                     |                                            | $R_L = 10 \text{ k}\Omega \text{ to } 2.5 \text{ V}$ | $T_J = 25^{\circ}C$                   | 4.92               | 4.98               |                    |      |

|                     |                                            | VID = 100 mV                                         | $T_J = -40^{\circ}C$ to $85^{\circ}C$ | 4.9                |                    |                    |      |

|                     |                                            | $R_L = 10 \text{ k}\Omega \text{ to } 2.5 \text{ V}$ | $T_J = 25^{\circ}C$                   |                    | 0.01 0.12          |                    |      |

| M                   |                                            | VID = -100 mV                                        | $T_J = -40^{\circ}C$ to $85^{\circ}C$ |                    |                    | 0.15               | V    |

| Vo                  | Output swing                               | $R_1 = 600 \Omega$ to 2.5 V                          | $T_J = 25^{\circ}C$                   | 4.82               | 4.85               |                    | V    |

|                     |                                            | VĪD = 100 mV                                         | $T_J = -40^{\circ}C$ to $85^{\circ}C$ | 4.8                |                    |                    |      |

|                     |                                            | $R_1 = 600 \Omega$ to 2.5 V                          | $T_J = 25^{\circ}C$                   |                    | 0.05               | 0.23               |      |

|                     |                                            | VĪD = −100 mV                                        | $T_J = -40^{\circ}C$ to $85^{\circ}C$ |                    |                    | 0.3                | l    |

| V <sub>O</sub> (SD) | Output voltage level in<br>shutdown mode   | LMV711 only                                          |                                       |                    | 50                 | 200                | mV   |

| I <sub>O</sub> (SD) | Output leakage current in<br>shutdown mode | LMV715 only                                          |                                       |                    | 1                  |                    | pА   |

(1) All limits are specified by testing or statistical analysis.

<sup>(2)</sup> Typical values represent the most likely parametric norm.

# Electrical Characteristics – 5 V (continued)

| PARAMETER           |                                     | TEST CONDITIONS                                                           |                                       | MIN <sup>(1)</sup> | TYP <sup>(2)</sup> | MAX <sup>(1)</sup> | UNIT   |

|---------------------|-------------------------------------|---------------------------------------------------------------------------|---------------------------------------|--------------------|--------------------|--------------------|--------|

| C <sub>O</sub> (SD) | Output capacitance in shutdown mode | LMV715 only                                                               |                                       |                    | 32                 |                    | pF     |

|                     | Supply current                      | ON mode                                                                   | $T_J = 25^{\circ}C$                   |                    | 1.17               | 1.7                | mA     |

| I <sub>S</sub>      |                                     |                                                                           | $T_J = -40^{\circ}C$ to $85^{\circ}C$ |                    |                    | 1.9                |        |

|                     |                                     | Shutdown mode                                                             |                                       |                    | 0.2                | 10                 | μA     |

|                     |                                     | Sourcing, $R_L = 10 k\Omega$ ,                                            | $T_J = 25^{\circ}C$                   | 80                 | 123                |                    |        |

|                     |                                     | $V_0 = 2.5 \text{ V to } 4.6 \text{ V}$                                   | $T_J = -40^{\circ}C$ to $85^{\circ}C$ | 76                 |                    |                    | dB     |

|                     |                                     | Sinking, $R_L = 10 k\Omega$ ,                                             | $T_J = 25^{\circ}C$                   | 80                 | 120                |                    |        |

| ^                   | Large signal voltage gain           | $V_0 = 0.4 \text{ V}$ to 2.5 V                                            | $T_J = -40^{\circ}C$ to $85^{\circ}C$ | 76                 |                    |                    |        |

| A <sub>V</sub>      |                                     | Sourcing, R <sub>L</sub> = 600 $\Omega$ , V <sub>O</sub> = 2.5 V to 4.5 V | $T_J = 25^{\circ}C$                   | 80                 | 110                |                    |        |

|                     |                                     |                                                                           | $T_J = -40^{\circ}C$ to $85^{\circ}C$ | 76                 |                    |                    |        |

|                     |                                     | Sinking, $R_{L} = 600 \Omega$ ,                                           | $T_J = 25^{\circ}C$                   | 76<br>80 118       |                    |                    |        |

|                     |                                     | $V_0 = 0.5 V$ to 2.5 V                                                    | $T_J = -40^{\circ}C$ to $85^{\circ}C$ | 76                 |                    |                    |        |

| SR                  | Slew rate <sup>(3)</sup>            |                                                                           |                                       |                    | 5                  |                    | V/µs   |

| GBWP                | Gain-bandwidth product              |                                                                           |                                       |                    | 5                  |                    | MHz    |

| φ <sub>m</sub>      | Phase margin                        |                                                                           |                                       |                    | 60                 |                    | 0      |

| T <sub>ON</sub>     | Turnon time from shutdown           |                                                                           |                                       |                    | <10                |                    | μs     |

| $V_{SD}$            |                                     | ON mode                                                                   |                                       | 2.4                | 2                  | 5                  | V      |

|                     | Shutdown pin voltage range          | Shutdown mode                                                             |                                       | 0                  | 1.5                | 0.8                |        |

| e <sub>n</sub>      | Input-referred voltage noise        | f = 1 kHz                                                                 |                                       |                    | 20                 |                    | nV/√Hz |

(3) Number specified is the slower of the positive and negative slew rates.

# LMV710-N, LMV711-N, LMV715-N

SNOS519K-APRIL 2000-REVISED AUGUST 2016

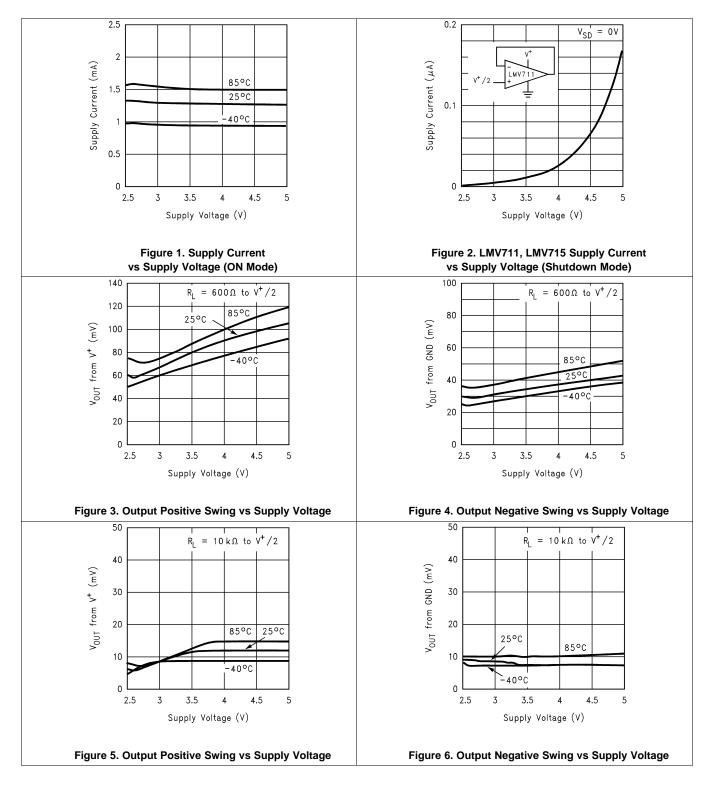

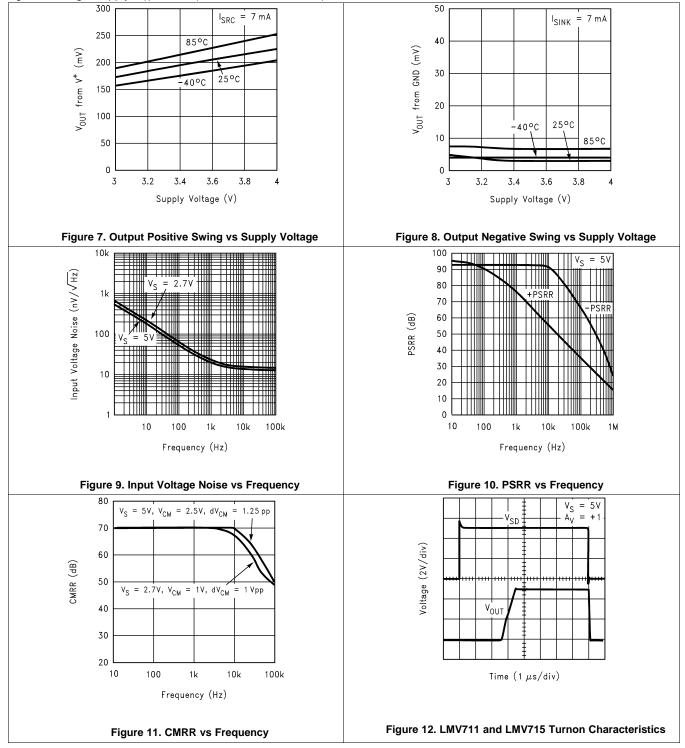

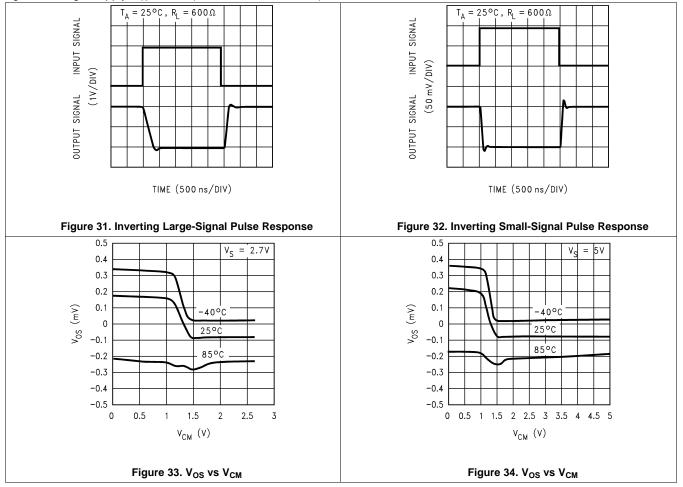

# 6.8 Typical Characteristics

$V_S = 5 V$ , single supply,  $T_A = 25^{\circ}C$  (unless otherwise noted)

8

Copyright © 2000–2016, Texas Instruments Incorporated

www.ti.com

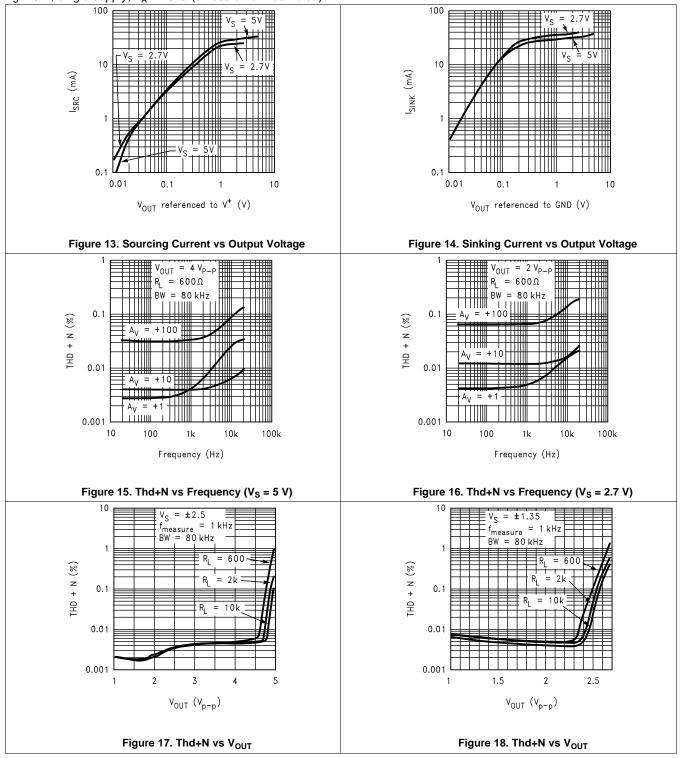

# **Typical Characteristics (continued)**

$V_S = 5 V$ , single supply,  $T_A = 25^{\circ}C$  (unless otherwise noted)

# LMV710-N, LMV711-N, LMV715-N

SNOS519K-APRIL 2000-REVISED AUGUST 2016

TEXAS INSTRUMENTS

www.ti.com

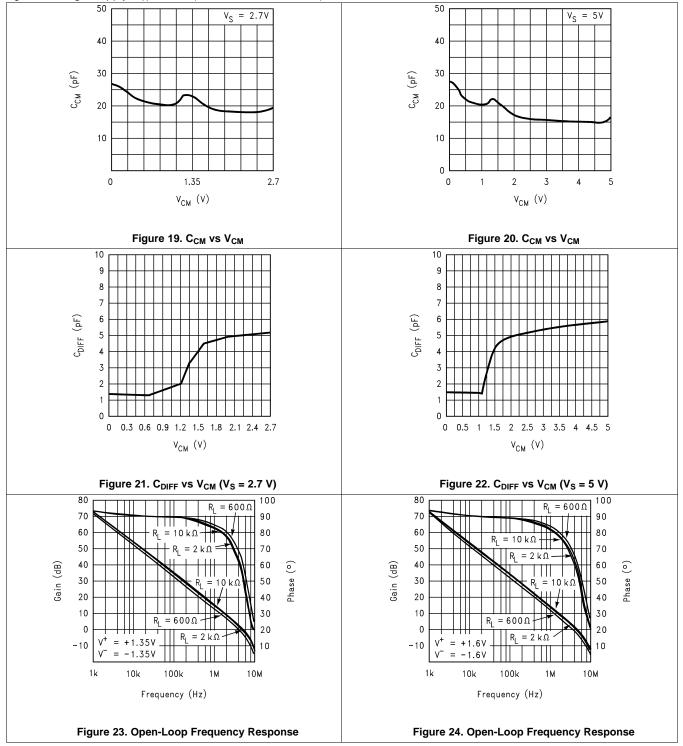

# **Typical Characteristics (continued)**

$V_S = 5 V$ , single supply,  $T_A = 25^{\circ}C$  (unless otherwise noted)

# **Typical Characteristics (continued)**

$V_{S} = 5 \text{ V}$ , single supply,  $T_{A} = 25^{\circ}\text{C}$  (unless otherwise noted)

# LMV710-N, LMV711-N, LMV715-N

SNOS519K-APRIL 2000-REVISED AUGUST 2016

www.ti.com

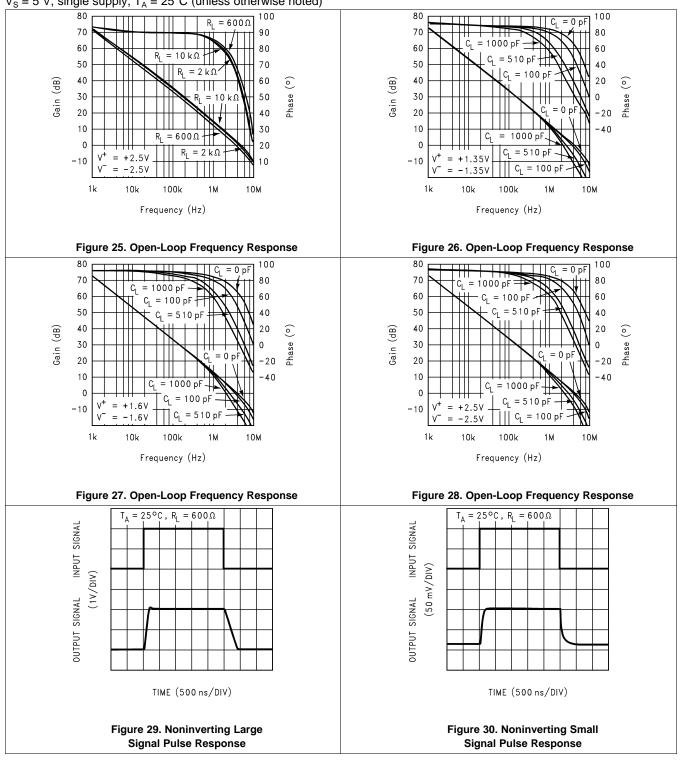

# Typical Characteristics (continued)

$V_S = 5 V$ , single supply,  $T_A = 25^{\circ}C$  (unless otherwise noted)

# **Typical Characteristics (continued)**

$V_{\rm S}$  = 5 V, single supply,  $T_{\rm A}$  = 25°C (unless otherwise noted)

# 7 Detailed Description

# 7.1 Overview

The LMV710-N, LMV711-N, and LMV715-N operational amplifiers provide a CMOS input stage, high current drive rail-to-rail output, and a greater than RR input common mode voltage range. They also provide a slew rate of 5 V/ $\mu$ s at a bandwidth of 5 MHz.

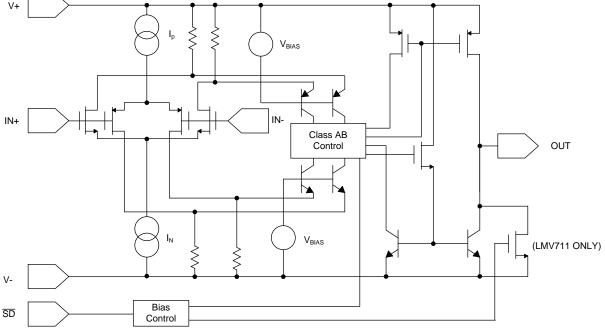

# 7.2 Functional Block Diagram

#### Copyright © 2016, Texas Instruments Incorporated

# 7.3 Feature Description

# 7.3.1 Supply Bypassing

The application circuits in this datasheet do not show the power supply connections and the associated bypass capacitors for simplification. When the circuits are built, it is always required to have bypass capacitors. Ceramic disc capacitors (0.1  $\mu$ F) or solid tantalum (1  $\mu$ F) with short leads, and located close to the IC are usually necessary to prevent interstage coupling through the power supply internal impedance. Inadequate bypassing will manifest itself by a low frequency oscillation or by high frequency instabilities. Sometimes, a 10- $\mu$ F (or larger) capacitor is used to absorb low frequency variations and a smaller 0.1- $\mu$ F disc is paralleled across it to prevent any high frequency feedback through the power supply lines.

# 7.3.2 Shutdown Mode

The LMV711 and LMV715 have a shutdown pin. To conserve battery life in portable applications, they can be disabled when the shutdown pin voltage is pulled low. For LMV711 during shutdown mode, the output stays at about 50 mV from the lower rail, and the current drawn from the power supply is 0.2  $\mu$ A (typical). This makes the LMV711 an ideal solution for power sensitive applications. For the LMV715 during shutdown mode, the output is tri-stated.

The shutdown pin must never be left unconnected. In applications where shutdown operation is not required and the LMV711 or LMV715 is used, the shutdown pin must be connected to V<sup>+</sup>. Leaving the shutdown pin floating results in an undefined operation mode and the device may oscillate between shutdown and active modes.

# Feature Description (continued)

### 7.3.3 Rail-to-Rail Input

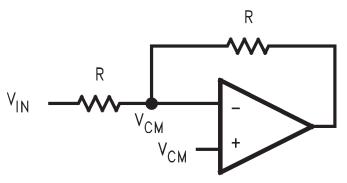

The rail-to-rail input is achieved by using paralleled PMOS and NMOS differential input stages (see *Functional Block Diagram*). When the common mode input voltage changes from ground to the positive rail, the input stage goes through three modes. First, the NMOS pair is cutoff and the PMOS pair is active. At around 1.4 V, both PMOS and NMOS pairs operate, and finally the PMOS pair is cutoff and NMOS pair is active. Because both input stages have their own offset voltage (V<sub>OS</sub>), the offset of the amplifier becomes a function of the common-mode input voltage (see Figure 33 and Figure 34 in *Typical Characteristics*).

As shown in the curve, the V<sub>OS</sub> has a crossover point at 1.4 V above V<sup>-</sup>. Proper design must be done in both DC- and AC-coupled applications to avoid problems. For large input signals that include the V<sub>OS</sub> crossover point in their dynamic range, it causes distortion in the output signal. One way to avoid such distortion is to keep the signal away from the crossover point. For example, in a unity-gain buffer configuration and with V<sub>S</sub> = 5 V, a 3-V peak-to-peak signal center at 2.5 V contains input-crossover distortion. To avoid this, the input signal must be centered at 3.5 V instead. Another way to avoid large signal distortion is to use a gain of -1 circuit which avoids any voltage excursions at the input terminals of the amplifier (see Figure 35). In this circuit, the common-mode DC voltage (V<sub>CM</sub>) can be set at a level away from the V<sub>OS</sub> crossover point.

Figure 35. Inverting Configuration

When the input is a small signal and this small signal falls inside the  $V_{OS}$  transition range, the gain, CMRR and some other parameters is degraded. To resolve this problem, the small signal must be placed such that it avoids the  $V_{OS}$  crossover point.

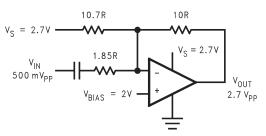

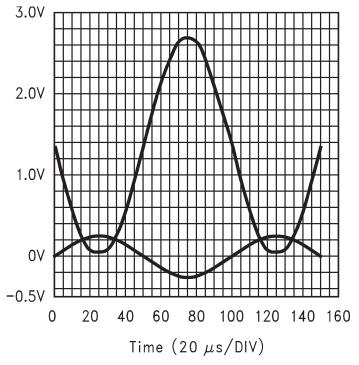

To achieve maximum output swing, the output must be biased at mid-supply. This is normally done by biasing the input at mid-supply. But with supply voltage range from 2 V to 3.4 V, the input of the op amp must not be biased at mid-supply because of the transition of the V<sub>OS</sub>. Figure 36 shows an example of how to get away from the V<sub>OS</sub> crossover point and maintain a maximum swing with a 2.7-V supply. Figure 37 shows the waveforms of V<sub>IN</sub> and V<sub>OUT</sub>.

Figure 36. Vout biasing Example

TEXAS INSTRUMENTS

www.ti.com

# Feature Description (continued)

Figure 37. Vout biasing Output Results

The inputs can be driven 300 mV beyond the supply rails without causing phase reversal at the output. However, the inputs must not be allowed to exceed the maximum ratings.

# 7.4 Device Functional Modes

# 7.4.1 Compensation of Input Capacitance

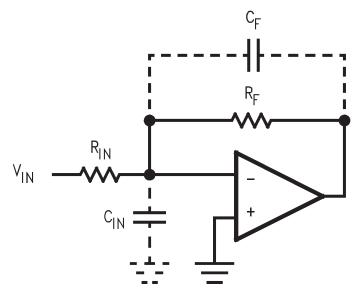

In the application (Figure 38) where a large feedback resistor is used, the feedback resistor can react with the input capacitance of the op amp and introduce an additional pole to the close loop frequency response.

### **Device Functional Modes (continued)**

This pole occurs at frequency  $f_p$  with Equation 1.

$$f_{P} = \frac{I}{2\pi(R_{IN} || R_{F})C_{IN}}$$

(1)

Any stray capacitance due to external circuit board layout, any source capacitance from transducer or photodiode connected to the summing node is added to the input capacitance. If  $f_p$  is less than or close to the unity-gain bandwidth (5 MHz) of the op amp, the phase margin of the loop is reduced and can cause the system to be unstable.

To avoid this problem, make sure that  $f_p$  occurs at least 2 octaves beyond the expected -3 dB frequency corner of the close loop frequency response. If not, a feedback capacitor  $C_F$  can be placed in parallel with  $R_F$  such that Equation 2.

$$\frac{1}{2\pi R_F C_F} = \frac{1}{2\pi (R_{IN} || R_F) (C_F + C_{IN})}$$

(2)

The paralleled  $R_F$  and  $C_F$  introduce a zero, which cancels the effect from the pole.

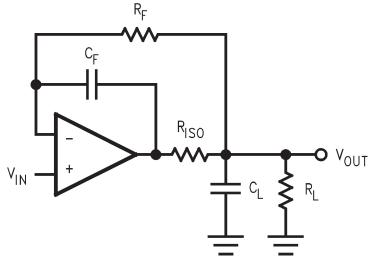

### 7.4.2 Capacitive Load Tolerance

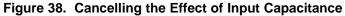

The LMV71x-N can directly drive 200 pF in unity-gain without oscillation. The unity-gain follower is the most sensitive configuration to capacitive loading. Direct capacitive loading reduces the phase margin of amplifiers. The combination of the amplifier's output impedance and the capacitive load induces phase lag. This results in either an underdamped pulse response or oscillation. To drive a heavier capacitive load, circuit in Figure 39 can be used.

Figure 39. Indirectly Driving a Capacitive Load Using Resistive Isolation

In Figure 39, the isolation resistor  $R_{ISO}$  and the load capacitor  $C_L$  form a pole to increase stability by adding more phase margin to the overall system. The desired performance depends on the value of  $R_{ISO}$ . The bigger the  $R_{ISO}$  resistor value, the more stable  $V_{OUT}$  is. But the DC accuracy is not great when the  $R_{ISO}$  gets bigger. If there were a load resistor in Figure 39, the output would be voltage divided by  $R_{ISO}$  and the load resistor.

The circuit in Figure 40 is an improvement to the one in Figure 39 because it provides DC accuracy as well as AC stability. In this circuit,  $R_F$  provides the DC accuracy by using feed-forward techniques to connect  $V_{IN}$  to  $R_L$ .  $C_F$  and  $R_{ISO}$  serve to counteract the loss of phase margin by feeding the high-frequency component of the output signal back to the inverting input of the amplifier, thereby preserving phase margin in the overall feedback loop. Increased capacitive drive is possible by increasing the value of  $C_F$ . This in turn slows down the pulse response.

# **Device Functional Modes (continued)**

Figure 40. Indirectly Driving a Capacitive a Load With DC Accuracy

# 8 Application and Implementation

### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 8.1 Application Information

The LMV71x family of amplifiers features low voltage, low power, and rail-to-rail output operational amplifiers designed for low-voltage portable applications.

# 8.2 Typical Applications

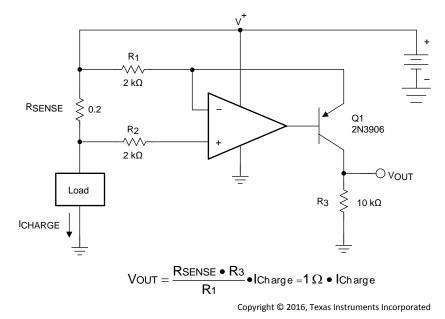

### 8.2.1 High-Side Current-Sensing

Figure 41. High-Side, Current-Sensing Schematic

### 8.2.1.1 Design Requirements

The high-side, current-sensing circuit (Figure 41) is commonly used in a battery charger to monitor charging current to prevent over charging. A sense resistor  $R_{SENSE}$  is connected to the battery directly. This system requires an op amp with rail-to-rail input. The LMV71x are ideal for this application because its common-mode input range goes up to the rail.

### 8.2.1.2 Detailed Design Procedure

As seen in (Figure 41), the  $I_{CHARGE}$  current flowing through sense resistor  $R_{SENSE}$  develops a voltage drop equal to  $V_{SENSE}$ . The voltage at the negative sense point is now less than the positive sense point by an amount proportional to the  $V_{SENSE}$  voltage.

The low-bias currents of the LMV71x cause little voltage drop through  $R_2$ , so the negative input of the LMV71x amplifier is at essentially the same potential as the negative sense input.

The LMV71x detects this voltage error between its inputs and servo the transistor base to conduct more current through Q1, increasing the voltage drop across  $R_1$  until the LMV71x inverting input matches the noninverting input. At this point, the voltage drop across  $R_1$  now matches  $V_{\text{SENSE}}$ .

$I_{G}$ , a current proportional to  $I_{CHARGE}$ , flows according to Equation 3.

SNOS519K-APRIL 2000-REVISED AUGUST 2016

NSTRUMENTS

ÈXAS

# **Typical Applications (continued)**

| $I_G = V_{RSENSE} / R_1 = (R_{SENSE} \times I_{CHARGE}) / R_1$                                            | (3) |

|-----------------------------------------------------------------------------------------------------------|-----|

| $I_{G}$ also flows through the gain resistor $R_{3}$ developing a voltage drop equal to Equation 4.       |     |

| $V_3 = I_G \times R_3 = (V_{RSENSE} / R_1) \times R_3 = ((R_{SENSE} \times I_{CHARGE}) / R_2) \times R_3$ | (4) |

|                                                                                                           |     |

$V_{OUT} = (R_{SENSE} \times I_{CHARGE}) \times G$

where

•

$$G = R_3 / R_1$$

(5)

The other channel of the LMV71x may be used to buffer the voltage across R3 to drive the following stages.

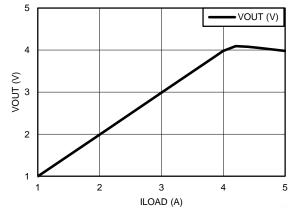

# 8.2.1.3 Application Curve

Figure 42. High-Side Current-Sensing Results

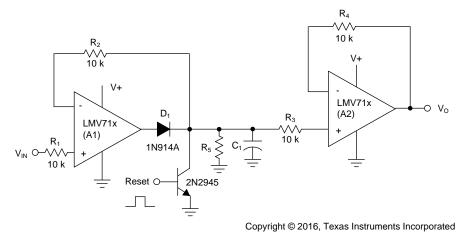

# 8.2.2 Peak Detector

Figure 43. Peak Detector

# 8.2.2.1 Design Requirements

A peak detector outputs a DC voltage equal to the peak value of the applied AC signal. Peak detectors are used in many applications, such as test equipment, measurement instrumentation, ultrasonic alarm systems, and so forth. Figure 43 shows the schematic diagram of a peak detector using LMV71x-N. This peak detector basically consists of a clipper, a parallel RC network, and a voltage follower.

## **Typical Applications (continued)**

### 8.2.2.2 Detailed Design Procedure

An AC voltage source applied to  $V_{IN}$  charges capacitor C1 to the peak of the input. Diode D1 conducts positive *half cycles*, charging C1 to the waveform peak. Including D1 inside the feedback loop of the amplifier removes the voltage drop of D1 and allows an accurate peak detection of  $V_{IN}$  on C1. When the input waveform falls below the DC *peak* stored on C1, D1 is reverse biased. The low input bias current of A1 and the reverse biasing of D1 limits current leakage from C1. As a result, C1 retains the peak value even as the waveform drops to zero. A2 further isolates the peak value on C1 while completing the peak detector circuit by operating as a voltage follower and reporting the peak voltage of C1 at its output.

R5 and C1 are properly selected so that the capacitor is charged rapidly to  $V_{IN}$ . During the holding period, the capacitor slowly discharge through C1, through leakage of the capacitor and the reverse-biased diode, or op amp bias currents. In any cases the discharging time constant is much larger than the charge time constant. And the capacitor can hold its voltage long enough to minimize the output ripple.

Resistors R2 and R3 limit the current into the inverting input of A1 and the noninverting input of A2 when power is disconnected from the circuit. The discharging current from C1 during power off may damage the input circuitry of the op amps.

The peak detector is reset by applying a positive pulse to the reset transistor. The charge on the capacitor is dumped into ground, and the detector is ready for another cycle.

The maximum input voltage to this detector must be less than  $(V^+ - V_D)$ , where  $V_D$  is the forward voltage drop of the diode. Otherwise, the input voltage must be scaled down before applying to the circuit.

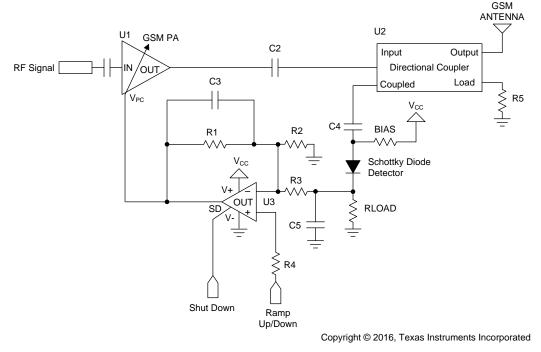

# 8.2.3 GSM Power Amplifier Control Loop

Figure 44. GSM P.A. Control Loop

### 8.2.3.1 Design Requirements

The control loop in Figure 44 controls the output power level of a GSM mobile phones. The control loop is used to avoid intermodulation of Base Station receivers, to prevent intermodulation with other mobile phones, and to minimize power consumption depending on the distance between mobile and base station

Copyright © 2000–2016, Texas Instruments Incorporated

# **Typical Applications (continued)**

### 8.2.3.2 Detailed Design Procedure

There are four critical sections in the GSM Power Amplifier Control Loop. The class-C  $R_F$  power amplifier provides amplification of the  $R_F$  signal. A directional coupler couples small amount of  $R_F$  energy from the output of the  $R_F$  P. A. to an envelope detector diode. The detector diode senses the signal level and rectifies it to a DC level to indicate the signal strength at the antenna. An op amp is used as an error amplifier to process the diode voltage and ramping voltage. This loop control the power amplifier gain through the op amp and forces the detector diode voltage and ramping voltage to be equal. Power control is accomplished by changing the ramping voltage.

The LMV71x-N are well suited as an error amplifier in this application. The LMV711 or LMV715 have an extra shutdown pin to switch the op amp to shutdown mode. In shutdown mode, the LMV711 or LMV715 consume very low current. The LMV711 provides a ground voltage to the power amplifier control pin  $V_{PC}$ . Therefore, the power amplifier can be turned off to save battery life. The LMV715 output is tri-stated when in shutdown.

# 9 Power Supply Recommendations

For proper operation, the power supplies must be properly decoupled. For decoupling the supply lines, TI recommends that 10-nF capacitors be placed as close as possible to the power supply pins of the operational amplifier. For single supply, place a capacitor between V<sup>+</sup> and V<sup>-</sup> supply leads. For dual supplies, place one capacitor between V<sup>+</sup> and ground, and one capacitor between V<sup>-</sup> and ground.

# 10 Layout

# 10.1 Layout Guidelines

To properly bypass the power supply, several locations on a printed-circuit board must be considered. A 6.8-µF or greater tantalum capacitor must be placed at the point where the power supply for the amplifier is introduced onto the board. Another 0.1-µF ceramic capacitor must be placed as close as possible to the power supply pin of the amplifier. If the amplifier is operated in a single power supply, only the V<sup>+</sup> pin requires a bypass with a 0.1-µF capacitor. If the amplifier is operated in a dual power supply, both V<sup>+</sup> and V<sup>-</sup> pins must be bypassed. It is good practice to use a ground plane on a printed-circuit board to provide all components with a low inductive ground connection.

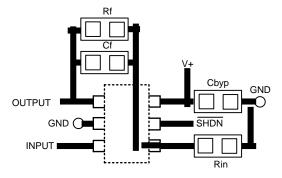

# 10.2 Layout Example

Figure 45. LMV711 Layout Example

# **11** Device and Documentation Support

# 11.1 Device Support

# 11.1.1 Development Support

For development support see the following:

- LMV710 PSPICE Model (applicable for LMV711 and LMV715)

- SPICE-based analog simulation program, TINA-TI

- DIP adapter evaluation module, DIP Adapter EVM

- TI universal operational amplifier evaluation module, Op Amp EVM

- TI software, FilterPro

# **11.2 Documentation Support**

# 11.2.1 Related Documentation

For related documentation see the following:

- Absolute Maximum Ratings for Soldering (SNOA549)

- AN-29 IC Op Amp Beats FETs on Input Current (SNOA624)

- AN-31 Op Amp Circuit Collection (SNLA140)

- AN-71 Micropower Circuits Using the LM4250 Programmable Op Amp (SNOA652)

- AN-127 LM143 Monolithic High Voltage Operational Amplifier Applications (SNVA516)

# 11.3 Related Links

The table below lists quick access links. Categories include technical documents, support and community resources, tools and software, and quick access to sample or buy.

| PARTS    | PRODUCT FOLDER | SAMPLE & BUY | TECHNICAL<br>DOCUMENTS | TOOLS &<br>SOFTWARE | SUPPORT &<br>COMMUNITY |

|----------|----------------|--------------|------------------------|---------------------|------------------------|

| LMV710-N | Click here     | Click here   | Click here             | Click here          | Click here             |

| LMV711-N | Click here     | Click here   | Click here             | Click here          | Click here             |

| LMV715-N | Click here     | Click here   | Click here             | Click here          | Click here             |

### Table 1. Related Links

# 11.4 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

# 11.5 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E<sup>™</sup> Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support TI's Design Support** Quickly find helpful E2E forums along with design support tools and contact information for technical support.

# 11.6 Trademarks

E2E is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

Copyright © 2000–2016, Texas Instruments Incorporated

SNOS519K-APRIL 2000-REVISED AUGUST 2016

```

www.ti.com

```

STRUMENTS

EXAS

# 11.7 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# 11.8 Glossary

# SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

# 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ctivity                       |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2016, Texas Instruments Incorporated