## **Brief Description**

The ZSLS7025, one of our ZSLS Family of LED control ICs, is a constant current boost converter designed for driving high-brightness LEDs. It is optimal for driving multiple white LEDs connected in series so that the LED current is uniform for better brightness and color control. The wide input range and high output current enables diverse industrial, after-market automotive, and consumer lighting applications.

The ZSLS7025 output current is adjustable via an external current sense resistor and can deliver stable constant output current from a few milliamps up to 2A or higher.

The ZSLS7025 drives a constant current into the load. The control loop features a pulse frequency modulated (PFM) architecture that is inherently stable and does not need loop compensation.

The ZSLS7025 supports pulse-width modulation (PWM) or linear voltage dimming, which allows flexible control of the LED luminance.

The ZSLS7025 can operate in applications with a wide input voltage range from 5V to 100V. An integrated over-voltage protection (OVP) circuit protects the system, even under no-load conditions. The over-voltage protection is adjustable via external resistors  $R_1$  and  $R_2$ .

### Features

- Wide application input voltage range: 5V to 100V (Higher voltage supported. See section 2.1 in the data sheet.)

- Constant current output limited only by external component selection

- No loop compensation required

- Internal over-voltage protection

- Internal over-temperature protection

- Brightness control via PWM or DC voltage control signal input

- SOP-8 package

#### Benefits

- High efficiency: up to 95%

- Minimum bill of materials

- Small form-factor package

### **Available Support**

Demonstration Kit

#### **Physical Characteristics**

- Junction temperature: -40°C to 125°C

- RoHS compliant

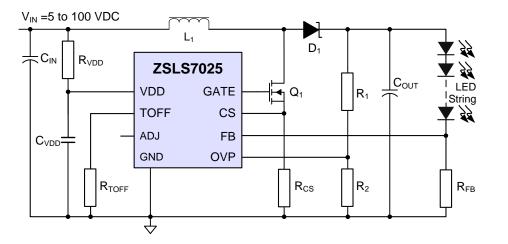

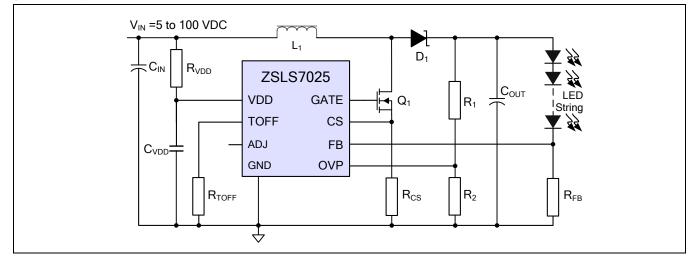

### **ZSLS7025** Typical Application Circuit

© 2016 Integrated Device Technology, Inc.

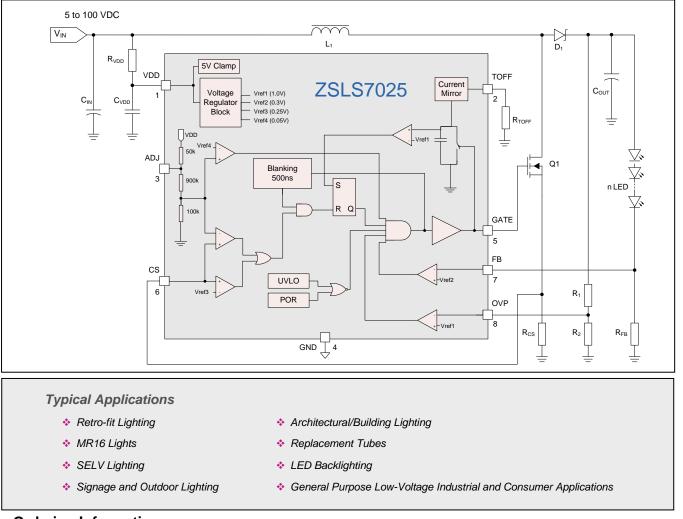

### ZSLS7025 Block Diagram

| Ordering Informat | Package                                                     |                     |

|-------------------|-------------------------------------------------------------|---------------------|

| ZSLS7025ZI1R      | ZSLS7025 – Boost LED Driver                                 | SOP-8 (Tape & Reel) |

| ZSLS7025KIT-D1    | ZSLS7025PCB-D1 Demo Board, 1 ZLED-PCB10, and 5 ZSLS7025 ICs | Kit                 |

Corporate Headquarters 6024 Silver Creek Valley Road San Jose, CA 95138 www.IDT.com Sales 1-800-345-7015 or 408-284-8200 Fax: 408-284-2775 www.IDT.com/go/sales

# Tech Support

www.IDT.com/go/support

DISCLAIMER Integrated Device Technology, Inc. (IDT) reserves the right to modify the products and/or specifications described herein at any time, without notice, at IDT's sole discretion. Performance specifications and operating parameters of the described products are determined in an independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of to the others.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are trademarks or registered trademarks of IDT and its subsidiaries in the United States and other countries. Other trademarks used herein are the property of IDT or their respective third party owners. For datasheet type definitions and a glossary of common terms, visit <a href="http://www.idt.com/go/glossary">www.idt.com/go/glossary</a>. All contents of this document are copyright of Integrated Device Technology, Inc. All rights reserved.

# Contents

| 1 | IC C  | IC Characteristics                                                           |     |  |  |  |  |  |

|---|-------|------------------------------------------------------------------------------|-----|--|--|--|--|--|

|   | 1.1   | Absolute Maximum/Minimum Ratings                                             | . 5 |  |  |  |  |  |

|   | 1.2   | Operating Conditions                                                         | . 5 |  |  |  |  |  |

|   | 1.3   | Electrical Parameters                                                        | . 6 |  |  |  |  |  |

|   | 1.4   | Typical Performance Characteristics Graphs                                   | 7   |  |  |  |  |  |

| 2 | Circ  | cuit Description                                                             | . 9 |  |  |  |  |  |

|   | 2.1   | ZSLS7025 Overview                                                            | . 9 |  |  |  |  |  |

|   | 2.2   | Boost Converter                                                              | . 9 |  |  |  |  |  |

|   | 2.3   | Internal 5V Regulator                                                        | 10  |  |  |  |  |  |

|   | 2.4   | Input Current                                                                | 10  |  |  |  |  |  |

|   | 2.5   | LED Current Control                                                          | 10  |  |  |  |  |  |

|   | 2.6   | Dimming Control                                                              | 10  |  |  |  |  |  |

|   | 2.6.  | 1 Dimming Control Using an External DC Control Signal                        | 11  |  |  |  |  |  |

|   | 2.6.  | 2 Dimming Control Using an RC Filter to Convert a PWM Signal to a DC Voltage | 12  |  |  |  |  |  |

|   | 2.6.  | 3 PWM Dimming with a Dimming Control MOSFET (Q <sub>2</sub> )                | 13  |  |  |  |  |  |

|   | 2.7   | Peak Input Current Control                                                   | 13  |  |  |  |  |  |

|   | 2.8   | Setting the Minimum Off-Time toFF_MIN                                        | 14  |  |  |  |  |  |

|   | 2.9   | Switching Frequency and Inductor Value                                       | 14  |  |  |  |  |  |

|   | 2.10  | DC Power Loss                                                                | 15  |  |  |  |  |  |

| 3 | Оре   | erating Conditions                                                           | 16  |  |  |  |  |  |

|   | 3.1   | Under-Voltage Lockout                                                        | 16  |  |  |  |  |  |

|   | 3.2   | Over-Voltage Protection                                                      | 16  |  |  |  |  |  |

| 4 | Арр   | plication Circuit Design                                                     | 17  |  |  |  |  |  |

|   | 4.1   | Applications                                                                 | 17  |  |  |  |  |  |

|   | 4.2   | External Component Selection                                                 | 17  |  |  |  |  |  |

|   | 4.2.  | 1 Series Resistor R <sub>VDD</sub>                                           | 17  |  |  |  |  |  |

|   | 4.2.2 | 2 Inductor L <sub>1</sub>                                                    | 17  |  |  |  |  |  |

|   | 4.2.3 | 3 High Frequency Noise Filter Capacitor C <sub>VDD</sub>                     | 18  |  |  |  |  |  |

|   | 4.2.4 | 4 Input Capacitor C <sub>IN</sub>                                            | 18  |  |  |  |  |  |

|   | 4.2.  | 5 Output Capacitor C <sub>OUT</sub> for Reducing Output Ripple               | 18  |  |  |  |  |  |

|   | 4.2.  | 6 Schottky Rectifier Diode D <sub>1</sub>                                    | 18  |  |  |  |  |  |

|   | 4.2.  |                                                                              |     |  |  |  |  |  |

|   | 4.3   | Application Circuit Layout Requirements                                      | 19  |  |  |  |  |  |

|   | 4.4   | Application Example                                                          |     |  |  |  |  |  |

|   | 4.4.  | 1 Selecting $R_{VDD}$ , $C_{IN}$ , and $C_{VDD}$                             | 20  |  |  |  |  |  |

|   | 4.4.  | 2 Selecting R <sub>TOFF</sub> to Set Minimum t <sub>OFF</sub>                | 20  |  |  |  |  |  |

|   | 4.4.3 | 3 Selecting R <sub>FB</sub> to Set Output Current and C3                     | 20  |  |  |  |  |  |

|   | 4.4.  | 4 Selecting $R_3$ , $R_4$ , $R_5$ and $C_1$                                  | 21  |  |  |  |  |  |

|   | 4.4.  | 5 R <sub>cs</sub> for Setting Input Peak Current                             | 22  |  |  |  |  |  |

|   | 4.4.  |                                                                              |     |  |  |  |  |  |

|   | 4.4.  |                                                                              |     |  |  |  |  |  |

|   | 4.4.  |                                                                              |     |  |  |  |  |  |

| 5 | ESD   | D Protection                                                                 | 24  |  |  |  |  |  |

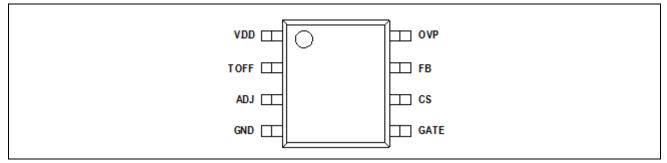

| 6 | Pin Configuration and Package | . 24 |

|---|-------------------------------|------|

|   | Glossary                      |      |

|   | Ordering Information          |      |

| 9 | Document Revision History     | . 26 |

# List of Figures

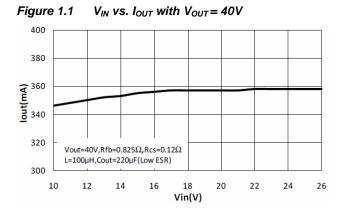

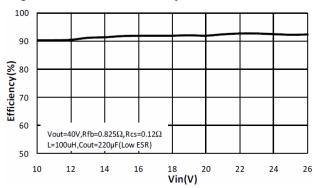

| Figure 1.1 | $V_{IN}$ vs. $I_{OUT}$ with $V_{OUT} = 40V$                                       | . 7 |

|------------|-----------------------------------------------------------------------------------|-----|

| Figure 1.2 | $V_{IN}$ vs. Efficiency with $V_{OUT} = 40V$                                      | . 7 |

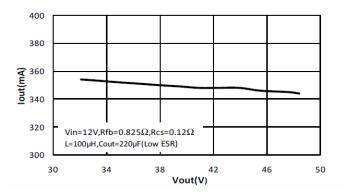

| Figure 1.3 | $V_{OUT}$ vs. $I_{OUT}$ with $V_{IN}$ = 12V                                       |     |

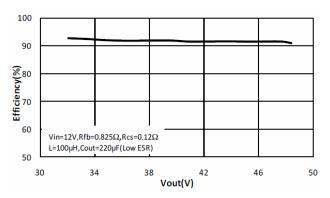

| Figure 1.4 | $V_{OUT}$ vs. Efficiency with $V_{IN} = 12V$                                      | . 7 |

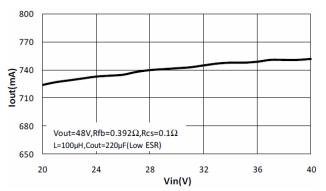

| Figure 1.5 | $V_{IN}$ vs. $I_{OUT}$ with $V_{OUT} = 48V$                                       | . 7 |

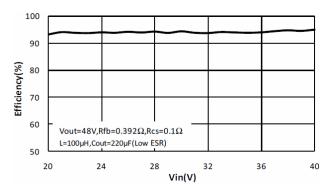

| Figure 1.6 | $V_{IN}$ vs. Efficiency with $V_{OUT} = 48V$                                      | . 7 |

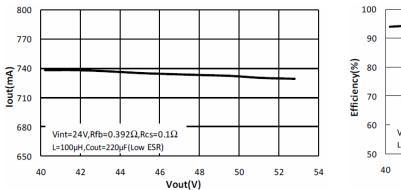

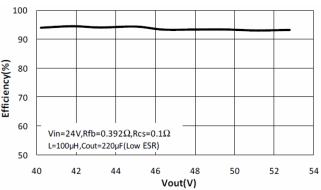

| Figure 1.7 | $V_{OUT}$ vs. $I_{OUT}$ with $V_{IN}$ = 24V                                       |     |

| Figure 1.8 | $V_{OUT}$ vs. Efficiency with $V_{IN} = 24V$                                      |     |

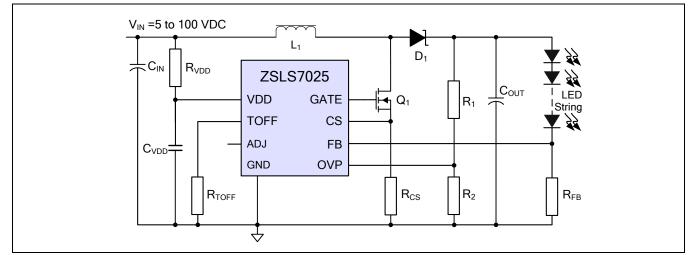

| Figure 2.1 | Typical ZSLS7025 Circuit Diagram                                                  | . 9 |

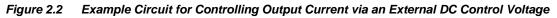

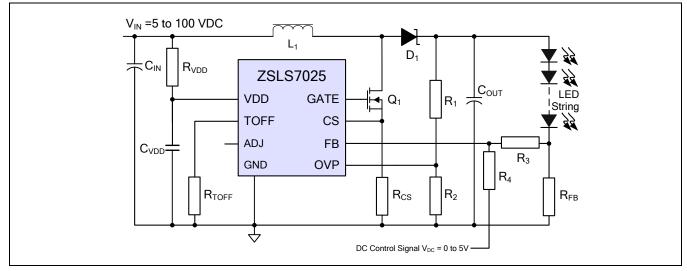

| Figure 2.2 | Example Circuit for Controlling Output Current via an External DC Control Voltage | 11  |

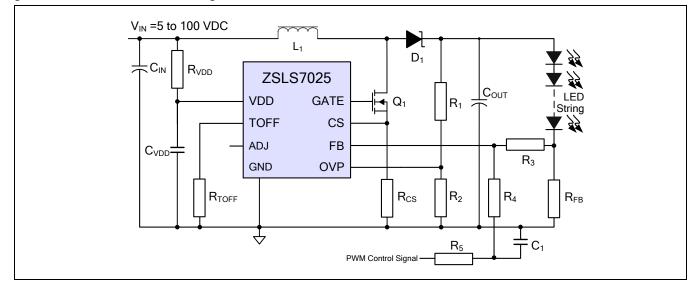

| Figure 2.3 | RC Filter PWM Dimming Circuit                                                     | 12  |

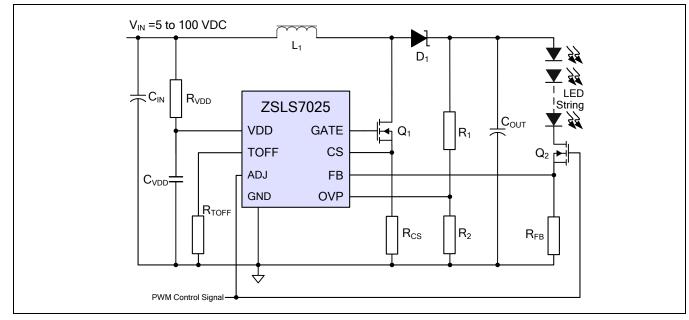

| Figure 2.4 | PWM Dimming Circuit Using a Dimming Control MOSFET (Q2)                           |     |

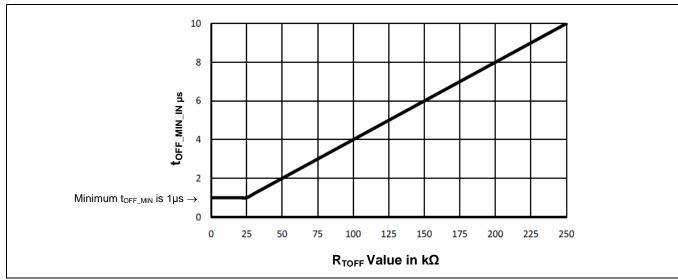

| Figure 2.5 | Minimum Off-Time toFF_MIN vs. RTOFF                                               | 14  |

| Figure 4.1 | Typical ZSLS7025 Application Circuit                                              | 17  |

| Figure 4.2 | Application Design Example – RC Filter PWM Dimming Circuit                        | 20  |

| Figure 6.1 | ZSLS7025 Pin Assignments                                                          | 24  |

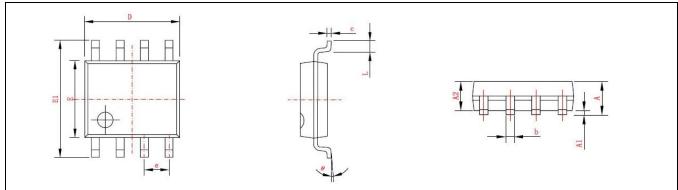

| Figure 6.2 | SOP-8 Package Dimensions and Pin Assignments                                      | 25  |

# List of Tables

| Table 1.1 | Absolute Maximum Ratings | 5 |

|-----------|--------------------------|---|

|           | Operating Conditions     |   |

|           | Electrical Parameters    |   |

| Table 6.1 | Pin Description SOP-8    | 4 |

|           |                          |   |

# **1** IC Characteristics

Stresses beyond those listed under "Absolute Maximum/Minimum Ratings" (section 1.1) may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those recommended under "Recommended Operating Conditions" (section 1.2) is not implied. Exposure to absolute–maximum conditions for extended periods may affect device reliability.

# 1.1 Absolute Maximum/Minimum Ratings

| Table 1.1 | Absolute Maximum Ratings |

|-----------|--------------------------|

|-----------|--------------------------|

| No.   | PARAMETER                                                         | SYMBOL            | CONDITIONS       | MIN  | ТҮР | MAX  | UNIT |  |

|-------|-------------------------------------------------------------------|-------------------|------------------|------|-----|------|------|--|

| 1.1.1 | Voltage on VDD pin (also<br>see specification 1.2.2 and<br>1.2.3) | V <sub>DD</sub>   |                  | -0.3 |     | 6    | V    |  |

| 1.1.2 | All other pins to GND                                             |                   |                  | -0.3 |     | 6    | V    |  |

| 1.1.3 | Maximum input current on VDD pin <sup>1)</sup>                    | I <sub>DD</sub>   |                  |      |     | 10   | mA   |  |

| 1.1.4 | ESD performance                                                   |                   | Human Body Model |      |     | ±3.5 | kV   |  |

| 1.1.5 | Junction temperature                                              | T <sub>jMAX</sub> |                  | -40  |     | 150  | °C   |  |

| 1.1.6 | Storage temperature                                               | T <sub>ST</sub>   |                  | -65  |     | 150  | °C   |  |

| 1) E  | xceeding VDD maximum input cu                                     |                   |                  |      |     |      |      |  |

# **1.2 Operating Conditions**

### Table 1.2Operating Conditions

| No.   | PARAMETER                                                   | SYMBOL          | CONDITIONS                                                                            | MIN | TYP | MAX | UNIT |  |

|-------|-------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------|-----|-----|-----|------|--|

| 1.2.1 | Junction temperature                                        | T <sub>OP</sub> |                                                                                       | -40 |     | 125 | °C   |  |

| 1.2.2 | Supply voltage <sup>1)</sup> (also see specification 1.1.1) | V <sub>IN</sub> | Supply voltage connected to VDD pin via series resistor $R_{VDD}$ (see section 4.2.1) | 5   |     | 100 | V    |  |

| 1.2.3 | VDD pin <sup>1) 2)</sup> (also see specification 1.1.1)     | V <sub>DD</sub> | Supply voltage connected to VDD pin via series resistor $R_{VDD}$ (see section 4.2.1) | 4.3 |     | 5.6 | V    |  |

| ,     | ,                                                           |                 |                                                                                       |     |     |     |      |  |

# **1.3 Electrical Parameters**

Except as noted, test conditions for the following specifications are  $V_{IN} = 10V$ ,  $R_{VDD} = 10K\Omega$ , ADJ floating, and  $T_{OP} = 25^{\circ}C$  (typical).

Production testing of the chip is performed at 25°C unless otherwise stated. Functional operation of the chip and specified parameters at other temperatures are guaranteed by design, characterization, and process control.

| No.    | PARAMETER                                      | SYMBOL                         | CONDITIONS                                 | MIN  | ТҮР | MAX  | UNIT |  |

|--------|------------------------------------------------|--------------------------------|--------------------------------------------|------|-----|------|------|--|

| 1.3.1  | VDD pin clamp voltage                          | V <sub>DD</sub>                | R <sub>VDD</sub> = 10KΩ                    | 4.3  | 5   | 5.6  | V    |  |

| 1.3.2  | Under-voltage threshold                        | Vuvlo_th                       | V <sub>DD</sub> rising                     | 2.0  | 2.7 | 3.0  | V    |  |

| 1.3.3  | Under-voltage threshold hysteresis             | $V_{\text{UVLO}_{\text{HYS}}}$ |                                            |      | 300 |      | mV   |  |

| 1.3.4  | Quiescent supply current                       | I <sub>SS</sub>                | $V_{DD} = 5V$                              |      | 250 | 400  | μA   |  |

|        |                                                |                                | V <sub>DD</sub> = 2.5V (under-voltage)     |      | 50  | 75   | μA   |  |

| 1.3.5  | Peak-current sense threshold voltage           | V <sub>CS_TH</sub>             | ADJ pin = 5V                               | 215  | 240 | 265  | mV   |  |

| 1.3.6  | Peak current sense blanking interval           | t <sub>BLANK</sub>             | V <sub>CS</sub> =V <sub>CS_TH</sub> + 50mV |      | 500 |      | ns   |  |

| 1.3.7  | Fixed turn-off interval                        | toff                           | R <sub>TOFF</sub> = 250KΩ                  |      | 10  |      | μs   |  |

| 100    | Peak-current control low threshold voltage     | N                              |                                            |      | 0.5 |      | V    |  |

| 1.3.8  | Peak-current control high threshold voltage    | V <sub>ADJ</sub>               |                                            |      | 2.4 |      | V    |  |

| 1.3.9  | Over-temperature protection<br>(OTP) threshold | T <sub>OTP</sub>               |                                            |      | 125 |      | °C   |  |

| 1.3.10 | OTP threshold hysteresis                       | T <sub>OTP_HYS</sub>           |                                            |      | 20  |      | °C   |  |

| 1.3.11 | Internal feedback reference voltage            | V <sub>FB</sub>                |                                            | 0.29 | 0.3 | 0.31 | V    |  |

| 1.3.12 | Over-voltage input threshold                   | $V_{OVP\_TH}$                  |                                            | 0.9  | 1.0 | 1.1  | V    |  |

Table 1.3Electrical Parameters

# 1.4 Typical Performance Characteristics Graphs

Figure 1.2  $V_{IN}$  vs. Efficiency with  $V_{OUT} = 40V$

Figure 1.3  $V_{OUT}$  vs.  $I_{OUT}$  with  $V_{IN} = 12V$

Figure 1.5  $V_{IN}$  vs.  $I_{OUT}$  with  $V_{OUT} = 48V$

Figure 1.4  $V_{OUT}$  vs. Efficiency with  $V_{IN} = 12V$

Figure 1.6  $V_{IN}$  vs. Efficiency with  $V_{OUT} = 48V$

# () IDT.

Figure 1.7  $V_{OUT}$  vs.  $I_{OUT}$  with  $V_{IN} = 24V$

Figure 1.8  $V_{OUT}$  vs. Efficiency with  $V_{IN} = 24V$

# 2 Circuit Description

## 2.1 ZSLS7025 Overview

The ZSLS7025 is a constant current boost converter. Its output current is adjustable via an external current sense resistor, and it can deliver stable constant output current from a few milliamps up to 2A or higher.

The ZSLS7025 drives a constant current into the load, automatically adjusting the output voltage according to the load. The control loop features a pulse frequency modulated (PFM) architecture that is inherently stable and does not need loop compensation.

The ZSLS7025 can operate in applications with a wide input voltage range from 5V to 100V.  $V_{IN}$  voltages above 100V can be supported if logic level MOSFETs for the higher voltage rating are available. An integrated over-voltage protection (OVP) circuit protects the system, even under no-load conditions. The over-voltage protection is adjustable via external resistors  $R_1$  and  $R_2$ . The minimum load voltage must always be higher than the maximum  $V_{IN}$ , and the drain voltage rating of the switching transistor ( $Q_1$ ) must be higher than the over-voltage shut-off limit.

Note: The ZSLS7025 has an internal 5V shunt regulator connected to the VDD pin. The  $R_{VDD}$  series resistor must be connected between the VDD pin and  $V_{IN}$  to limit current flow.

See section 4.2 for requirements for selecting the external components referred to in the following sections.

#### Figure 2.1 Typical ZSLS7025 Circuit Diagram

# 2.2 Boost Converter

The ZSLS7025's boost converter uses a peak-current mode topology. The CS pin voltage in conjunction with the current-sense resistor  $R_{CS}$  determines the peak current in the inductor (L<sub>1</sub>). Q<sub>1</sub> is turned on and off by the output of an RS flip-flop that is set when the voltage on the FB pin drops below the internal threshold of 300 mV. After Q<sub>1</sub> has been switched on, a blanking timer disables the current sense input CS to avoid immediate spurious shut-off as a result of the switching transient when Q<sub>1</sub> discharges the parasitic capacitances on its drain node to ground. After the blanking time t<sub>BLANK</sub> (see parameter 1.3.6 in section 1.3) has elapsed, the current through the inductor is sensed as a voltage drop across  $R_{CS}$ , and when the voltage reaches the peak-current sense threshold voltage  $V_{CS_TH}$  (see parameter 1.3.5 in section 1.3), the flip-flop is reset and Q<sub>1</sub> is turned off. Once Q<sub>1</sub> is turned off, the inductor reverses polarity, providing the voltage boost, and the inductor current will decrease until the input voltage on the FB pin drops below the internal feedback reference voltage  $V_{FB}$ , (see parameter 1.3.11 in section 1.3). Q<sub>1</sub> is then turned on again, and this operation repeats in each cycle.

9

<sup>© 2016</sup> Integrated Device Technology, Inc.

When the input voltage on the FB pin does not exceed the internal feedback reference voltage  $V_{FB}$ , such as during start-up,  $Q_1$  will remain off for the configured minimum  $t_{OFF}$  time (see sections 2.8 and 2.9), and then it is switched on again.

### 2.3 Internal 5V Regulator

The ZSLS7025 includes an internal 5V (typical) shunt regulator connected to the VDD pin which maintains a 5V power supply for the gate driver and control circuitry. Connect  $V_{IN}$  to the VDD pin via the current limiting series resistor  $R_{VDD}$  (see section 4.2.1 for required values). Consideration should be given to the tolerances on the VDD pin operating conditions (see section 1.2, parameter 1.2.3) and  $V_{IN}$ .

## 2.4 Input Current

The current required by the ZSLS7025 is 0.25mA (typical) plus the switching current of the external MOSFET,  $Q_1$ . The switching frequency of  $Q_1$  affects the amount of current required, as does  $Q_1$ 's gate charge requirement (found in the MOSFET manufacturer's data sheet).

$$I_{IN} \approx 0.25 \text{mA} + Q_{G} \times f_{S}$$

Where

$f_S$  = switching frequency of  $Q_1$

$Q_{\rm G}$  = gate charge of Q<sub>1</sub>

# 2.5 LED Current Control

The ZSLS7025 regulates the LED current by sensing the voltage across the external feedback resistor  $R_{FB}$  in series with the LEDs. The voltage is sensed via the FB pin where the internal feedback reference voltage  $V_{FB}$  is 0.3V (typical; see section 1.3, parameter 1.3.11). The LED current can easily be set according to equation (2).

$$I_{OUT} = \frac{V_{FB}}{R_{FB}} = \frac{0.3V}{R_{FB}}$$

(2)

Where

$I_{OUT}$  = Average output current through the LED(s) in amperes

V<sub>FB</sub> = Internal feedback reference voltage

Note: For an accurate LED current, a precision resistor is required for  $R_{FB}$  (1% is recommended).

# 2.6 Dimming Control

There are three options for LED dimming:

- DC voltage dimming control

- RC-filtered PWM signal dimming control

- PWM signal with a dimming control MOSFET(Q<sub>2</sub>)

(1)

## 2.6.1 Dimming Control Using an External DC Control Signal

The LED output current can be set below the nominal average value defined by equation (2) using an external DC voltage control signal superimposed on the FB pin as shown in the example circuit in Figure 2.2. As the DC control signal,  $V_{DC}$ , increases, the current through  $R_3$  increases with a subsequent increase in the voltage at the FB pin. This causes the ZSLS7025 to compensate by reducing the output current through the LED string. Consequently, the output current is inversely proportional to the DC control voltage.

**Note:** It is important to ensure that the LED output voltage  $V_{OUT}$  remains higher than the input voltage  $V_{IN}$  in dimming applications.

The output current controlled by the DC voltage on FB can be calculated using equation (3).

$$I_{OUT} = \frac{V_{FB} - \left(\frac{R_3 \times (V_{DC} - V_{FB})}{R_4}\right)}{R_{FB}}$$

(3)

Where

$I_{OUT}$  = Output current through the LED(s) with a DC control voltage

$V_{FB}$  = Internal feedback reference voltage (see section 1.3, parameter 1.3.11)

V<sub>DC</sub> = External DC control voltage

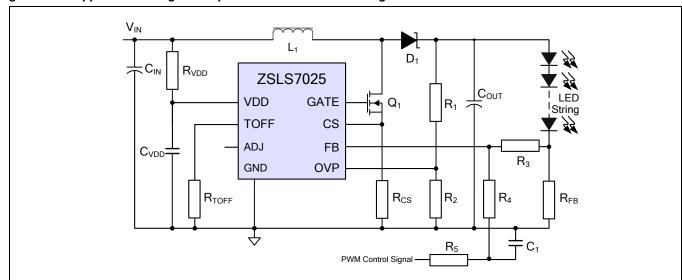

### 2.6.2 Dimming Control Using an RC Filter to Convert a PWM Signal to a DC Voltage

As shown in Figure 2.3, a filtered PWM signal can be used as an adjustable DC voltage for LED dimming control, and it functions the same as the DC control signal described in section 2.6.1. An external RC filter converts the PWM signal to a DC voltage, which is summed with the FB voltage to regulate the output current. Using a fixed frequency PWM signal and changing the duty cycle adjusts the average LED current. The LED current can be calculated with equation (4):

$$I_{OUT} = \frac{V_{FB} - \left(\frac{R_3 \times (V_{PWM} \times D_{PWM} - V_{FB})}{R_4 + R_5}\right)}{R_{FB}}$$

(4)

Where

- $I_{OUT}$  = Output current through the LED(s) with a PWM control voltage

- $V_{FB}$  = Internal feedback reference voltage (see section 1.3, parameter 1.3.11)

- V<sub>PWM</sub> = External PWM control voltage

- $D_{PWM}$  = Duty cycle of the PWM control signal

The LED current is inversely proportional to the PWM duty cycle; i.e., when the PWM signal has a 100% duty cycle, the output current is minimum, ideally zero, and when the PWM signal has a 0% duty cycle, the output current is at its maximum. See the example in section 4.4 for more details.

Note: Care must be taken to ensure that the minimum required current is not already exceeded when the LEDs are connected to  $V_{IN}$ .

#### Figure 2.3 RC Filter PWM Dimming Circuit

## 2.6.3 PWM Dimming with a Dimming Control MOSFET (Q<sub>2</sub>)

Figure 2.4 shows the configuration for using an external PWM signal with a dimming control MOSFET  $Q_2$ . When the PWM input is high (V<sub>H</sub>>2.4V),  $Q_2$  is on and the ZSLS7025 operates normally to regulate the output current. When the PWM signal is low (V<sub>L</sub><0.5V),  $Q_2$  is off; the input voltage on the FB pin will be below V<sub>FB</sub> and the ZSLS7025 is shutdown. Using a fixed frequency PWM signal and changing the duty cycle adjusts the average LED current. The recommended 5V PWM frequency is between 200Hz and 1KHz.

Figure 2.4 PWM Dimming Circuit Using a Dimming Control MOSFET (Q<sub>2</sub>)

# 2.7 Peak Input Current Control

The ZSLS7025 limits the peak inductor current and therefore the peak input current through the feedback path of  $R_{CS}$  connected from the source of the external MOSFET (Q<sub>1</sub>) to ground. The required average input current is based on the boost ratio  $V_{OUT}/V_{IN}$  and the designed value for average LED current. The required average input current can be calculated with equation (5):

$$I_{IN\_AVG} = \frac{V_{OUT} \times I_{OUT}}{V_{IN} \times \eta}$$

Where

$\eta$  = Assumed power conversion efficiency (recommended value for calculation: 0.9)

(5)

(7)

In general, setting the peak inductor current to 1.5 times the average input current is sufficient to maintain good regulation of the output current.

$$I_{\text{IN}_{\text{PEAK}}} = 1.5 \times I_{\text{IN}_{\text{AVG}}} = \frac{V_{\text{CS}_{\text{TH}}}}{R_{\text{CS}}}$$

(6)

Where

$$\begin{split} V_{CS\_TH} &= V_{ADJ}/10 \text{ if } 0.5V < V_{ADJ} \leq 2.4V \quad \text{or} \\ V_{CS\_TH} &= 0.24V \text{ if } V_{ADJ} > 2.4V \quad \text{or} \quad \text{if the ADJ pin is floating} \end{split}$$

### 2.8 Setting the Minimum Off-Time t<sub>OFF\_MIN</sub>

The ZSLS7025 operates in a pulsed frequency modulation (PFM) mode. In nominal operation, on-time and off-time are determined according to equations (8), (9), (10), and (11). In most applications, the recommended value for  $t_{OFF\_MIN}$  is 1µs. The relationship between  $t_{OFF\_MIN}$  and  $R_{TOFF}$  is shown in equation (7) and Where tOFF\_<sub>MIN</sub> is in µs and RTOFF is in  $\Omega$ .

Figure 2.5.  $t_{OFF\_MIN}$  is valid as long as VFB has not reached the threshold of 300 mV.

$$t_{OFF\_MIN} = 40 \times 10^{-12} \times R_{TOFF}$$

Where  $t_{OFF\_MIN}$  is in  $\mu$ s and  $R_{TOFF}$  is in  $\Omega$ .

# 2.9 Switching Frequency and Inductor Value

The inductance value of the inductor  $(L_1)$  directly determines the switching frequency of the converter. Under fixed conditions, the inductance is inversely proportional to the switching frequency; i.e., the larger the inductance, the lower the switching frequency. A higher switching frequency will reduce the value required for the inductor but will increase the switching loss in the external MOSFET,  $Q_1$  (see section 2.4).

<sup>© 2016</sup> Integrated Device Technology, Inc.

The switching frequency f in Hertz can be calculated from  $t_{ON}$  and  $t_{OFF}$  in seconds with equation (8).

$$f = \frac{1}{\left(t_{ON} + t_{OFF}\right)}$$

(8)

The ripple current in the inductor can be calculated with equation (9).

$$I_{RIPPLE} = 2 \times (I_{IN_{PEAK}} - I_{IN_{AVG}})$$

(9)

The  $Q_1$  on-time,  $t_{ON}$ , can be calculated with equation (10).

$$t_{ON} \approx \frac{(I_{RIPPLE} \times L_1)}{V_{IN} - I_{IN\_AVG} \times (R_L + R_{DS(ON)} + R_{CS})}$$

(10)

Where

$R_L$  = the DC resistance of inductor  $L_1$  in  $\Omega$

$R_{DS(ON)}$  = the on-resistance of  $Q_1$  in  $\Omega$  (see manufacturer's specifications)

$L_1$  = the value of the inductor  $L_1$  in Henries

The  $Q_1$  off-time,  $t_{OFF}$ , can be calculated with equation (11).

$$t_{OFF} \approx \frac{I_{RIPPLE} \times L_{1}}{V_{OUT} + V_{D} + (I_{IN_{AVG}} \times R_{L}) - V_{IN}}$$

(11)

Where

$V_D$  = the forward voltage of the diode  $D_1$  at the required load current in volts

Note: The selection of inductor  $L_1$  must ensure that  $t_{OFF}$  is longer than the  $t_{OFF\_MIN}$  as calculated in equation (7). If not, the converter cannot output the required current.

The recommended switching frequency is 20kHz < f < 200kHz. Lower than 20KHz will cause audio noise of the inductor, and a frequency that is too high will increase the switching loss in  $Q_1$ .

With a fixed V<sub>IN</sub>, V<sub>OUT</sub>, I<sub>IN\_AVG</sub>, and I<sub>IN\_PEAK</sub>, the switching frequency is inversely proportional to the inductor value.

# 2.10 DC Power Loss

The RDS (ON) of the external MOSFET, Q1, determines the DC power loss, which can be calculated with equation (12).

$$P_{DISS} \approx I_{IN\_AVG}^{2} \times R_{DS(ON)} \times D_{Q1} \approx I_{IN\_AVG}^{2} \times R_{DS(ON)} \times \left(1 - \frac{V_{IN}}{V_{OUT}}\right) \times \frac{1}{\eta}$$

(12)

Where

$D_{Q1}$  = the duty cycle for  $Q_1$

$\eta$  = Assumed power conversion efficiency (recommended value for calculation: 0.9)

<sup>© 2016</sup> Integrated Device Technology, Inc.

# **3** Operating Conditions

# 3.1 Under-Voltage Lockout

The under-voltage lockout (UVLO) function monitors the voltage on the ZSLS7025's VDD pin. If this voltage is lower than the UVLO threshold minus the UVLO hysteresis ( $V_{UVLO_TH}$  -  $V_{UVLO_HYS}$ ), the ZSLS7025 is disabled.

If the voltage on the VDD pin reaches a level higher than the UVLO threshold ( $V_{UVLO_TH}$ ), the lock-out function turns off and the ZSLS7025 is re-enabled. See parameters 1.3.2 and 1.3.3 in section 1.3 for the  $V_{UVLO_TH}$  threshold and  $V_{UVLO_HYS}$  hysteresis, respectively.

# 3.2 Over-Voltage Protection

Open-load protection is achieved through the ZSLS7025's over-voltage protection (OVP). In boost converters, an LED string failure can cause the feedback voltage ( $V_{FB}$ ) to always be zero. If this happens, the ZSLS7025 will keep boosting the output voltage higher and higher. If the output voltage reaches the programmed OVP threshold, the protection mechanism will be triggered and stop the switching action. To ensure that the circuit functions properly, the OVP setting resistor divider,  $R_1$  and  $R_2$ , must be set with appropriate values given by equation (13). The recommended OVP voltage is either 1.25 times the normal output voltage or 5V higher than the normal output voltage, whichever is higher.

$$V_{OVP} = V_{OVP_TH} \times \frac{(R_1 + R_2)}{R_2}$$

(13)

Where

$V_{OVP_TH}$  = Over-voltage input threshold: 1.0V (typical; see parameter 1.3.12 in section 1.3)  $V_{OVP}$  = Output voltage OVP level

# 4 Application Circuit Design

# 4.1 Applications

The ZSLS7025 is ideal for driving white HB-LEDs in diverse industrial, after-market automotive, and consumer lighting applications using low supply voltages, such as SELV applications. It is optimal for driving multiple white HB-LEDs connected in series so that the LED current is uniform for better brightness and color control. It features a wide input range and high output current.

Figure 4.1 demonstrates the typical application with the external components described in section 4.2. Figure 2.2, Figure 2.3, and Figure 2.4 demonstrate various dimming applications.

Figure 4.1 Typical ZSLS7025 Application Circuit

# 4.2 External Component Selection

Note: Also see section 4.3 for layout guidelines for the following external components.

# 4.2.1 Series Resistor R<sub>VDD</sub>

The ZSLS7025 has an internal 5V shunt regulator connected to the VDD pin. The  $R_{VDD}$  series resistor must be connected between the VDD pin and  $V_{IN}$  to limit current flow. See section 2.1 regarding input voltages over 100V.

# 4.2.2 Inductor L<sub>1</sub>

See section 2.9 for calculating the proper value for  $L_1$ . Select an inductor with a current rating higher than the input average current and a saturation current over the calculated peak current. To calculate the worst case inductor peak current, use the minimum input voltage, maximum output voltage, and maximum total LED current. Also ensure that the inductor has a low DCR (copper wire resistance) to minimize the  $I^2R$  power loss.

### 4.2.3 High Frequency Noise Filter Capacitor C<sub>VDD</sub>

External capacitor  $C_{VDD}$  forms a high-frequency noise filter for the VDD pin. For all configurations, use  $C_{VDD}$  to bypass the VDD pin using a low ESR capacitor (a 10µF ceramic capacitor is recommended) to provide a high frequency path to GND.

#### 4.2.4 Input Capacitor C<sub>IN</sub>

The  $C_{IN}$  input capacitor connected to  $V_{IN}$  will supply the transient input current for the power inductor. A value of 100µF or higher is recommended to prevent excessive input voltage ripple. Also see section 4.2.3.

### 4.2.5 Output Capacitor C<sub>OUT</sub> for Reducing Output Ripple

The output capacitor ( $C_{OUT}$ ) holds the output current while the  $Q_1$  external MOSFET turns ON. This capacitor directly impacts the line regulation and the load regulation.

Using a low ESR capacitor can minimize output ripple voltage and improve output current regulation. For most applications, a 220µF low ESR capacitor will be sufficient. Proportionally lower ripple can be achieved with higher capacitor values.

#### 4.2.6 Schottky Rectifier Diode D<sub>1</sub>

The  $D_1$  external diode for the ZSLS7025 should be a Schottky diode with a low forward voltage drop and fast switching speed. The diode's average current rating must exceed the application's average output current. The diode's maximum reverse voltage rating must exceed the over-voltage protection of the application. For PWM dimming applications, note the reverse leakage of the Schottky diode. Lower leakage current will drain the output capacitor less during PWM low periods, allowing for higher PWM dimming ratios.

#### 4.2.7 External MOSFET Q<sub>1</sub>

The Q<sub>1</sub> external MOSFET must have a V<sub>DS</sub> rating that exceeds the maximum over-voltage protection (OVP) level configured for the application. The V<sub>GS(th)</sub> of the MOSFET should be not higher than 4V. The MOSFET's current rating must be higher than the input peak current ( $I_{IN\_PEAK}$ ). Determine the power dissipation within Q<sub>1</sub> and check if the thermal resistance of the MOSFET package causes the junction temperature to exceed maximum ratings. Also see section 2.10 regarding the effect of the MOSFET R<sub>DS(ON)</sub> on DC power loss.

# 4.3 Application Circuit Layout Requirements

The guidelines in this section are strongly recommended when laying out application circuits. As for all switching power supplies, especially those providing high current and using high switching frequencies, layout is an important design step. If the layout is not well-designed, the regulator could show instability as well as EMI problems. For additional guidelines, refer to the IDT application note *PCB Layout Design Guidelines for LED Driver Circuits* available at <a href="http://www.IDT.com">http://www.IDT.com</a>.

- Wide traces should be used for connection of the high current loop to minimize the EMI and unnecessary loss.

- The external components ground should be connected to the ZSLS7025 ground and should be as short as

possible. It is especially important that the R<sub>FB</sub> ground to ZSLS7025 ground connection is as short and wide as

possible to have an accurate LED current.

- The capacitors C<sub>IN</sub>, C<sub>VDD</sub>, and C<sub>OUT</sub> should be placed as close as possible to the ZSLS7025 for good filtering. It is especially important that the C<sub>OUT</sub> output capacitor connection is as short and wide as possible.

- The Q<sub>1</sub> external MOSFET drain is a fast switching node (also applies to Q<sub>2</sub> if the PWM is accomplished with a dimming control MOSFET as described in section 2.6.3). The inductor L<sub>1</sub> and Schottky diode D<sub>1</sub> should be placed as close as possible to the drain, and the connection should be kept as short and wide as possible. Avoid other traces crossing and routing too long in parallel with this node to minimize the noise coupling into these traces. The feedback pins (i.e., CS, FB, OVP) should be as short as possible and routed away from the inductor, Schottky diode, and Q<sub>1</sub>. The feedback pins and feedback network should be shielded with a ground plane or trace to minimize noise coupling into this circuit.

- The thermal pad on the back of the external MOSFET package must be soldered to the large ground plane for ideal heat distribution.

# 4.4 Application Example

This section provides an example of an application design for the ZSLS7025 for the RC-filter PWM application described in section 2.6.2 and shown again for reference in Figure 4.2.

Design criteria:

$V_{\text{IN}}$  = 12 to 24 V  $I_{\text{OUT}}$  = 350mA  $V_{\text{OUT}}$  = 30 to 40V (9 to 12 LEDs, Vf = 3.3V)

To calculate the worst case parameters, use the minimum input voltage, maximum output voltage, and maximum output current; i.e.,  $V_{IN} = 12V$ ,  $I_{OUT} = 350$ mA, and  $V_{OUT} \approx 40V$  (12 LEDs, Vf = 3.3V).

Figure 4.2 Application Design Example – RC Filter PWM Dimming Circuit

### 4.4.1 Selecting R<sub>VDD</sub>, C<sub>IN</sub>, and C<sub>VDD</sub>

Assume I<sub>IN</sub> = 2.5mA.

$$\mathsf{R}_{\mathsf{VDD}} = \frac{\mathsf{V}_{\mathsf{IN}} - \mathsf{V}_{\mathsf{DD}}}{\mathsf{I}_{\mathsf{IN}}} \approx 3\mathsf{k}\Omega \tag{14}$$

→ Choose  $C_{IN}$  as 220µF/35V and  $C_{VDD}$  as 10µF/16V.

### 4.4.2 Selecting R<sub>TOFF</sub> to Set Minimum t<sub>OFF</sub>

The recommended value for toFF\_MIN is 1µs.

$$t_{OFF\_MIN} = 40 \times 10^{-12} \times R_{TOFF} = 1\mu s$$

(15)

→ Choose  $R_{TOFF} = 24k\Omega$ .

### 4.4.3 Selecting R<sub>FB</sub> to Set Output Current and C3

$$R_{FB} = \frac{V_{FB_TH}}{I_{OUT}} \approx 0.86\Omega$$

(16)

→ Choose C3 =  $220\mu$ F/63V (low ESR electrolytic capacitor).

© 2016 Integrated Device Technology, Inc.

### 4.4.4 Selecting $R_3$ , $R_4$ , $R_5$ and $C_1$

$R_3$ ,  $R_4$ , and  $R_5$  can be obtained by

$$I_{OUT} = \frac{V_{FB} - \left(\frac{R_3 \times (V_{PWM} \times D_{PWM} - V_{FB})}{R_4 + R_5}\right)}{R_{FB}}$$

(17)

Substitute  $D_{PWM}$ =100%,  $V_{PWM}$ = 5V, and  $I_{OUT}$ =0 in the equation, and the result is

$$0 = \frac{0.3 - \left(\frac{R_3 \times (5 \times 100\% - 0.3)}{R_4 + R_5}\right)}{0.86}$$

(18)

which can be simplified to

15.66 x

$$R_3 = R_4 + R_5$$

The low pass filter formed by  $R_5$  and  $C_1$  must have a corner frequency much lower than the PWM frequency. As the corner frequency of the filter decreases, the response time of the LED current to changes in PWM increases. Choose a corner frequency 50 times lower than f<sub>PWM</sub>.

$$R_5 \times C_1 \ge \frac{50}{2\pi f_{PWM}}$$

(19)

Assume f<sub>PWM</sub> is 200Hz (or higher) and choose  $C_1 = 0.1\mu$ F, and the result is  $R_5 \ge 400$ k $\Omega$ .

→ Choose C4 =  $0.1\mu$ F, R<sub>5</sub> = 400k $\Omega$ .

Choose a nominal value for  $R_4$ , and then calculate  $R_3$ .

→ Choose  $R_4 = 10k\Omega$ , then  $R_3 = 26.2k\Omega$ .

Substitute  $D_{PWM}=0$ ,  $V_{PWM}=5V$  and  $I_{OUT}=350$ mA in the equation, and the result is

$$I_{OUT} = \frac{V_{FB} - \left(\frac{R_3 \times (V_{PWM} \times D_{PWM} - V_{FB})}{R_4 + R_5}\right)}{R_{FB}} = \frac{0.3 - \left(\frac{26.2 \times (5 \times 0\% - 0.3)}{400 + 10}\right)}{R_{FB}} = 0.35A$$

(20)

So,  $R_{FB} = 0.91\Omega$ . (With the RC filter PWM dimming,  $R_{FB}$  will be different than in the no dimming application shown in Figure 2.1.)

### 4.4.5 R<sub>CS</sub> for Setting Input Peak Current

Assume that

$$I_{IN\_PEAK} = 1.5 \times I_{IN\_AVG} = 1.5 \times \frac{V_{OUT} \times I_{OUT}}{V_{IN} \times \eta}$$

$$= 1.5 \times \frac{40 \times 0.35}{12 \times 0.9} \approx 1.95A$$

(21)

Where  $\eta$  is the assumed power conversion efficiency (the recommended value for this calculation is 0.9)

$$R_{CS} = \frac{V_{CS} - TH}{I_{IN} - PEAK} = 0.123\Omega$$

(22)

→ Choose  $R_{CS} = 0.123\Omega$ ,  $I_{IN_{PEAK}} = 1.95A$

#### 4.4.6 L<sub>1</sub> for Setting the Frequency

Input average current:

$$I_{IN\_AVG} = \frac{V_{OUT} \times I_{OUT}}{V_{IN} \times \eta} = 1.3A$$

(23)

The ripple current in the inductor:

$I_{RIPPLE} = 2 \times (I_{IN_{PEAK}} - I_{IN_{AVG}}) = 1.3A$ (24)

According to  $t_{OFF} > t_{OFF\_MIN}$ :

$$t_{OFF} = \frac{I_{RIPPLE} \times L_1}{V_{OUT} + V_D + (I_{IN\_AVG} \times R_L) - V_{IN}} > 1\mu s$$

(25)

This gives  $L_1 > 22\mu H$ .

Assume  $L_1$  = 22µH and  $R_L$  +  $R_{DS(ON)}$  +R\_{CS}=0.4 $\Omega$

$$t_{ON} = \frac{(I_{RIPPLE} \times L_1)}{V_{IN} - I_{IN} \times (R_L + R_{DS(ON)} + R_{CS})} \approx 2.5 \mu s$$

(26)

Then the assumed switching frequency:

$$f' = \frac{1}{\left(t_{ON} + t_{OFF}\right)} \approx 285 \text{kHz}$$

(27)

© 2016 Integrated Device Technology, Inc.

The recommended switching frequency, 20KHz < f < 200KHz, according to the switching frequency, is inversely proportional to the inductor value; for example, select  $L_1$ =100 µH.

Therefore

$$f = f' \times \frac{22}{100} \approx 63 \text{kHz}$$

The saturation current of the inductor must exceed the input peak current ( $I_{IN PEAK}$ ).

#### 4.4.7 R<sub>1</sub> and R<sub>2</sub> for Setting OVP

Set VOVP = VOUT + 5V = 45V

$$V_{OVP} = V_{OVP_TH} \times \frac{(R_1 + R_2)}{R_2}$$

(29)

→Choose  $R_2 = 10k\Omega$ , then  $R_1 = 470k\Omega$ .

#### 4.4.8 **Q<sub>1</sub> External MOSFET and D<sub>1</sub> Diode**

Power losses in the Q1 external MOSFET should be minimized. Conduction losses increase with RDS(on), and switching losses increase with gate/drain charge and frequency. Therefore, selecting a MOSFET with low RDS(on) and low gate/drain charge for the Q<sub>1</sub> external MOSFET will help to optimize efficiency.

The MOSFET's current rating must be higher than the input peak current IIN PEAK. Q1 must have a VDS rating that exceeds the maximum over-voltage protection (OVP) level configured for the application.

The average and peak current of the diode D<sub>1</sub> must exceed the output average current and input peak current. The diode's maximum reverse voltage rating must exceed the over-voltage protection of the application.

(28)

# 5 ESD Protection

All pins have an ESD protection of  $\ge \pm 3500$ V according to the Human Body Model (HBM). The ESD test follows the Human Body Model based on MIL 883-H, Method 3015.8.

# 6 Pin Configuration and Package

#### Table 6.1Pin Description SOP-8

| Pin Name | NO.                                                                                                                                                                                                                                                                                                                                                                                                                                               | Description                                                                                                                                                                           |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VDD      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Positive power supply input pin. Internally clamped at 5V (typical).                                                                                                                  |  |

| TOFF     | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Pin for setting off time. An external resistor, $R_{TOFF}$ , connected to this pin forms an RC discharge path to generate the constant minimum off time of the $Q_1$ external MOSFET. |  |

| ADJ      | $ \begin{array}{c} \mbox{Enable and input peak current control pin.} \\ \mbox{3} \end{array} \begin{array}{c} \mbox{Enable and input peak current control pin.} \\ \mbox{This pin is pulled up to 4.5V internally to set $V_{CS_TH} = 0.24V$ if ADJ$ is floating. If $V_{ADJ} < 0.5V$, the $Q_1$ external $MOSFET$ shuts down. If $0.5 \le V_{ADJ} \le 2.4V$, $V_{CS_TH} = V_{ADJ}/10$. If $V_{ADJ} > 2.4V$, $V_{CS_TH} = 0.24V$. } \end{array} $ |                                                                                                                                                                                       |  |

| GND      | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Ground.                                                                                                                                                                               |  |

| GATE     | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Driver's output for the gate of the Q <sub>1</sub> external MOSFET.                                                                                                                   |  |

| CS       | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Current sense input for the boost, peak-current control loop.                                                                                                                         |  |

| FB       | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Feedback voltage input pin. Used to regulate the current of the LEDs by keeping $V_{FB}$ =0.3V.                                                                                       |  |

| OVP      | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Overvoltage protection input pin. If the voltage at OVP exceeds the over-voltage input threshold, $V_{OVP_TH}$ , the GATE output shuts down.                                          |  |

| SOP-8 Package Dimensions (mm, except $\theta$ ) |                           |    |               |  |  |  |

|-------------------------------------------------|---------------------------|----|---------------|--|--|--|

| Α                                               | A 1.550 ± 0.200 E 3.900 ± |    | 3.900 ± 0.100 |  |  |  |

| A1                                              | 0.175 ± 0.075             | E1 | 6.000 ± 0.200 |  |  |  |

| A2                                              | <b>1.450 Typical e</b>    |    | 1.270 Typical |  |  |  |

| b                                               | $0.420 \pm 0.090$         | L  | 0.835 ± 0.435 |  |  |  |

| С                                               | 0.214 ± 0.036             | θ  | 4° ± 4°       |  |  |  |

| D                                               | $4.900 \pm 0.200$         |    |               |  |  |  |

# 7 Glossary

| Term         | Description                 |  |

|--------------|-----------------------------|--|

| НВ           | High Brightness             |  |

| OTP          | Over-Temperature Protection |  |

| OVP          | Over-Voltage Protection     |  |

| RS Flip-Flop | Reset-Set Flip-Flop         |  |

| UVLO         | Under-Voltage Lockout       |  |

# 8 Ordering Information

| Product Sales Code | Description                                                 | Package |

|--------------------|-------------------------------------------------------------|---------|

| ZSLS7025ZI1R       | ZSLS7025 – Boost LED Driver SOP-8 (Tape & Re                |         |

| ZSLS7025KIT-D1     | ZSLS7025PCB-D1 Demo Board, 1 ZLED-PCB10, and 5 ZSLS7025 ICs | Kit     |

# 9 Document Revision History

| Revision | Date           | Description              |

|----------|----------------|--------------------------|

| 1.00     | June 28, 2012  | First issue.             |

|          | April 20, 2016 | Changed to IDT branding. |

Corporate Headquarters 6024 Silver Creek Valley Road San Jose, CA 95138 www.IDT.com Sales 1-800-345-7015 or 408-284-8200 Fax: 408-284-2775 www.IDT.com/go/sales Tech Support www.IDT.com/go/support

DISCLAIMER Integrated Device Technology, Inc. (IDT) reserves the right to modify the products and/or specifications described herein at any time, without notice, at IDT's sole discretion. Performance specifications and operating parameters of the described products are determined in an independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are trademarks or registered trademarks of IDT and its subsidiaries in the United States and other countries. Other trademarks used herein are the property of IDT or their respective third party owners. For datasheet type definitions and a glossary of common terms, visit <u>www.idt.com/go/glossary</u>. All contents of this document are copyright of Integrated Device Technology, Inc. All rights reserved.