#### **FEATURES AND BENEFITS**

- High-speed analog, A-to-D converter (ADC), and digital architectures, enabling user-selectable bandwidth for speed-sensitive applications

- □ 4-phase chopper stabilization, which minimizes offset drift across temperature range

- □ 16-bit, high update rate ADC

- · Automotive AEC-Q100 qualified

- Exceptional stability throughout lifetime and across temperature changes

- ☐ Factory-configured using multisegment temperature compensation to give a flat baseline across operating temperature range

- □ Customer configurability for 1<sup>st</sup> and 2<sup>nd</sup> order sensitivity and 1<sup>st</sup> order offset compensation across temperature range

- ☐ Integrated feedback coil compensates for drift throughout product lifetime

Continued on the next page...

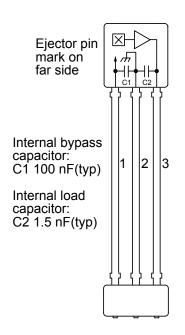

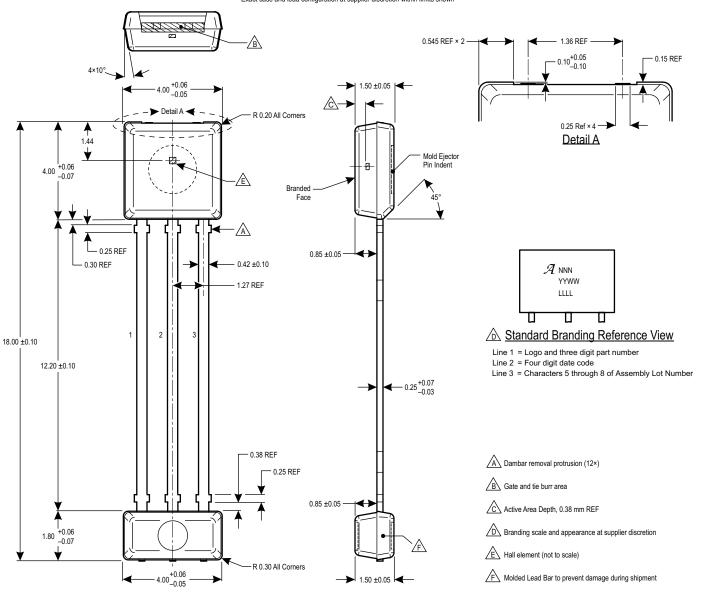

# PACKAGE: 3-pin SIP (suffix UC) Not to scale

#### **DESCRIPTION**

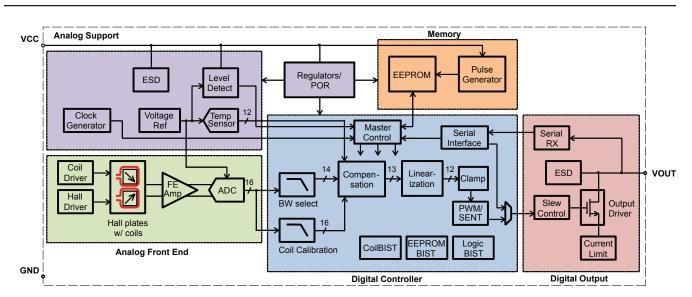

The A1342 device is a high-precision, programmable Hall-effect linear sensor integrated circuit (IC) with an open-drain output, for both automotive and nonautomotive applications. The signal path of the A1342 provides flexibility through external programming that allows the generation of an accurate, and customized, output from an input magnetic signal.

The A1342 is an especially configurable and robust solution for the most demanding linear field sensor applications. The BiCMOS, monolithic IC incorporates a Hall sensing element, precision temperature-compensating circuitry to reduce the intrinsic sensitivity and offset drift of the Hall element, a small-signal high-gain amplifier, proprietary dynamic offset cancellation circuits, advanced output linearization circuitry, and advanced diagnostics. The A1342 provides an unmatched level of customer-programmable options.

A key feature of the A1342 is its ability to produce a highly linear device output for nonlinear input magnetic fields. To achieve this, the device features 16-segment customer-programmable linearization, where a unique linearization coefficient factor is applied to each segment. Linearization coefficients are stored in a look-up table in EEPROM.

The A1342 has two configurable output options: SENT or PWM. In addition to SAEJ2716, the A1342 includes two additional proprietary SENT options: SSENT and ASENT. Both protocols enable bus configurations with up to four devices on one SENT line to reduce system costs. SSENT provides sequential

Continued on the next page...

**Functional Block Diagram**

### A1342

### Programmable Linear Hall IC with Advanced Diagnostics for Safety-Critical Applications

#### **Description (continued)**

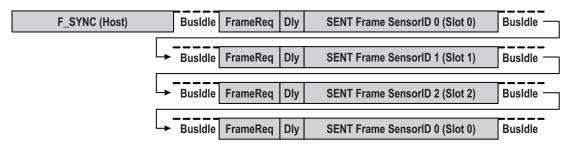

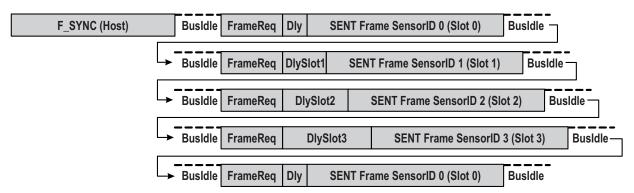

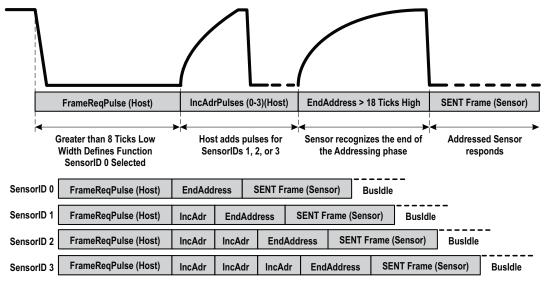

access to the sensors connected to the same line. SSENT provides a very low overhead method to maximize the sensor bandwidth on this single SENT line, minimizing impact on system performance. ASENT provides random access to all the sensors on the common SENT line. Both protocols allow individual sensors on the same line to enter diagnostic mode while the other sensors continue to

respond to queries, allowing for the highest diagnostic coverage while maintaining 100% availability of the sensor solution.

The A1342 is available in a through-hole, lead (Pb) free 3-pin SIP package (UC suffix), with 100% matte-tin leadframe plating.

#### Features and Benefits (continued)

- Wide operating flexibility to meet any application:

- $\Box$  Input field range up to  $\pm 1500~G$

- □ Rail to negative rail offset configurability

- ☐ High-precision, full output range high and low clamps

- ☐ Integrated linearization allows for flexible output waveform translation and compensation for nonlinear magnetic inputs

- ☐ Integrated capacitors offer extremely robust ESD performance and enhanced EMC performance

- Advanced diagnostic-focused features enabling easier systemlevel ASIL compliance

- ☐ Full data path validation through active front-end stimulation with internal magnetic coil; this method validates all relevant transistors for device operation

- □ Logic Built-In Self Test (LBIST) on-demand to validate the digital subsystem

- ☐ Large suite of configurable fault monitors provide system level fault detection, including:

- ♦ Overvoltage or undervoltage

- ♦ Overtemperature

- ♦ Magnetic Field Out of Range detection

- ♦ Broken wire detection

- Flexible output protocols with up to 12-bit resolution and configurable error notifications

- Digital open-drain output allows for flexible output voltage levels

- ☐ PWM (Pulse-Width-Modulated) output with diagnostic output mode to identify fault conditions

- ☐ SENT (Single Edge Nibble Transmission) compliant output with configurable reporting of error conditions and other diagnostic information

- Proprietary Fast SENT provides increased data rates to support high-bandwidth applications

- Device-shared SENT protocol as SSENT (Sequential SENT) and ASENT (Addressable SENT) allows user to connect up to four devices on the same output line for faster communication.

- ☐ Enhanced EMC tuning through programmable fall-time configurability

- Integrated EEPROM enables a high level of configurability and product traceability

- ☐ Customer-reserved area allows on-board storage of unique lot and date code information

- ☐ Robust EEPROM with Single Error Correction and Double Error Detection (SECDED) capability

- □ Integrated charge pump allows in-application programming without any requirement for high voltages to be supplied to the device during programming

### A1342

# Programmable Linear Hall IC with Advanced Diagnostics for Safety-Critical Applications

#### **SELECTION GUIDE**

| Part Number  | Packing [1]                 |

|--------------|-----------------------------|

| A1342LUCTN-T | 4000 pieces per 13-in. reel |

#### **Table of Contents**

| Functional Block Diagram         | 1  | Linear Output Protocols            | 18 |  |

|----------------------------------|----|------------------------------------|----|--|

| Specifications                   | 4  | PWM Output Mode (outmsg_mode = 0)  | 18 |  |

| Absolute Maximum Ratings         | 4  | SENT Output Modes                  | 20 |  |

| Thermal Characteristics          | 4  | Message Structure                  | 20 |  |

| Pinout Diagram and Terminal List | 4  | Optional Short Serial Message      | 21 |  |

| Operating Characteristics        | 5  | Data Nibble Format                 | 21 |  |

| Magnetic Characteristics         | 7  | Checksum (CRC) Nibble              | 22 |  |

| Accuracy Characteristics         | 8  | Output Driver Fall Time Selection  | 22 |  |

| Programmable Characteristics     | 9  | SAEJ2716 SENT and TSENT            | 24 |  |

| Application Information          | 10 | SSENT Addressing Protocol          | 27 |  |

| Signal Path                      | 11 | SSENT Function Pulses              | 28 |  |

| Compansation Block               | 11 | ASENT Addressing Protocol          | 30 |  |

| Linearization                    | 12 | ASENT Function Pulses              | 31 |  |

| Post-Linearization Trim          | 14 | Serial Communication               | 31 |  |

| Clamp                            | 14 | Programming Information            | 32 |  |

| Diagnostic Conditions            | 15 | Serial Interface Message Structure | 35 |  |

| Diagnostic Modes                 | 15 | Read and Write Transmission        | 36 |  |

| Diagnostic Configuration         | 15 | CRC                                | 36 |  |

| Analog Signal Path               | 15 | Customer Factory Access            | 37 |  |

| BIST                             | 16 | Customer Memory Lock               | 37 |  |

| ADC Overflow                     | 17 | EEPROM Margin Checking             | 37 |  |

| Undervoltage Detection and Reset | 17 | Memory Address Map                 | 38 |  |

| Broken Ground Detection          | 17 | Programmable Parameter Reference   | 43 |  |

| EEPROM Diagnostics               | 17 | Package Outline Drawing            | 47 |  |

|                                  |    |                                    |    |  |

<sup>&</sup>lt;sup>1</sup> Contact Allegro<sup>™</sup> for additional packing options

#### **SPECIFICATIONS**

#### **ABSOLUTE MAXIMUM RATINGS**

| Characteristic                | Symbol                   | Notes                                                                 | Rating     | Unit |

|-------------------------------|--------------------------|-----------------------------------------------------------------------|------------|------|

| Forward Supply Voltage        | V <sub>CC</sub>          |                                                                       | 20         | V    |

| Reverse Supply Voltage        | V <sub>RCC</sub>         |                                                                       | -16        | V    |

| Forward Supply Current        | I <sub>CC</sub>          |                                                                       | 30         | mA   |

| Reverse Supply Current        | I <sub>RCC</sub>         |                                                                       | -30        | mA   |

| Forward Output Voltage        | V <sub>OUT</sub>         |                                                                       | 20         | V    |

| Reverse Output Voltage        | V <sub>ROUT</sub>        |                                                                       | -1         | V    |

| Output Short-Circuit Current  | I <sub>OUTSC(SINK)</sub> | V <sub>CC</sub> to V <sub>OUT</sub> , 4.5 V < V <sub>CC</sub> < 5.5 V | -20        | mA   |

| Operating Ambient Temperature | T <sub>A</sub>           | L temperature range                                                   | -40 to 150 | °C   |

| Maximum Junction Temperature  | T <sub>J</sub> (max)     |                                                                       | 165        | °C   |

| Storage Temperature           | T <sub>stg</sub>         |                                                                       | -65 to 165 | °C   |

#### THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic             | Symbol          | Test Conditions [1]                            | Value | Unit |

|----------------------------|-----------------|------------------------------------------------|-------|------|

| Package Thermal Resistance | $R_{\theta JA}$ | 1-layer PCB with copper limited to solder pads | 201   | °C/W |

<sup>[1]</sup> Additional thermal information available on the Allegro website.

#### PINOUT DIAGRAM AND TERMINAL LIST TABLE

#### **Terminal List Table**

| Number | Name | Function               |

|--------|------|------------------------|

| 1      | VCC  | Input power supply [2] |

| 2      | GND  | Ground                 |

| 3      | VOUT | Output signal          |

[2] Allegro offers LDOs well-suited for regulated sensor applications. For available devices, visit www.allegromicro.com/en/Products/ Regulators-And-Lighting/Single-Output-Regulators, or contact your local Allegro sales representative.

Package UC, 3-Pin SIP Pinout Diagram

#### **OPERATING CHARACTERISTICS:** Valid $T_A$ and $V_{CC}$ , unless otherwise specified

| Characteristics                        | Symbol                   | Test Conditions                                                                            | Min. | Тур. | Max. | Unit |

|----------------------------------------|--------------------------|--------------------------------------------------------------------------------------------|------|------|------|------|

| ELECTRICAL CHARACTERISTIC              | s                        |                                                                                            | ,    | •    | •    |      |

| Supply Voltage                         | V <sub>CC</sub>          |                                                                                            | 4.5  | 5    | 5.5  | V    |

| Supply Current                         | I <sub>CC</sub>          | Compensation coil off                                                                      | _    | _    | 10   | mA   |

| Peak Supply Current                    | I <sub>CC(pk)</sub>      | Compensation coil on                                                                       | _    | _    | 16   | mA   |

| Reverse Supply Current                 | I <sub>RCC</sub>         | V <sub>CC</sub> = -16 V, T <sub>A</sub> = 25°C                                             | -3   | _    | _    | mA   |

| Supply Zener Clamp Voltage             | V <sub>ZSUPPLY</sub>     | I <sub>CC</sub> = 13 mA, compensation coil off, T <sub>A</sub> = 25°C                      | 20   | _    | _    | V    |

| Channing Fraguency                     | £                        | T <sub>A</sub> = 25°C, compensation coil off                                               | _    | 128  | _    | kHz  |

| Chopping Frequency                     | f <sub>C</sub>           | T <sub>A</sub> = 25°C, compensation coil on                                                | _    | 64   | _    | kHz  |

| Oscillator Frequency                   | f <sub>OSC</sub>         | T <sub>A</sub> = 25°C                                                                      | 6963 | 8192 | 9421 | kHz  |

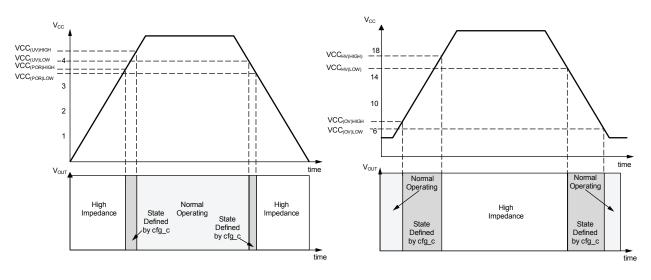

| Lindam rollings Datastian Throshold    | V <sub>CC(UV)LOW</sub>   | V <sub>CC</sub> falling, see Figure 1                                                      | 4    | _    | 4.35 | V    |

| Undervoltage Detection Threshold       | V <sub>CC(UV)HIGH</sub>  | V <sub>CC</sub> rising, see Figure 1                                                       | 4.05 | _    | 4.4  | V    |

| Develop On Board Through ald           | V <sub>CC(POR)LOW</sub>  | V <sub>CC</sub> falling, see Figure 1                                                      | 3.4  | _    | 3.8  | V    |

| Power-On-Reset Threshold               | V <sub>CC(POR)HIGH</sub> | V <sub>CC</sub> rising, see Figure 1                                                       | 3.5  | _    | 3.9  | V    |

|                                        | V <sub>CC(OV)LOW</sub>   | V <sub>CC</sub> falling, see Figure 1                                                      | 6.6  | _    | 7.4  | V    |

| Overvoltage Detection Threshold        | V <sub>CC(OV)HIGH</sub>  | V <sub>CC</sub> rising, see Figure 1                                                       | 6.7  | _    | 7.6  | V    |

|                                        | V <sub>CC(HV)LOW</sub>   | V <sub>CC</sub> falling, see Figure 1                                                      | 15   | _    | _    | V    |

| High-Voltage Threshold                 | V <sub>CC(HV)HIGH</sub>  | V <sub>CC</sub> rising, see Figure 1                                                       | _    | _    | 17   | V    |

| OUTPUT CHARACTERISTICS                 | , , ,                    |                                                                                            |      |      |      |      |

|                                        |                          | bw_sel_c = 0                                                                               | _    | 40   | _    | Hz   |

|                                        |                          | bw_sel_c = 1                                                                               | _    | 160  | _    | Hz   |

| Bandwidth [1]                          | BW                       | bw_sel_c = 2                                                                               | _    | 680  | _    | Hz   |

|                                        |                          | bw_sel_c = 3                                                                               | _    | 3000 | _    | Hz   |

|                                        |                          | bw_sel_c = 4-7                                                                             | _    | 7400 | _    | Hz   |

|                                        |                          | bw_sel_c = 0, T <sub>A</sub> = 25°C, coil_freq = 0,<br>coilcomp_dis = 0, bw_sel_comp_c = 0 | _    | 0.32 | _    | G    |

|                                        |                          | bw_sel_c = 1, T <sub>A</sub> = 25°C, coil_freq = 0,<br>coilcomp_dis = 0, bw_sel_comp_c = 0 | _    | 0.50 | _    | G    |

| Noise (Peak-to-Peak)[2]                | OUT <sub>N(PK-PK)</sub>  | bw_sel_c = 2, T <sub>A</sub> = 25°C, coil_freq = 0,<br>coilcomp_dis = 0, bw_sel_comp_c = 0 | _    | 0.93 | _    | G    |

|                                        |                          | bw_sel_c = 3, T <sub>A</sub> = 25°C, coil_freq = 0,<br>coilcomp_dis = 0, bw_sel_comp_c = 0 | _    | 1.74 | _    | G    |

|                                        |                          | bw_sel_c = 4, T <sub>A</sub> = 25°C, coil_freq = 0,<br>coilcomp_dis = 0, bw_sel_comp_c = 0 | _    | 2.85 | _    | G    |

| Output Leakage Current                 | I <sub>OUT</sub>         | Output voltage ≤ 5.5 V, output FET off                                                     | _    | _    | 100  | μΑ   |

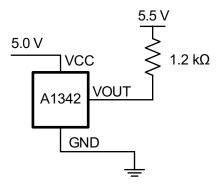

| Output Load Resistance                 | R <sub>L(PULLUP)</sub>   | Output current ≥ –10 mA                                                                    | 1.2  | _    | -    | kΩ   |

| Output Saturation Voltage              | V <sub>OUT(Sat)</sub>    | Output current = –4.7 mA, V <sub>CC</sub> = 5 V,<br>Output FET on                          | _    | _    | 0.35 | V    |

| Output Current Limit                   | I <sub>LIMIT</sub>       | Output FET on, T <sub>A</sub> = 25°C                                                       | 20   | 30   | 50   | mA   |

| Output Zener Clamp Voltage             | V <sub>ZOUT</sub>        | T <sub>A</sub> = 25°C, output current = -3 mA                                              | 20   | _    | _    | V    |

| Internal Load Capacitor <sup>[3]</sup> | C <sub>LI</sub>          | T <sub>A</sub> = 25°C                                                                      | _    | 1.5  | _    | nF   |

| External Load Capacitor                | C <sub>LX</sub>          |                                                                                            | _    | _    | 4.7  | nF   |

Continued on the next page...

#### OPERATING CHARACTERISTICS (continued): Valid T<sub>A</sub> and V<sub>CC</sub>, unless otherwise specified

| Characteristics                          | Symbol             | Test Conditions                                                  | Min.        | Тур. | Max. | Unit |

|------------------------------------------|--------------------|------------------------------------------------------------------|-------------|------|------|------|

|                                          |                    | bw_sel_c = 4-7                                                   | -           | 0.15 | _    | ms   |

|                                          |                    | bw_sel_c = 3                                                     | -           | 0.25 | _    | ms   |

| Output Response Time <sup>[4]</sup>      | t <sub>resp</sub>  | bw_sel_c = 2                                                     | _           | 0.69 | _    | ms   |

|                                          |                    | bw_sel_c = 1                                                     | -           | 2.4  | _    | ms   |

|                                          |                    | bw_sel_c = 0                                                     | -           | 9.3  | _    | ms   |

|                                          |                    | bw_sel_c = 4-7                                                   | _           | 0.6  | _    | ms   |

|                                          | t <sub>PO</sub>    | bw_sel_c = 3                                                     | _           | 0.75 | _    | ms   |

| Power-On Time <sup>[4]</sup>             |                    | bw_sel_c = 2                                                     | _           | 1.25 | _    | ms   |

|                                          |                    | bw_sel_c = 1                                                     | -           | 3.7  | -    | ms   |

|                                          |                    | bw_sel_c = 0                                                     | _           | 13   | -    | ms   |

| Outrat litter DIA/A/[1]                  | 5,,,,,             | outmsg_mode = 0, SENT_PWM_RATE < 2 kHz                           | -1          | -    | 1    | LSB  |

| Output Jitter, PWM <sup>[1]</sup>        | PWM <sub>JIT</sub> | outmsg_mode = 0, SENT_PWM_RATE ≥ 2 kHz                           | -3          | -    | 3    | LSB  |

| Output, Integral Nonlinearity            | INL                | outmsg_mode = 0, SENT_PWM_RATE < 2 kHz                           | _           | ±0.5 | -    | %FSO |

|                                          |                    | T <sub>A</sub> = 25°C, outmsg_mode = 1-5                         | _           | 12   | _    | bit  |

| Maximum Output Resolution <sup>[5]</sup> | OUT <sub>RES</sub> | T <sub>A</sub> = 25°C, outmsg_mode = 0,<br>SENT_PWM_RATE ≤ 2 kHz | _           | 12   | _    | bit  |

| PWM Carrier Frequency <sup>[6]</sup>     | f <sub>PWM</sub>   |                                                                  | <b>–</b> 15 | -    | 15   | %    |

<sup>[1]</sup> Determined from design characterization; not tested in production.

<sup>[6]</sup> PWM carrier frequency accuracy is % of the programming target. See programmable parameter reference for PWM carrier frequency programming options.

Figure 1: V<sub>CC</sub> Thresholds and Resultant Output States

<sup>[2]</sup> Noise (Peak-to-Peak) calculated as 6 sigma (6 standard deviations) from characterization of a small sample of devices. Conversion of noise from gauss to LSB can be done by: Noise (G) × Sensitivity (LSB/G) = Noise (LSB)

<sup>[3]</sup> Capacitor internal to device package between VOUT and GND. Capacitor specifications are determined by the manufacturer.

<sup>[4]</sup> Defined as time before magnetic data is 90% of the settled value.

<sup>[5]</sup> When outmsg\_mode = 0, the maximum output resolution decreases to 11 - n (bits) for SENT\_PWM\_RATE = 2 kHz × 2<sup>n</sup>.

### A1342

# Programmable Linear Hall IC with Advanced Diagnostics for Safety-Critical Applications

#### **MAGNETIC CHARACTERISTICS:** Valid at $T_A = 25$ °C and $V_{CC} = 5$ V, unless otherwise specified

| Characteristics          | Symbol               | Test Conditions               | Min.  | Тур.   | Max. | Unit <sup>[1][2]</sup> |

|--------------------------|----------------------|-------------------------------|-------|--------|------|------------------------|

| Input Field Range        | B <sub>IN</sub>      |                               | -1500 | _      | 1500 | G                      |

| Initial Sensitivity      | SENS <sub>INIT</sub> |                               | _     | 0.0333 | _    | %FSO/G                 |

| Initial Quiescent Output | QO <sub>INIT</sub>   |                               | _     | 50     | -    | %FSO                   |

|                          | OUT <sub>CLP</sub>   | clampl = 0, outmsg_mode = 1-5 | _     | 0      | -    | LSB                    |

| Initial Output Clamp     | (L)INIT              | clampl = 0, outmsg_mode = 0   | -     | 2      | -    | %D                     |

| Initial Output Clamp     | OUT <sub>CLP</sub>   | clamph = 0, outmsg_mode = 1-5 | -     | 4095   | -    | LSB                    |

|                          | (H)INIT              | clamph = 0, outmsg_mode = 0   | _     | 98     | _    | %D                     |

<sup>[1] 1</sup> G (gauss) = 0.1 mT (millitesla).

<sup>[2]</sup> FSO means Full Scale Output. See Definitions of Terms section.

#### $\textbf{ACCURACY CHARACTERISTICS:} \ \ \text{Valid at T}_{A} \ \text{and V}_{CC}, \ \text{unless otherwise specified}$

| Characteristics                                   | Symbol                | Test Conditions                                                                                                                                                                | Min.  | Тур.  | Max. | Unit <sup>1,2</sup> |

|---------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|------|---------------------|

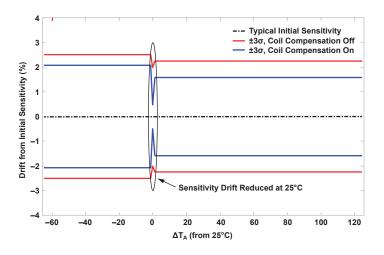

| Lifetime Sensitivity Drift                        | ΔSENS <sub>LIFE</sub> | Variation on final programmed Sensitivity value; T <sub>A</sub> = 25°C coilcomp_dis = 0; shift after AEC-Q100 grade 0 qualification testing; measured at T <sub>A</sub> = 25°C | -     | <±1.5 | -    | %                   |

|                                                   |                       | Variation on final programmed Sensitivity value; T <sub>A</sub> = 25°C coilcomp_dis = 1; shift after AEC-Q100 grade 0 qualification testing; measured at T <sub>A</sub> = 25°C | -     | <±2.5 | -    | %                   |

| Sensitivity Drift Due To Package<br>Hysteresis    | ΔSENS <sub>PKG</sub>  | Variation on final programmed Sensitivity value; measured at $T_A$ = 25°C after temperature cycling from 25°C, coilcomp_dis = 0                                                | -     | <±0.5 | -    | %                   |

|                                                   |                       | Variation on final programmed Sensitivity value; measured at $T_A$ = 25°C after temperature cycling from 25°C, coilcomp_dis = 1                                                | -     | <±2.0 | -    | %                   |

|                                                   |                       | 25°C ≤ T <sub>A</sub> ≤ 150°C, coil compensation on                                                                                                                            | -1.5  | _     | 1.5  | %                   |

| Considiuity Drift Over Temperature [1]            | ACENIC                | -40°C ≤ T <sub>A</sub> ≤ 25°C, coil compensation on                                                                                                                            | -2    | _     | 2    | %                   |

| Sensitivity Drift Over Temperature <sup>[1]</sup> | ΔSENS                 | 25°C ≤ T <sub>A</sub> ≤ 150°C, coil compensation off                                                                                                                           | -1    |       | 1    | %                   |

|                                                   |                       | -40°C ≤ T <sub>A</sub> ≤ 25°C, coil compensation off                                                                                                                           | -1.5  | _     | 1.5  | %                   |

| Quiescent Output Drift <sup>[2]</sup>             | ΔQO                   | SENS = SENS <sub>INIT</sub>                                                                                                                                                    | -1.32 | _     | 1.32 | G                   |

<sup>[1]</sup> Does not include drift over lifetime and package hysteresis.

<sup>[2]</sup> Quiescent Output Drift scales with Sensitivity.

Figure 2: Typical Initial Sensitivity Drift Due To Temperature and Package Hysteresis

#### **PROGRAMMABLE CHARACTERISTICS**: Valid at $T_A = 25$ °C and $V_{CC} = 5$ V, unless otherwise specified

| Characteristics                              | Symbol                          | Test Conditions               | Min.   | Тур. | Max.  | Unit [1] |

|----------------------------------------------|---------------------------------|-------------------------------|--------|------|-------|----------|

| SENSITIVITY                                  |                                 |                               |        |      |       |          |

| Output Sensitivity Trim Range [2]            | SENS                            |                               | 0.5    | -    | 48    | _        |

| Bits Sensitivity Trim, Coarse                | Bit<br>(SENSM_C)                |                               | _      | 3    | _     | bit      |

| Sensitivity Coarse Trim Range <sup>[3]</sup> | SENSM_C                         |                               | 1      | _    | 32    | _        |

| Bits Sensitivity Trim, Fine                  | Bit<br>(SENS_C)                 |                               | -      | 11   | _     | bit      |

| Sensitivity Fine Trim Range <sup>[4]</sup>   | SENS_C                          |                               | 0.5    | _    | 1.5   | _        |

| Bits Sensitivity Polarity                    | Bit<br>(POL)                    |                               | _      | 1    | _     | bit      |

| OFFSET (QUIESCENT OUTPUT)                    |                                 |                               |        |      |       |          |

| Bits Quiescent Output Trim, Fine             | Bit<br>(QO_C)                   |                               | -      | 16   | _     | bit      |

| Customer Quiescent Output Fine Trim Range    | QO_C                            |                               | -32768 | -    | 32767 | LSB      |

| CLAMPS (HIGH AND LOW OUTPUT                  | CLAMPS)                         |                               |        |      |       |          |

| Bits Output Low Clamp                        | Bit (OUT <sub>CLP(LOW)</sub> )  |                               | _      | 12   | _     | bit      |

| Output Low Clamp Range                       | OUT <sub>CLP(LOW)</sub>         |                               | 0      | -    | 4095  | LSB      |

| Bits Output High Clamp                       | Bit (OUT <sub>CLP(HIGH)</sub> ) |                               | _      | 12   | _     | bit      |

| Output High Clamp Range                      | OUT <sub>CLP(HIGH)</sub>        |                               | 0      | _    | 4095  | LSB      |

| TEMPERATURE COMPENSATION                     |                                 |                               |        |      |       |          |

| Bits 1st Order Sensitivity TC                | Bit<br>(SENSTC1)                | senstc1_hot_c, senstc1_cld_c  | -      | 11   | _     | bit      |

| 1st Order Sensitivity TC Range               | SENSTC1                         | 25°C < T <sub>A</sub> ≤ 150°C | -0.391 | _    | 0.391 | % / °C   |

| 1- Order densitivity to realige              | SENSICI                         | -40°C ≤ T <sub>A</sub> < 25°C | -0.781 | _    | 0.781 | %/°C     |

| Bits 2 <sup>nd</sup> Order Sensitivity TC    | Bit<br>(SENSTC2)                | senstc2_hot_c, senstc2_cld_c  | _      | 10   | _     | bit      |

| 2 <sup>nd</sup> Order Sensitivity TC Range   | SENSTC2                         | 25°C < T <sub>A</sub> ≤ 150°C | -1.5   | _    | 1.5   | m% / °C2 |

| 2 Order Sensitivity TO Nange                 | JENG102                         | -40°C ≤ T <sub>A</sub> < 25°C | -6     | _    | 6     | m% / °C2 |

| Bits 1st Order Offset TC                     | Bit<br>(QOTC)                   | qotc_hot_c, qotc_cld_c        | _      | 12   | _     | bit      |

| 1st Order Offset TC Range                    | QOTC                            | 25°C < T <sub>A</sub> ≤ 150°C | -32    | _    | 31.98 | LSB / °C |

| 1 Order Offset 10 Ivalige                    | QUIC                            | -40°C ≤ T <sub>A</sub> < 25°C | -64    | -    | 63.97 | LSB / °C |

Continued on the next page...

### A1342

# Programmable Linear Hall IC with Advanced Diagnostics for Safety-Critical Applications

#### PROGRAMMABLE CHARACTERISTICS (continued): Valid at T<sub>A</sub> = 25°C and V<sub>CC</sub> = 5 V, unless otherwise specified

| Characteristics                              | Symbol                         | Test Conditions | Min.  | Тур. | Max. | Unit [1]   |

|----------------------------------------------|--------------------------------|-----------------|-------|------|------|------------|

| LINEARIZATION                                |                                |                 |       | `    |      |            |

| Linearization Positions                      |                                |                 | _     | 17   | _    | data point |

| Bits Linearization Coefficients              | Bits<br>(LIN <sub>COEF</sub> ) |                 | _     | 12   | _    | bit        |

| Bits Post Linearization Sensitivity Trim     | Bits<br>(PLIN_SENS)            |                 | _     | 12   | _    | bit        |

| Post Linearization Sensitivity Trim<br>Range | PLIN_SENS<br>(RANGE)           |                 | _     | ±1   | _    | _          |

| Bits Post Linearization Offset Trim          | Bits<br>(PLIN_QVO)             |                 | _     | 12   | _    | bit        |

| Post Linearization Offset Trim Range         | PLIN_QVO<br>(RANGE)            |                 | -2048 | _    | 2047 | LSB        |

| Bit Linearization Output Polarity            | Bits<br>(POL <sub>OUT</sub> )  |                 | _     | 1    | _    | bit        |

| Bit Linearization Input Polarity             | Bits<br>(POL <sub>IN</sub> )   |                 | _     | 1    | _    | bit        |

<sup>[1] 1</sup> G (gauss) = 0.1 mT (millitesla).

<sup>[2]</sup> The Initial Sensitivity is adjustable by the Sensitivity Trim Coarse and Fine parameters. When reducing the initial Sensitivity check the input field is within the range specified by B<sub>IN</sub>.

<sup>[3]</sup> Sensitivity Coarse Trim is a multiplier to the initial Sensitivity with step sizes defined by the sensm parameter. Refer to the Programmable Parameter Reference section for more information.

<sup>[4]</sup> Sensitivity Fine Trim is a multiplier applied to the initial Sensitivity after the Sensitivity Coarse Trim with step sizes defined by the sens\_c parameter. Refer to the Programmable Parameter Reference section for more information.

#### **APPLICATION INFORMATION**

#### Signal Path

The A1342 contains a Hall-effect transducer that produces a signal proportional to the magnetic flux density perpendicular to the face of the package, referred as the applied magnetic flux density. The output of the Hall transducer is then amplified and digitized. The resulting signal is a signed digital value that can be scaled, offset, and compensated to achieve a desired output. The advanced digital parameters allow for a large range of input signals to be adjusted for the application. This results in the A1342 being highly flexible and accurate for applications with challenging sensing requirements. The following sections give an overview of digital signal path blocks and the corresponding transfer functions.

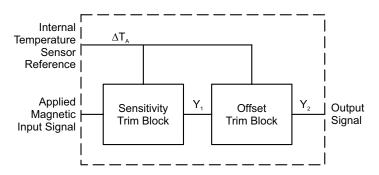

#### **COMPENSATION BLOCK**

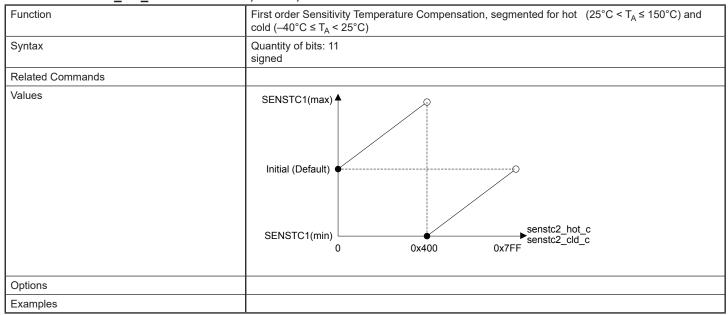

The compensation block contains adjustments to the Sensitivity and Offset. This includes compensation for input signal changes over the operating temperature range. First, the Sensitivity Trim Block multiplies the signal by a temperature-dependant gain (or attenuation) factor. The correction is segmented into two regions: hot and cold, where hot indicates ambient temperatures greater or equal to 25 °C, and cold indicates ambient temperatures lesser or equal to 25 °C. Each segmented region also contains 1st and 2nd order Sensitivity temperature compensation.

#### Note:

### The hot Sensitivity temperature compensation is independent of the cold region.

Equations 1 and 2 show the transfer function of the Sensitivity Trim Block.

$$Y_{1} = B_{IN} \cdot SENS_{INIT} \cdot POL_{C} \cdot SENSM_{C} \cdot SENS_{C} \cdot$$

$$I + \left( \left( \frac{SENSTC2\_HOT\_C}{1000} \right) \cdot \Delta T_{A} + SENSTC1\_HOT\_C \right) \cdot \frac{\Delta T_{A}}{100} I$$

(1)

$$Y_{I} = B_{IN} \cdot SENS_{INIT} \cdot POL_{C} \cdot SENSM_{C} \cdot SENS_{C} \cdot$$

$$I + \left( \left( \frac{SENSTC2\_CLD\_C}{1000} \right) \cdot \Delta T_{A} + SENSTCI\_CLD\_C \right) \cdot \frac{\Delta T_{A}}{1000}$$

(2)

#### NOTE:

Included in the transfer function shown in Equations 1 and 2 is the conversion from the applied magnetic input to a digital value,  $B_{IN} \times SENS_{INIT}$ .

The output of the Sensitivity Trim Block, Y<sub>1</sub>, is a 17-bit signed integer.

The Offset Trim Block adds a temperature-dependent factor to the input signal. The offset factor is segmented into two region: hot and cold, as defined in the Sensitivity Trim Block. Each segment contains 1st order Offset temperature compensation. Equations 3 and 4 show the transfer functions of the Offset Trim Block. The output, Y<sub>2</sub>, is a 13-bit signed integer and is the value passed out of the Compensation Block.

$$Y_2 = Y_1 + QO C + QOTC HOT C \times \Delta T_4$$

(3)

$$Y_2 = Y_1 + QO C + QOTC CLD C \times \Delta T_4$$

(4)

Figure 3: Compensation Block

**Table 1: Compensation Block Parameters**

| Variable             | Description                                                                                                                              | Programmable Parameter<br>(Memory Location)    | Units              |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------|

| POL_C                | Determines the sensitivity polarity. The default polarity is increasing with output with increasing applied south magnetic flux density. | pol_c (Register sens_trim_c 0x3 [15])          | NA                 |

| SENSM_C              | Coarse Sensitivity multiplier                                                                                                            | sensm_c (Register sens_trim_c 0x3 [14:12])     | NA                 |

| SENS_C               | Fine Sensitivity multiplier                                                                                                              | sens_c (Register sens_trim_c 0x3 [10:0])       | NA                 |

| SENSTC2_HOT_C        | 2 <sup>nd</sup> order Sensitivity temperature compensation for T <sub>A</sub> ≥ 25°C                                                     | senstc2_hot_c (Register senstc2_c 0x5 [9:0])   | m%/°C2             |

| SENSTC1_HOT_C        | 1 <sup>st</sup> order Sensitivity temperature compensation for T <sub>A</sub> ≥ 25°C                                                     | senstc1_hot_c (Register senstc1_c 0x4 [10:0])  | %/°C               |

| SENSTC2_CLD_C        | 2 <sup>nd</sup> order Sensitivity temperature compensation for T <sub>A</sub> ≤ 25°C                                                     | senstc2_cld_c (Register senstc2_c 0x5 [21:12]) | m%/°C <sup>2</sup> |

| SENSTC1_CLD_C        | 1 <sup>st</sup> order Sensitivity temperature compensation for T <sub>A</sub> ≤ 25°C                                                     | senstc1_cld_c (Register senstc1_c 0x4 [22:12]) | %/°C               |

| ΔT <sub>A</sub>      | Change in ambient temperature, equal the ambient temperature, T <sub>A</sub> , minus 25°C.                                               | NA                                             | °C                 |

| QO_C                 | Fine quiescent output adjustment                                                                                                         | qo_c (Register qo_trim_c 0x6 [15:0])           | LSB                |

| QOTC_HOT_C           | 1 <sup>st</sup> order quiescent output temperature drift compensation.                                                                   | qotc_hot_c (Register qotc_c 0x7 [11:0])        | LSB/°C             |

| QOTC_CLD_C           | 1 <sup>st</sup> order quiescent output temperature drift compensation.                                                                   | qotc_cld_c (Register qotc_c 0x7 [23:12])       | LSB/°C             |

| SENS <sub>INIT</sub> | Initial Sensitivity                                                                                                                      | NA                                             | LSB/G              |

| B <sub>IN</sub>      | Applied magnetic flux density                                                                                                            | NA                                             | G                  |

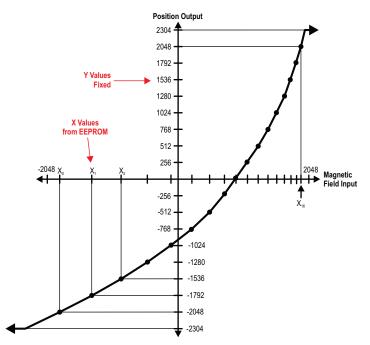

#### **LINEARIZATION**

The Linearization block passes the output from the compensation block through a piecewise-linear transfer described by 17 points, which define 16 line segments. The x-coordinates of these points are programmable and are stored as 12-bit words in a table in memory, LIN\_C. Corresponding y-coordinates are fixed and are equally spaced over the output range. For proper operation, table increasing entries, i.e.,  $x_0 \le x_1 \le x_2 \le ... \le x_{16}$  should be satisfied. If not satisfied, the output is undefined. Adjacent table entries can be equal. The linearization algorithm will not produce output values in between the y-coordinates that correspond to identical adjacent table entries; these output values are skipped. Thus jumps in the transfer function can be realized. Additionally, two more segments are implemented above and below the normal 12-bit output range to facilitate use of all 16 linearization segments without output clipping. Output points in these two segments

ments are linearly extrapolated from the two points nearest each end of the linearization table.

The linearization algorithm incorporates two modes, linearization mode (Lin Mode) and binning mode (Bin Mode).

#### **Linearization Mode (Lin Mode)**

Figure 4 shows an example transfer function which is monotonically increasing. Adjacent points form line segments; input values between are linearly interpolated to find intermediate values. Input values smaller than the first table entry are extrapolated using the points  $(x_0,-2048)$  and  $(x_1,-1792)$ , down to a minimum output value of -2304. Input values larger than the last table entry are extrapolated using the points  $(x_{15},+1792)$  and  $(x_{16},+2048)$ , up to a maximum output value of +2304. The output of the Linearization Algorithm Block,  $Y_3$ , is a 13-bit signed integer.

Figure 4: Monotonically Increasing Linearization

Transfer Function

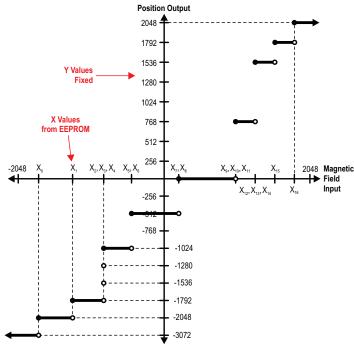

#### **Linearization Binning Mode (Bin Mode)**

When the bin\_mode\_c parameter, address lin8\_c 0x12 [13], is set, the linearization algorithm does not interpolate between points, but instead produces the output corresponding to the nearest linearization table entry less than or equal to the input value. This transfer function is useful for applications that require distinguishing between several different input ranges. For example, see Figure 5, because  $x_2 = x_3 = x_4$  and corresponding output points are -1536, -1280 and -1024 respectively, input values just below  $x_2 = x_3 = x_4$  produce an output of -1792 (output corresponding to  $x_1$ ) and inputs just above or equal to  $x_2 = x_3 = x_4$  produce an

output of -1024. Intermediate values are skipped. Thus the linearization table functions like a series of comparators with 12-bit programmable thresholds.

#### Note:

The input values below the lowest table entry produce an output value of -3072, while input values above the highest table entry produce an output value of +2048.

Figure 5: Bin Mode Transfer Function Containing Jumps (Identical Adjacent Table Entries)

The Linearization coefficients and corresponding parameters are stored in following memory locations.

**Table 2: Linearization Algorithm Block Parameters**

| Coefficient/Parameter                                              | Description                                            | Memory Location  | Units |

|--------------------------------------------------------------------|--------------------------------------------------------|------------------|-------|

| x <sub>0</sub> , x <sub>2</sub> ,x <sub>14</sub> , x <sub>16</sub> | Even Linearization Coefficients                        | lin0_c lin8_c    | LSB   |

| x <sub>1</sub> , x <sub>3</sub> ,x <sub>13</sub> , x <sub>15</sub> | Odd Linearization Coefficients                         | lin0_c lin7_c    | LSB   |

| lint_e                                                             | Set to logic 1 to enable the Linearization table.      | lin8_c 0x12 [12] | NA    |

| lint_bin_e                                                         | Set to logic 1 to enable linearization binning mode.   | lin8_c 0x12 [13] | NA    |

| lint_out_inv                                                       | Set to logic 1 to Invert output of linearization block | lin8_c 0x12 [14] | NA    |

| lint_in_inv                                                        | Set to logic 1 to Invert input of linearization block  | lin8_c 0x12 [15] | NA    |

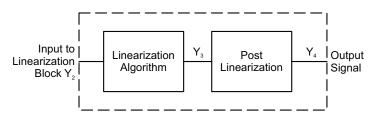

#### **POST-LINEARIZATION TRIM**

An additional gain and offset trim stage is available in the linearization block. This can be used to attenuate and gain the signal to maintain usage of all 17 linearization points when using an output range that is not full-scale. Equation 5 shows the transfer function for the Post Linearization. The output of the Post Linearization Block,  $Y_4$ , is a 12-bit signed integer and is the output of the Linearization Block.

Figure 6: Linearization Block

$$Y_4 = Y_3 \times (1 + PLIN SENS) + PLIN QVO$$

(5)

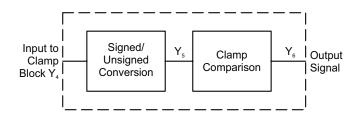

#### **CLAMP**

The clamp block limits the output to a programmable range set by the parameters clamph and clampl, register clamp\_c 0x8. Clamps are programmable throughout the full output range. If the input to the clamp block is greater than the value set by clamph the output is limited to the upper clamp value. Similarly, if the input to the clamp block is less than the value set by clampl the output is limited to the lower clamp value. If the lower clamp exceeds the upper clamp the output is undefined.

#### Note:

The input to the clamp block is a 12 bit signed value (-2048 to +2047) and is changed to a 12 bit unsigned value (0 to 4095) before comparing to the upper and lower clamp values.

Equations 6 and 7 show the transfer functions for the clamp block. The output of the Clamp Comparison is a 12-bit unsigned integer and is passed to the output block at a fixed frequency of 16 kHz.

Figure 7: Clamp Block

$$Y_5 = Y_4 + 2048$$

(conversion from signed to unsigned) (6)

if

$$(Y_5 > OUT_{CLP(HIGH)})$$

, then  $Y_6 = OUT_{CLP(HIGH)}$

else if  $(Y_5 < OUT_{CLP(LOW)})$ ,  $Y_6 = OUT_{CLP(LOW)}$

else  $Y_6 = Y_5$  (7)

**Table 3: Post-Linearization Trim Memory Parameters**

| Variable  | Step<br>Size | Min.  | Max.  | Description                                        | Parameter (Memory Location)         | Units |

|-----------|--------------|-------|-------|----------------------------------------------------|-------------------------------------|-------|

| PLIN_SENS | 2-11         | -1    | +1    | Customer post-linearization sensitivity adjustment | plin_sens, (post_lin_c 0x13 [11:0]) | NA    |

| PLIN_QVO  | 1            | -2048 | +2047 | Customer post-linearization offset adjustment      | plin_qvo, (post_lin_c 0x13 [23:12]) | LSB   |

**Table 4: Clamp Block Parameters**

| Variable | Description                      | Programmable Parameter (Memory Location) |     |  |  |  |  |

|----------|----------------------------------|------------------------------------------|-----|--|--|--|--|

| CLAMPH   | Determines the upper clamp value | clamph (Register clamp_c 0x8 [11:0])     | LSB |  |  |  |  |

| CLAMPL   | Determines the lower clamp value | clampl (Register clamp_c 0x8 [23:12])    | LSB |  |  |  |  |

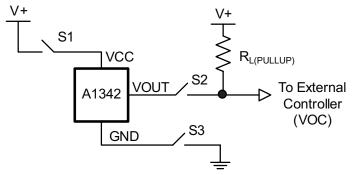

### Diagnostic Conditions DIAGNOSTIC MODES

The A1342 contains features specifically designed to reduce nondetectable fault conditions and improve system-level ASIL (Automotive Safety Integrity Level) performance. The diagnostic features provide ability to diagnose errors of the main signal path, including the analog signal path (Hall sensor and amplifiers), the ADC, and the digital processing. The A1342 also contains features to diagnose broken wire or open circuit conditions. A description of the broken wire fault conditions are listed in Table 5.

#### **DIAGNOSTIC CONFIGURATION**

The A1342 contains EEPROM parameters to configure the diagnostic modes and output behavior. The EEPROM register, cfg\_c, contains configurable parameters to enable or disable the Overvoltage Detection, Undervoltage Detection, BIST Error, Signal Out of Range, and Analog Signal Path Error (CoilBIST). In addition the output behavior in response to the error conditions is configurable. By default the device outputs a diagnostic error signal that is decoded by either the PWM or SENT message. Alternatively, the output behavior in response to the error conditions can be set to a high-impedance state (see Table 7).

Figure 8: Diagnostic Application Circuit

#### ANALOG SIGNAL PATH

Errors in the analog signal path are diagnosed using an integrated active coil compensation circuit, CoilBIST. When enabled (coil\_freq < 3), an active coil provides a known diagnostic input magnetic field to the Hall sensor circuit. The diagnostic input runs passively during normal operation and does not interfere with the response to external magnetic input. The analog signal path is time-shared between the diagnostic input and the external input at a rate of approximately 128 kHz. The CoilBIST signal detection circuit monitors the signal path at rate of approximately 8 kHz by comparing the diagnostic signal to an internal reference. In the event the analog signal path deviates by more than 10%,  $V_{\rm OUT}$  is forced to a state defined by the EEPROM register cfg\_c. Setting the parameter coilbist\_dis = 1 prevents the analog signal path monitoring from reporting detected errors on the output.

The active coil also provides compensation to reduce Sensitivity drift from lifetime and package stress influences. This feature results in a highly stable Sensitivity over multiple temperature excursions. A programmable bit, coilcomp\_dis, is available to disable the compensation while retaining the diagnostic features.

The active coil compensation feature requires an increase of the supply current,  $I_{CC}$ , to generate the internal diagnostic magnetic input. The coil compensation on-time is fixed at approximately 16 ms, while the off-time is determined by the EEPROM parameter coil\_freq. When the coil compensation is on, the supply current increases by approximately 4 mA. See Table 6 for available coil compensation off time settings. Note, setting coil\_freq to a value of 1 or 2 may increase Noise. Setting coil\_freq to a value of 3 disables the active coil compensation and diagnostic features during normal operation, while this may reduce noise.

| Description   | Circuit  | S1     | S2     | S3     | VOUT           | VOC |

|---------------|----------|--------|--------|--------|----------------|-----|

| Broken VCC    | Figure 8 | OPEN   | CLOSED | CLOSED | High Impedance | VCC |

| Broken VOUT   | Figure 8 | CLOSED | OPEN   | CLOSED | Low Impedance  | VCC |

| Broken Ground | Figure 8 | CLOSED | CLOSED | OPEN   | High Impedance | VCC |

NOTE: For proper diagnostic detection the device output clamps should be programmed to appropriate levels. Typical levels are 10% FSO for clamp low and 90% FSO for clamp high.

Table 6: Coil Compensation On/Off Time

| coil_freq <sup>[1]</sup><br>(0x09 bits 14:13) | Typical Coil<br>Compensation<br>On-Time (ms) | Typical Coil<br>Compensation<br>Off-Time (ms) | Typical Average I <sub>CC</sub><br>Increase Due to Coil<br>Compensation (mA) | CoilBIST Response<br>Time (ms) |

|-----------------------------------------------|----------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------|--------------------------------|

| 0                                             | 16                                           | 0                                             | 4                                                                            | 10                             |

| 1                                             | 16                                           | 16                                            | 2                                                                            | 26                             |

| 2                                             | 16                                           | 4080                                          | 0.015625                                                                     | 4090                           |

| 3                                             | 0                                            | 16                                            | NA                                                                           | After BIST Request             |

<sup>[1]</sup> Setting coil freq = 1 or 2 may increase noise. Setting coil freq = 3 may decrease noise but increase Lifetime Sensitivity Drift.

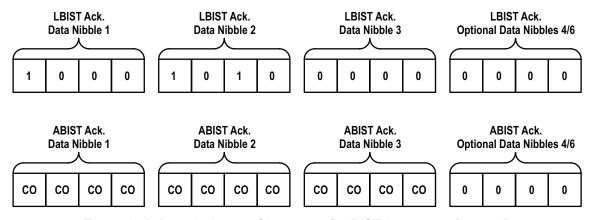

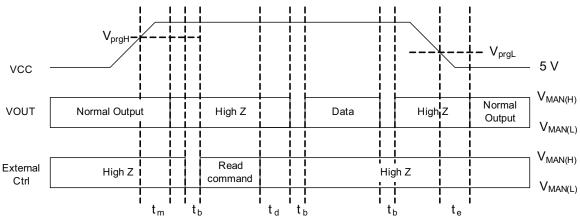

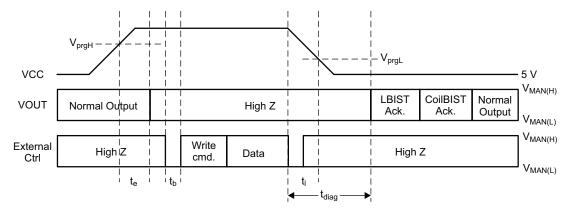

#### **BIST**

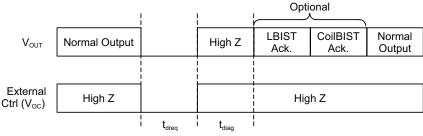

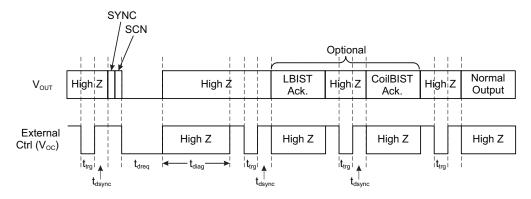

The A1342 also has a BIST (Built-In Self Test) feature to check for logic errors in the digital processing circuitry. The BIST feature is configurable with options to disable or enable on request. The options are configured by customer-programmable EEPROM bits in the cfg c register. When set for enable on request, the BIST runs in response to a request by an external controller. Diagnostic request will be different based on the output protocol. When the output protocol is PWM or SENT, the controller must hold the output low for two consecutive messages to trigger a BIST. In the case when output protocol is TSENT, to request the device perform a BIST, the external controller must hold the output low for a period of time, t<sub>drea</sub>, during the Data Nibbles of the output after the SCN nibble (see Table 8, Figure 11, and Figure 15), and then release the output to a highimpedance state. For SSENT and ASENT, the F DIAG function pulse should be used to trigger a BIST request.

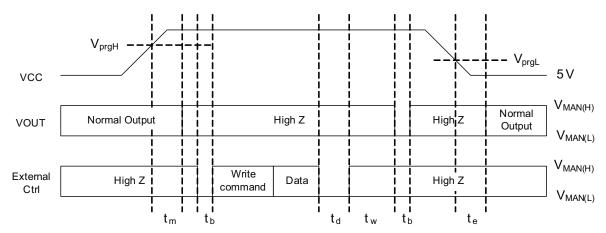

Alternatively, the BIST can execute in response to a write command from the serial communication interface. To request the device perform a BIST using the serial communication interface, a write command is used to set parameter lbist run = 1 in register

lbist\_crtl\_c (see Figure 28). The LBIST test takes approximately 10 ms to complete.

After the BIST request is received, the Output remains in a highimpedance state while the internal BIST executes. If the parameter lbist ack is set, the first output message contains a BIST signature value (LBIST Ack) indicating whether or not an error is detected during the digital logic test. If the parameter coilbist ack is set, the first output message contains the coil diagnostic value (ABIST Ack) from the CoilBIST. If both lbist ack and coilbist ack are set, the first output message is the LBIST Ack followed by the second output message ABIST Ack. The ABIST Ack message is only valid when coil freq = 3. For more information on CoilBIST when using coil freq < 3, see Diagnostic Conditions: Analog Signal Path. If there are no errors detected, the next output message after the acknowledge messages contains the normal output response. Alternatively, the LBIST Ack and ABIST Ack are returned in register lbist ctrl c. Should an error be detected, the output remains in a high-impedance state after the acknowledge messages are transmitted. See Table 7, Diagnostic Summary Table, for more information on the output in response to a diagnosed error.

Figure 9: Acknowledgment Signatures for BIST (no errors detected)

(CO = Calibrated Output, valid when coil\_freq = 3)

#### SIGNAL OUT OF RANGE

Included in the A1342 is a diagnostic feature, Signal Out of Range, to detect erroneous clamping of digital signal path as a result of external magnetic input signals. This feature also checks that the magnetic input does not exceed internal ADC range. The output responds to a Signal Out of Range diagnostic according to the settings in the EEPROM register, cfg c and Table 7.

#### **UNDERVOLTAGE DETECTION AND RESET**

The A1342 contains circuitry to detect a condition when the supply voltage drops below the specified limit. Hysteresis is designed into the circuit to prevent chattering around the threshold. This hysteresis is defined by  $V_{\rm CC(UV)HIGH}-V_{\rm CC(UV)LOW}.$  As an example, initially  $V_{\rm CC}$  and  $V_{\rm OUT}$  are within the normal operating range. If  $V_{\rm CC}$  drops below  $V_{\rm CC(UV)LOW},$  VOUT is forced to a state defined by the EEPROM register, efg\_c. When  $V_{\rm CC}$  returns above  $V_{\rm CC(UV)HIGH},$  VOUT returns to its normal operating state. If  $V_{\rm CC}$  drops below the internal reset level,  $V_{\rm CC(POR)LOW},$  the output is forced to a high-impedance state. When  $V_{\rm CC}$  returns above the rising reset level,  $V_{\rm CC(POR)HIGH},$  the output responds according to the undervoltage detection. The output will not respond with normal data until a delay of  $t_{\rm PO}$  after a reset event.

#### **OVERVOLTAGE DETECTION**

The A1342 contains circuitry to detect a condition when the supply voltage rises above the specified limit. Hysteresis is designed into the circuit to prevent chattering around the threshold. This hysteresis is defined by  $V_{CC(OV)HIGH} - V_{CC(OV)LOW}.$  As an example, initially  $V_{CC}$  and  $V_{OUT}$  are within the normal operating range. If  $V_{CC}$  rises above  $V_{CC(OV)HIGH},\,V_{OUT}$  is forced to a state defined by the EEPROM register, cfg\_c. When  $V_{CC}$  returns below  $V_{CC(OV)LOW}$ ,  $V_{OUT}$  returns to its normal operating state.

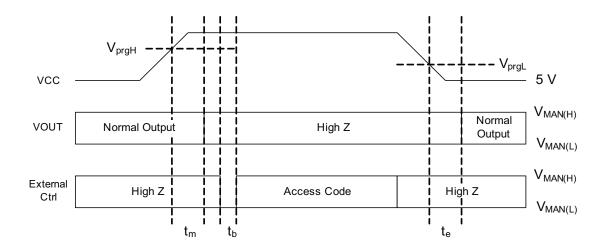

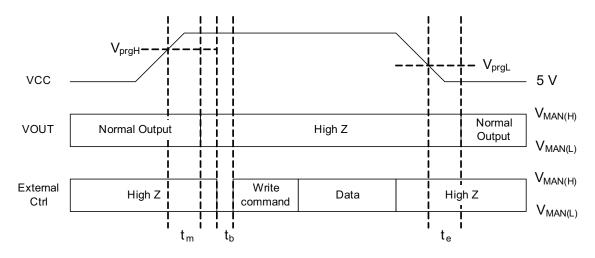

The overvoltage detection is only enabled when the EEPROM lock bit is set. If the EEPROM lock bit is not set, and  $V_{CC}$  increases above  $V_{CC(OV)HIGH},\;$  the device will enter programming mode and the output is forced to a high-impedance state. If  $V_{CC}$  rises above the high-voltage threshold,  $V_{CC(HV)HIGH},\;$  the output is forced to a high-impedance state.

#### **OVERTEMPERATURE DETECTION**

The A1342 contains circuitry to detect a condition when the ambient temperature is greater than 160°C, which is outside of the operating range of the part. This will cause the output to respond according to the settings in the EEPROM register, cfg\_c and Table 7.

#### **BROKEN GROUND DETECTION**

The A1342 contains circuitry to detect a condition when the ground connection is disconnected. When the ground connection is severed, the digital output driver turns off, forcing the output to a high-impedance state.

#### **EEPROM DIAGNOSTICS**

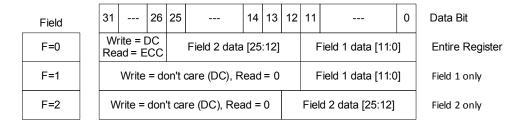

The A1342 contains EEPROM with error checking and correction, ECC. The ECC corrects for a single EEPROM bit error without effecting device performance. The ECC also detects a dual bit EEPROM error and triggers an internal fault signal and forces the output to a high-impedance state. Upon a read of EEPROM with no errors, bits 0 through 25 will return the requested EEPROM contents and bits 26 through 31, the six MSBs of the EEPROM register, will return as all zeros. When a corrected single bit error is detected, bit 28 of the read response will return high, indicating the single bit error. When a dual bit error is detected, a read of EEPROM will have bit 29 set high indicating the dual bit error.

**Table 7: Diagnostic Summary Table**

| Diagnostic<br>Detection                  | Conditions                                                                                                                                        | V <sub>OUT</sub> (PWM)<br>diag_mode = 0 | V <sub>OUT</sub> (SENT)<br>diag_mode = 0 | V <sub>OUT</sub> (PWM)<br>diag_mode = 1 <sup>[1]</sup> | diag_reg_c<br>(binary) | SENT Data<br>Nibble #4<br>and #5 (sent_<br>data_cfg = 1)<br>(binary) |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------|--------------------------------------------------------|------------------------|----------------------------------------------------------------------|

| Overvoltage<br>Condition                 | Overvoltage detection is enabled,<br>diagnostic output is set for advanced<br>output flag, and device lock is set, ovd_<br>dis = 0, dev_lock = 5. | ½ carrier frequency<br>60% DC           | See SENT, SCN<br>nibble bit 1 = 1        | High impedance                                         | XXX1 XXXX              | XXXX 1XXX                                                            |

| Undervoltage<br>Condition <sup>[2]</sup> | Undervoltage detection is enabled, and diagnostic output is set for advanced output flag, uvd_dis = 0.                                            | ½ carrier frequency<br>40% DC           | See SENT, SCN<br>nibble bit 1 = 1        | High impedance                                         | XXXX 1XXX              | XXX1 XXXX                                                            |

| CoilBIST (Analog<br>Signal Path) Error   | CoilBIST enabled and diagnostic output is set for advanced output flag, coilbist_dis = 0, coil_freq < 3.                                          | ½ carrier frequency<br>30% DC           | See SENT, SCN<br>nibble bit 0 = 1        | High impedance                                         | XXXX X1XX              | XX1X XXXX                                                            |

| BIST Error                               | lbist_dis = 0                                                                                                                                     | High impedance                          | High impedance                           | High impedance                                         | XXXX XX1X              | NA (High<br>Impedance)                                               |

| Overtemperature<br>Condition             | Overtemperature detection is enabled and diagnostic output is set for advanced output flag, otmp_dis = 0.                                         | ½ carrier frequency<br>70% DC           | See SENT, SCN<br>nibble bit 1 = 1        | High impedance                                         | XX1X XXXX              | XXXX X1XX                                                            |

| Signal Out of Range,<br>Low              | Signal Out of Range detection is enabled, and diagnostic output is set for advanced output flag, oor_dis = 0.                                     | ½ carrier frequency<br>80% DC           | See SENT, SCN<br>nibble bit 1 = 1        | High impedance                                         | X1XX XXXX              | XXXX XX1X                                                            |

| Signal Out of Range,<br>High             | Signal Out of Range detection is enabled, and diagnostic output is set for advanced output flag, oor_dis = 0.                                     | ½ carrier frequency<br>90% DC           | See SENT, SCN<br>nibble bit 1 = 1        | High impedance                                         | 1XXX XXXX              | XXXX XXX1                                                            |

| EEPROM Fault (2 bit error detection)     |                                                                                                                                                   | High impedance                          | High impedance                           | High impedance                                         | XXXX XXX1              | NA (High<br>Impedance)                                               |

<sup>[1]</sup> diag\_mode = 1 is not supported when V<sub>OUT</sub> is configured for SENT protocol.

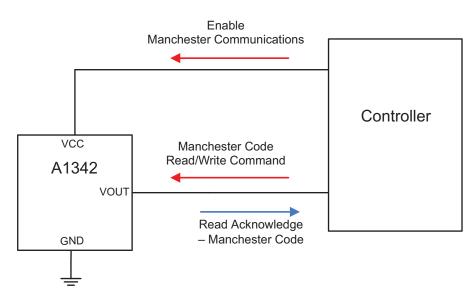

#### **Linear Output Protocols**

The A1342 operating output is a digital voltage signal that transfers information proportionally to the applied magnetic input signal. Few customer-selectable options are provided for output signal formatting: pulse-width-modulated (PWM), and variations of single-edge nibble transmission encoding scheme (SENT, SAEJ2716).

#### Note:

The device response to the applied magnetic field is on the OUT pin. However, that pin is also used to transmit and receive data in response to a serial programming commands, during which the normal output operation is suppressed. Refer to the Programming Serial Interface section for more information. The EEPROM is described in the EEPROM Structure section. The output falling edge slew rate is adjustable using the outdrv\_sel parameter. Adjusting this can improve EMC performance by reducing high-frequency

currents. This parameter can also increase the output fall time and result in longer minimum pulse durations for serial communication or SENT transmission.

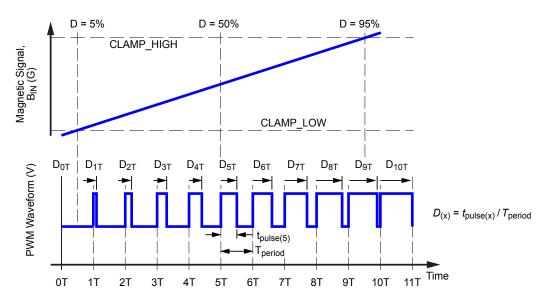

#### PWM OUTPUT MODE (outmsg\_mode = 0)

PWM involves converting the output voltage amplitude to a series of constant-frequency binary pulses, with the percentage of the of high portion of the pulse varied in direct proportion to the applied magnetic field.

The PWM output mode is configured by setting the following parameters in EEPROM:

- PWM option is EEPROM programmable (for programming parameters, see EEPROM Structure section)

- sent\_pwm\_rate sets the PWM carrier frequency based on the values in Table 14

<sup>[2]</sup> An Overvoltage Condition will cause the device to enter Programming Mode which will result in the output being in a high-impedance state when dev\_lock does not equal 5.

Figure 10: PWM Mode Duty-Cycle-Based Waveform

PWM mode outputs a duty-cycle-based waveform that can be read by the external controller as a cumulatively changing continuous voltage.

Initiation of the BIST is done through the external controller request and explained in Table 8 and Figure 11.

Table 8: External BIST Request and SENT Trigger Characteristics

| Parameter                             | Symbol                      | Description                                                                                  | Min. | Тур. | Max. | Unit              |

|---------------------------------------|-----------------------------|----------------------------------------------------------------------------------------------|------|------|------|-------------------|

| Trigger Pulse Width                   | t <sub>trg</sub>            | Trigger pulse for TSENT operation; see SSENT and ASENT sections for F_OUTPUT pulse durations | 1.8  | -    | _    | μs                |

| Synchronization Pulse Delay [1]       | t <sub>dsync</sub>          |                                                                                              | 7    | -    | 524  | tick              |

| SENT Output Trigger Signal            | V <sub>SENTtrig(L)</sub>    | V <sub>OUT</sub> falling, T <sub>A</sub> = 25°C                                              | _    | _    | 1.39 | V                 |

| SENT Output Trigger Signal            | V <sub>SENTtrig(H)</sub>    | V <sub>OUT</sub> rising, T <sub>A</sub> = 25°C                                               | 2.3  | _    | -    | V                 |

| SENT Output Trigger Signal Hysteresis | V <sub>SENTtrig(HYST)</sub> | T <sub>A</sub> = 25°C                                                                        | _    | 300  | _    | mV                |

| External BIST Request Pulse Width     | t <sub>dreq</sub>           | PWM                                                                                          | 2    | _    | _    | frame<br>rate [2] |

|                                       |                             | SENT Modes                                                                                   | 15   | _    | _    | tick              |

| BIST Delay                            | t <sub>diag</sub>           | Delay for device to execute internal BIST                                                    | 10   | -    | 20   | ms                |

<sup>[1]</sup> t<sub>dsync</sub> can increase from 7 ticks to preserve a minimum time of approximately 70 µs from the falling edge of the trigger to the start of the SCN nibble.

<sup>[3]</sup> When in Trigger SENT Output mode the external controller must pull the output low after tdsync and before the first data nibble in the SENT frame, for a time of t<sub>dreq</sub>, to initiate a BIST request.

Figure 11: External BIST Request with PWM or Synchronous SENT Output Mode

<sup>[2]</sup> The frame rate is determined by the sent\_pwm\_rate parameter.

#### SENT OUTPUT MODES

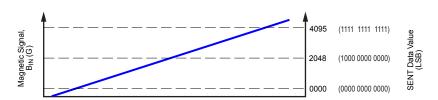

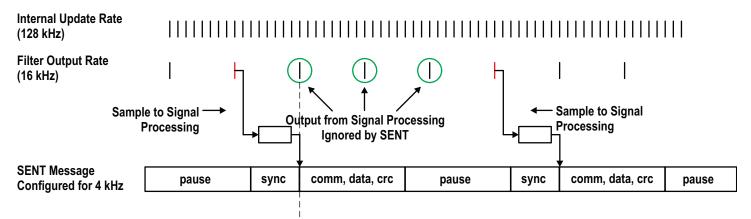

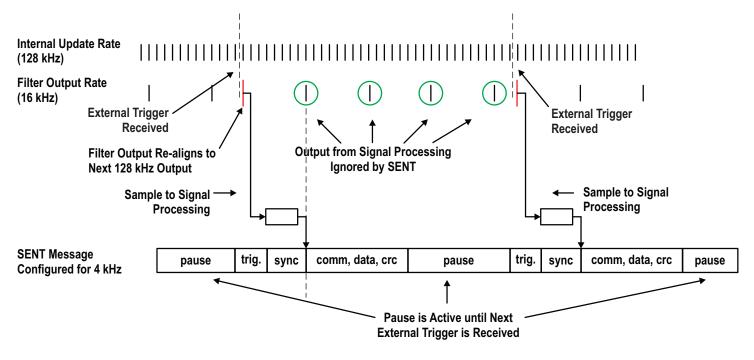

The SENT output mode converts the input magnetic signal to a binary value mapped to the Full Scale Output, FSO, range of 0 to 4095, shown in Figure 12. This data is inserted into a binary pulse message, referred to as a frame, that conforms to the SENT data transmission specification (SAEJ2716 JAN2010). Certain parameters for configuration of the SENT messages can be set in EEPROM.

The SENT output modes are selected by setting the following parameters in EEPROM:

- SAE J2716 SENT with enhancement options (outmsg\_mode = 1)

- Triggered SENT TSENT (outmsg\_mode = 2) User defines sampling and data retrieving.

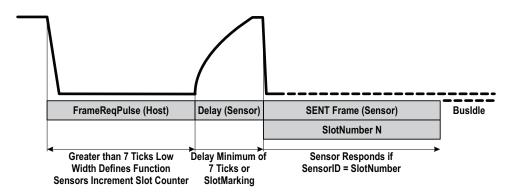

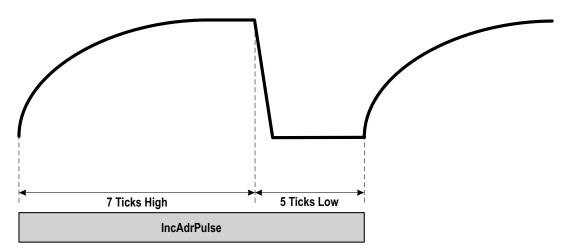

- Sequential SENT SSENT User requests data from multiple devices on the SENT line in sequential order (outmsg\_mode = 4 for short\_trigger and outmsg\_mode = 3 for long\_trigger). Short and long trigger modes can be differentiated on the length and number of host function/request pulses.

- Addressable SENT ASENT User requests data from any device on the SENT line in any order. (outmsg\_mode = 7, 6, or 5)

- Additional configuration parameters in register 0x14, out\_ cfg c.

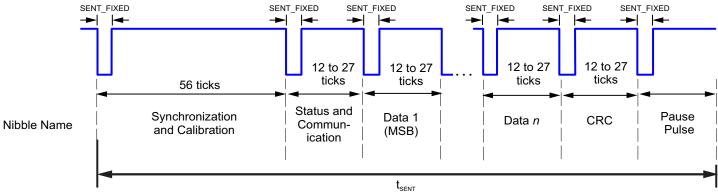

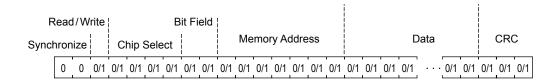

#### **MESSAGE STRUCTURE**

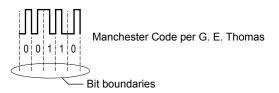

A SENT message is a series of nibbles, with the following characteristics:

- Each nibble is an ordered pair of a low-voltage interval followed by a high-voltage interval

- The low interval, SENT\_FIXED, is defined as 5 SENT ticks.

The high interval contains information and is variable in duration to indicate the data payload of the nibble.

The duration of a nibble is denominated in clock ticks. The period of a tick is set by sent\_pwm\_rate parameter as in Table 14. The duration of the nibble is the sum of the low-voltage interval plus the high-voltage interval.

The nibbles of a SENT message are arranged in the following required sequence (see Figure 13):

- Synchronization and Calibration: flags the start of the SENT message

- 2. Status and Communication: provides A1342 status and the format of the data

- 3. Data: magnetic field and optional data

- 4. CRC: error checking

- 5. Pause Pulse: sets timing relative to A1342 updates

Figure 12: SENT Mode Output

SENT mode outputs a digital value that can be read by the external controller

Figure 13: General Format for SENT Message Frame

#### **OPTIONAL SHORT SERIAL MESSAGE**

The A1342 SENT output supports an optional mode to transmit additional data. The slow serial mode, enables transmission of additional data by encoding information in the Status and Communication (SCN) nibbles. The encoded data is captured over several transmissions and is then decoded to indicate additional short serial message data. For more details on the short serial

message please refer to the SENT SAEJ2716 specification. The slow serial mode is enabled when the EEPROM parameter sent\_slow\_ser\_dis = 0. Following a reset, the first message transmitted is 0, following in order of the message ID until message 4, and then repeating. Table 10 identifies the data sent with each message ID. The CRC for the Short Serial Message is derived for the Message ID and data, and is the same checksum algorithm used for the SENT CRC.

Table 9: Short Serial Message Format in SENT Status and Communication Nibble

| SCN Bit (For the values of bits 0 and 1 please see Table 7:<br>Diagnostic Summary) |            | Nibble # |      |   |   |   |   |   |     |    |    |    |    |    |    |    |

|------------------------------------------------------------------------------------|------------|----------|------|---|---|---|---|---|-----|----|----|----|----|----|----|----|

|                                                                                    | 1          | 2        | 3    | 4 | 5 | 6 | 7 | 8 | 9   | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

| Bit 3 (Start Bit)                                                                  | 1          | 0        | 0    | 0 | 0 | 0 | 0 | 0 | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Bit 2 (Serial Data)                                                                | Message ID |          | Data |   |   |   |   |   | CRC |    |    |    |    |    |    |    |

Table 10: SENT Slow Serial Data

| Message ID | Data                                                                                                                                                                                                                                         |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0          | Error status from the parameter diag_reg_c located in register err_status_c, 0x45 bits [23:16]. {EEPROM DBE, LBIST, Coil Measurement Monitor, Undervoltage, Overvoltage, Overtemperature, Signal out of range low, Signal out of range high} |

| 1          | 8-bit temperature value from internal temperature sensor. Values are saturated to ±128°C, and 3 LSBs are rounded to nearest degree                                                                                                           |

| 2          | id_c[7:0] (Customer ID, EEPROM 0x2)                                                                                                                                                                                                          |

| 3          | id_c[15:8] (Customer ID, EEPROM 0x2)                                                                                                                                                                                                         |

| 4          | id_c[23:16] (Customer ID, EEPROM 0x2)                                                                                                                                                                                                        |

In the case of SSENT and ASENT mode, SCN bits 2 and 3 can be selected to label the address of the sensor on the shared SENT line (sen\_no\_smsg =1 and sent\_slow\_ser\_dis = 1, gives ID in SCN).

#### **DATA NIBBLE FORMAT**

The A1342 SENT output supports options for the message data nibble format. The data nibble format is determined by the EEPROM parameter sent\_data\_cfg. The options for either a minimum 3 or maximum 6 nibbles of data is defined in Table 11. Where:

• magout[11:0]: 12-bit magnetic output data.

- count[11:0]: SENT frame count. The counter increments once for every frame that is sent up to the maximum count. At the next count, after the maximum, the counter starts again at 0. The maximum count is 15 and 4095 for sent\_data\_cfg = 1 and sent data\_cfg = 2 respectively.

- temp\_out[11:0]: 12-bit signed output from the internal temperature sensor. Ambient temperature (°C) = 12-bit signed temperature value / 8 (LSB / °C) + 25.

- diag[7:0] Diagnostic flags, EEPROM, LBIST, CoilBist, Undervoltage, Overvoltage, Overtemperature, Signal out of range low, and Signal out of range high.

**Table 11: SENT Data**

| sent_data_cfg | Data Nibble #1 | Data Nibble #2 | Data Nibble #3 | Data Nibble #4  | Data Nibble #5 | Data Nibble #6 | # of Nibbles |

|---------------|----------------|----------------|----------------|-----------------|----------------|----------------|--------------|

| 0             | mag_out [11:8] | mag_out[7:4]   | mag_out[3:0]   | _               | _              | _              | 3            |

| 1             | mag_out [11:8] | mag_out[7:4]   | mag_out[3:0]   | diag[7:4]       | diag[3:0]      | count[3:0]     | 6            |

| 2             | mag_out[11:8]  | mag_out[7:4]   | mag_out[3:0]   | count[11:8]     | count[7:4]     | count[3:0]     | 6            |

| 3             | mag_out[11:8]  | mag_out[7:4]   | mag_out[3:0]   | temp_out [11:8] | temp_out [7:4] | temp_out [3:0] | 6            |

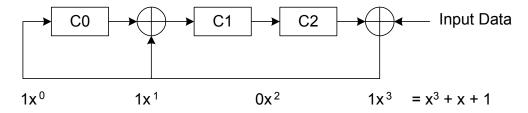

#### **CHECKSUM (CRC) NIBBLE**

The CRC consists of 4 bits derived from the data nibbles only. The CRC is calculated using the polynomial  $x^4 + x^3 + x^2 + 1$  with a seed of 4'b0101. For the shared SENT protocols, SSENT and ASENT, there is an option that SCN is included into the CRC

nibble (sen crc has scn = 1, includes SCN into CRC).

#### **OUTPUT DRIVER FALL TIME SELECTION**

User is allowed to change the fall time of the output digital signal using the EEPROM parameter outdry sel. See Table 12 below.

Table 12: Code vs C<sub>LOAD</sub> for outdrv\_sel