SNOSCX2-SEPTEMBER 2013

# LDC1000 Inductance to Digital Converter

Check for Samples: LDC1000

## FEATURES

- Magnet-Free Operation

- Sub-Micron Precision

- Adjustable Sensing Range (via Coil Design)

- Lower System Cost

- Remote Sensor Placement (Decoupling the LDC from Harsh Environments)

- High Durability (by Virtue of Contact-Less Operation)

- Insensitivity to Environmental Interference (such as Dirt, Dust, Water, Oil)

- Supply Voltage, Analog: 4.75V to 5.25V

- Supply Voltage, IO: 1.8V to 5.25V

- Supply Current (w/o LC Tank): 1.7mA

- Rp Resolution: 16-bit

- L Resolution: 24-bit

- LC Frequency Range: 5kHz to 5MHz

# **APPLICATIONS**

- Drive-by-Wire Systems

- Gear-Tooth Counting

- Flow Meters

- Push-Button Switches

- Notebook Computers

- Game Controllers

- Multi-Function Printers

- Digital Cameras

- Medical Devices

## DESCRIPTION

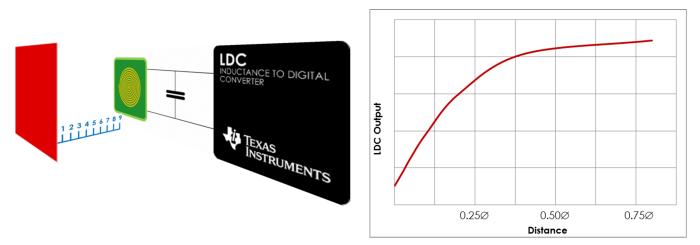

Inductive Sensing is a contact-less, short-range sensing technology that enables low-cost, highresolution sensing of conductive targets in the presence of dust, dirt, oil, and moisture, making it extremely reliable in hostile environments. Using a coil which can be created on a PCB as a sensing element, the LDC1000 enables ultra-low cost system solutions.

Inductive sensing technology enables precise measurement of linear/angular position, displacement, motion, compression, vibration, metal composition, and many other applications in markets including automotive, consumer, computer, industrial, medical, and communications. Inductive sensing offers better performance and reliability at lower cost than other, competitive solutions.

The LDC1000 is the world's first inductance-to-digital converter, offering the benefits of inductive sensing in a low-power, small-footprint solution. The product is available in a SON-16 package and offers several modes of operation. An SPI interface simplifies connection to an MCU.

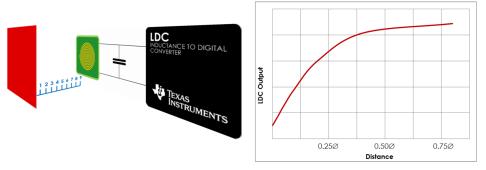

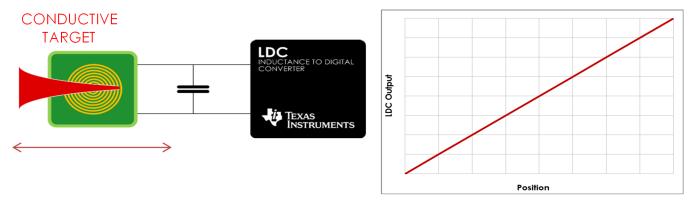

## TYPICAL APPLICATION

Figure 1. Axial Distance Sensing

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# LDC1000

Alla S

#### SNOSCX2-SEPTEMBER 2013

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

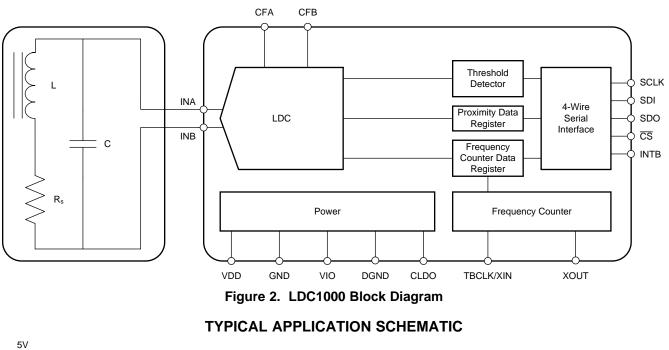

**BLOCK DIAGRAM**

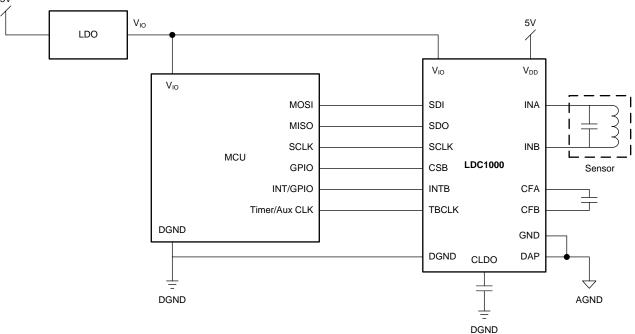

Figure 3. Typical Application Schematic

#### www.ti.com

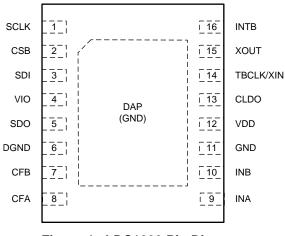

### **CONNECTION DIAGRAM**

Figure 4. LDC1000 Pin Diagram SON-16

### Table 1. Pin Description<sup>(1)</sup>

| PIN NAME  | PIN<br>NO. | PIN<br>TYPE | FUNCTION                                                                                                                                                            |

|-----------|------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK      | 1          | DO          | SPI clock input. SCLK is used to clock-out/clock-in the data from/into the chip                                                                                     |

| CSB       | 2          | DI          | SPI CSB. Multiple devices can be connected on the same SPI bus and CSB can be used to select the device to be communicated with                                     |

| SDI       | 3          | DI          | SPI Slave Data In (Master Out Slave In). This should be connected to the Master Out Slave In of the master                                                          |

| VIO       | 4          | Р           | Digital IO Supply                                                                                                                                                   |

| SDO       | 5          | DO          | SPI Slave Data Out (Master In Slave Out). It is high-z when CSB is high                                                                                             |

| DGND      | 6          | Р           | Digital ground                                                                                                                                                      |

| CFB       | 7          | А           | LDC filter capacitor                                                                                                                                                |

| CFA       | 8          | А           | LDC filter capacitor                                                                                                                                                |

| INA       | 9          | А           | External LC Tank. Connected to external LC tank                                                                                                                     |

| INB       | 10         | А           | External LC Tank. Connected to external LC tank                                                                                                                     |

| GND       | 11         | Р           | Analog ground                                                                                                                                                       |

| VDD       | 12         | Р           | Analog supply                                                                                                                                                       |

| CLDO      | 13         | А           | LDO bypass capacitor. A 56nF capacitor should be connected from this pin to GND                                                                                     |

| TBCLK/XIN | 14         | DI/A        | External time-base clock/XTAL. Either an external clock or crystal can be connected                                                                                 |

| XOUT      | 15         | A           | XTAL. Crystal out. Recommended to connect 8Mhz crystal between XIN and XOUT with 20pF cap from each pin to ground. Should be floating when external clock is used   |

| INTB      | 16         | DO          | Configurable interrupt. This pin can be configured to behave in 3 different ways by programing the INT pin mode register. Either threshold detect, wakeup, or DRDYB |

| DAP       | 17         | Р           | Connect to GND                                                                                                                                                      |

(1) DO: Digital Output, DI: Digital Input, P: Power, A: Analog

www.ti.com

## ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| ESD Tolerance <sup>(2)</sup>                 | Human Body Model    | 1kV                 |

|----------------------------------------------|---------------------|---------------------|

|                                              | Charge Device Model | 250V                |

| Analog Supply Voltage (VDD – GND)            | 6V                  |                     |

| IO Supply Voltage (VIO – GND)                | 6V                  |                     |

| Voltage on any Analog Pin                    |                     | -0.3V to VDD + 0.3V |

| Voltage on any Digital Pin                   |                     | -0.3V to VIO + 0.3V |

| Input Current on INA and INB                 |                     | 8mA                 |

| Junction Temperature, TJ <sup>(3)</sup>      |                     | +150°C              |

| Storage Temperature Range , T <sub>stg</sub> | -65°C to +150°C     |                     |

(1) Absolute Maximum Ratings are limits beyond which damage to the device may occur. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. Operating Ratings are conditions under which operation of the device is intended to be functional. For ensured specifications and test conditions, see the Electrical Characteristics. The human body model is a 100pF capacitor discharged through a  $1.5k\Omega$  resistor into each pin.

The maximum power dissipation is a function of TJ(MAX),  $\theta$ JA, and the ambient temperature, TA. The maximum allowable power dissipation at any ambient temperature is PDMAX = (TJ(MAX) - TA)/ $\theta$ JA. All numbers apply for packages soldered directly onto a PC (3) board. The package thermal impedance is calculated in accordance with JESD 51-7.

## **RECOMMENDED OPERATING CONDITIONS**<sup>(1)</sup>

|                                           |                        | MIN  | MAX  | UNIT |

|-------------------------------------------|------------------------|------|------|------|

| Analog Supply Voltage (VDD – GND)         | 4.75                   | 5.25 | V    |      |

| IO Supply Voltage (VIO – GND)             |                        |      | 5.25 | V    |

| VDD-VIO                                   | VDD-VIO                |      |      | V    |

| Operating Temperature, TA                 |                        |      | 125  | °C   |

| Package Thermal Resistance <sup>(2)</sup> | SON (θ <sub>JA</sub> ) |      | 28   | °C/W |

(1) Absolute Maximum Ratings are limits beyond which damage to the device may occur. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. Operating Ratings are conditions under which operation of the device is intended to be functional. For ensured specifications and test conditions, see the Electrical Characteristics.

The maximum power dissipation is a function of TJ(MAX), 0JA, and the ambient temperature, TA. The maximum allowable power (2) dissipation at any ambient temperature is PDMAX = (TJ(MAX) - TA)/ 0JA. All numbers apply for packages soldered directly onto a PC board. The package thermal impedance is calculated in accordance with JESD 51-7.

### ELECTRICAL CHARACTERISTICS<sup>(1)</sup>

Unless otherwise specified, all limits ensured for TA = TJ = 25°C, VDD = 5.0V, VIO =  $3.3V^{(2)}$

| SYMBOL                  | PARAMETER                        | CONDITIONS/<br>COMMENTS                                                        | MIN <sup>(3)</sup>                           | TYP <sup>(4)</sup>         | MAX <sup>(3)</sup> | UNITS                 |

|-------------------------|----------------------------------|--------------------------------------------------------------------------------|----------------------------------------------|----------------------------|--------------------|-----------------------|

| POWER                   |                                  |                                                                                |                                              |                            |                    |                       |

| V <sub>DD</sub>         | Analog Supply Voltage            |                                                                                | 4.75                                         | 5                          | 5.25               | V                     |

| V <sub>IO</sub>         | IO Supply Voltage                | VIO≤VDD                                                                        | 1.8                                          | 3.3                        | 5.25               | V                     |

| I <sub>DD</sub>         | Supply Current, VDD              | Does not include LC<br>tank current                                            |                                              | 1.7                        | 2.3                | mA                    |

| I <sub>VIO</sub>        | IO Supply Current                | Static current                                                                 |                                              |                            | 14                 | uA                    |

| I <sub>DD_LP</sub>      | Low-Power Mode<br>Supply Current | With out LC Tank                                                               |                                              | 250                        |                    | uA                    |

| t <sub>start</sub>      | Start-Up Time                    | From POR to ready-to-<br>convert. Crystal not<br>used for frequency<br>counter | convert. Crystal not<br>used for frequency 2 |                            |                    | ms                    |

| LDC                     |                                  |                                                                                |                                              |                            |                    |                       |

| f <sub>sensor_MIN</sub> | Minimum sensor<br>frequency      |                                                                                |                                              | 5                          |                    | kHz                   |

| f <sub>sensor_MAX</sub> | Maximum sensor<br>frequency      |                                                                                |                                              | 5                          |                    | MHz                   |

| A <sub>sensor_MIN</sub> | Minimum sensor<br>amplitude      |                                                                                |                                              | 1                          |                    | VPP                   |

| A <sub>sensor_MAX</sub> | Maximum sensor<br>amplitude      |                                                                                |                                              | 4                          |                    | VPP                   |

| t <sub>REC</sub>        | Recovery time                    | Oscillation start-up time<br>after RP under-range<br>condition                 |                                              | 10                         |                    | 1/f <sub>sensor</sub> |

| R <sub>p_MIN</sub>      | Minimum Sensor Rp<br>Range       |                                                                                |                                              | 798                        |                    | Ω                     |

| R <sub>p_MAX</sub>      | Maximum Sensor Rp<br>Range       |                                                                                |                                              | 3.93M                      |                    | Ω                     |

| $R_{p\_RES}$            | Rp Measurement<br>Resolution     |                                                                                |                                              | 16                         |                    | Bits                  |

| t <sub>S_MIN</sub>      | Minimum Response<br>Time         | Minimum<br>programmable settling<br>time of digital filter                     |                                              | 192×1/f <sub>sensor</sub>  |                    | S                     |

| t <sub>S_MAX</sub>      | Maximum Response<br>Time         | Maximum<br>programmable settling<br>time of digital filter                     |                                              | 6144×1/f <sub>sensor</sub> |                    | S                     |

| EXTERNAL CLO            | CK/CRYSTAL FOR FREQ              | UENCY COUNTER                                                                  |                                              |                            | · ·                |                       |

| Crystal                 | Frequency                        |                                                                                |                                              | 8                          |                    | MHz                   |

|                         | Startup time                     |                                                                                |                                              | 30                         |                    | ms                    |

| External Clock          | Frequency                        |                                                                                |                                              |                            | 8                  | MHz                   |

|                         | Clock Input High<br>Voltage      |                                                                                |                                              |                            | V <sub>IO</sub>    | V                     |

(1) Electrical Characteristics Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that TJ = TA. No specification of parametric performance is indicated in the electrical tables under conditions of internal self-heating where TJ > TA. Absolute Maximum Ratings indicate junction temperature limits beyond which the device may be permanently degraded, either mechanically or electrically.

(2) The maximum power dissipation is a function of TJ(MAX), θJA, and the ambient temperature, TA. The maximum allowable power dissipation at any ambient temperature is PDMAX = (TJ(MAX) - TA)/ θJA. All numbers apply for packages soldered directly onto a PC board. The package thermal impedance is calculated in accordance with JESD 51-7.

(3) Limits are specified by testing, design, or statistical analysis at 25°C. Limits over the operating temperature range are specified through correlations using statistical quality control (SQC) method.

(4) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not specified on shipped production material.

TEXAS INSTRUMENTS

SNOSCX2-SEPTEMBER 2013

www.ti.com

# ELECTRICAL CHARACTERISTICS<sup>(1)</sup> (continued)

Unless otherwise specified, all limits ensured for TA = TJ = 25°C, VDD = 5.0V, VIO =  $3.3V^{(2)}$

| SYMBOL            | PARAMETER                     | CONDITIONS/<br>COMMENTS | MIN <sup>(3)</sup>  | TYP <sup>(4)</sup>   | MAX <sup>(3)</sup>  | UNITS |

|-------------------|-------------------------------|-------------------------|---------------------|----------------------|---------------------|-------|

| DIGITAL I/O C     | HARACTERISTICS                |                         |                     |                      |                     |       |

| V <sub>IH</sub>   | Logic "1" Input Voltage       |                         | 0.8×V <sub>IO</sub> |                      |                     | V     |

| V <sub>IL</sub>   | Logic "0" Input Voltage       |                         |                     |                      | 0.2×V <sub>IO</sub> | V     |

| V <sub>OH</sub>   | Logic "1" Output<br>Voltage   | ISOURCE=400uA           |                     | V <sub>IO</sub> -0.3 |                     | V     |

| V <sub>OL</sub>   | Logic "0" Output<br>Voltage   | ISINK=400uA             |                     |                      | 0.3                 | V     |

| I <sub>IOHL</sub> | Digital IO Leakage<br>Current |                         | -500                |                      | 500                 | nA    |

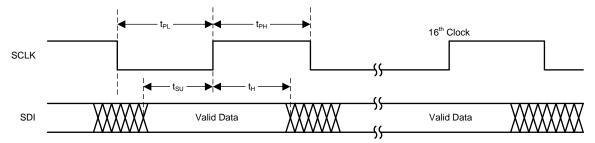

### **TIMING DIAGRAMS**

Unless otherwise noted, all limits specified at TA = 25°C, VDD=5.0, VIO=3.3, 10pF capacitive load in parallel with a 10k $\Omega$  load on SDO. Specified by design; not production tested.

Figure 5. Write Timing Diagram

|                   |                        | Table                   | <del>2</del> . |     |     |      |

|-------------------|------------------------|-------------------------|----------------|-----|-----|------|

| F                 | PARAMETER              | CONDITIONS              | MIN            | TYP | MAX | UNIT |

| F <sub>SCLK</sub> | Serial Clock Frequency |                         |                |     | 4   | MHz  |

| t <sub>PH</sub>   | SCLK Pulse Width High  | F <sub>SCLK</sub> =4Mhz | 0.4/Fsclk      |     |     | S    |

| t <sub>PL</sub>   | SCLK Pulse Width Low   | F <sub>SCLK</sub> =4Mhz | 0.4/Fsclk      |     |     | S    |

| t <sub>SU</sub>   | SDI Setup Time         |                         | 10             |     |     | ns   |

| t <sub>H</sub>    | SDI Hold Time          |                         | 10             |     |     | ns   |

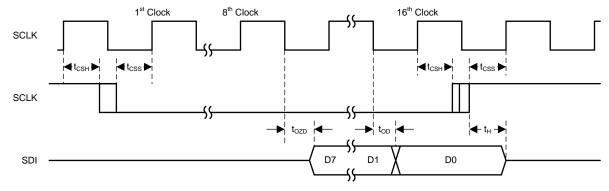

### Figure 6. Read Timing Diagram

| F                  | PARAMETER                      | CONDITIONS                                         | MIN | TYP                   | MAX | UNIT |

|--------------------|--------------------------------|----------------------------------------------------|-----|-----------------------|-----|------|

| t <sub>ODZ</sub>   | SDO Driven-to-Tristate<br>Time | Measured at 10% / 90% point                        |     |                       | 20  | ns   |

| t <sub>OZD</sub>   | SDO Tristate-to-Driven<br>Time | Measured at 10% / 90% point                        |     |                       | 20  | ns   |

| t <sub>OD</sub>    | SDO Output Delay Time          |                                                    |     |                       | 20  | ns   |

| t <sub>CSS</sub>   | CSB Setup Time                 |                                                    | 20  |                       |     | ns   |

| t <sub>CSH</sub>   | CSB Hold Time                  |                                                    | 20  |                       |     | ns   |

| t <sub>IAG</sub>   | Inter-Access Gap               |                                                    | 100 |                       |     | ns   |

| t <sub>DRDYB</sub> | Data ready pulse width         | Data ready pulse at every 1/ODR if no data is read |     | 1/f <sub>sensor</sub> |     | S    |

www.ti.com

## THEORY OF OPERATION

### **Inductive Sensing**

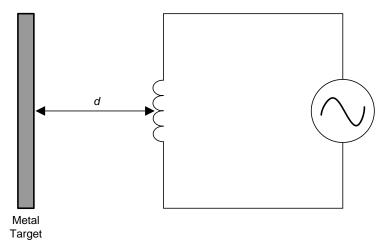

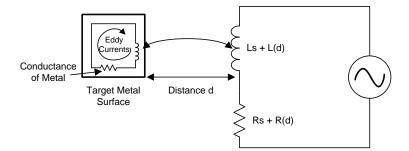

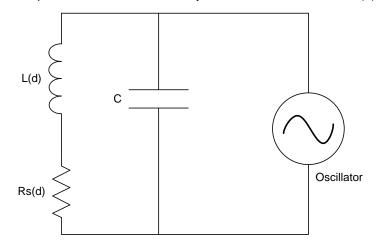

An AC current flowing through a coil will generate an AC magnetic field. If a conductive material, such as a metal target, is brought into the vicinity of the coil, this magnetic field will induce circulating currents (eddy currents) on the surface of the target. These eddy currents are a function of the distance, size, and composition of the target. These eddy currents then generate their own magnetic field, which opposes the original field generated by the coil. This mechanism is best compared to a transformer, where the coil is the primary core and the eddy current is the secondary core. The inductive coupling between both cores depends on distance and shape. Hence the resistance and inductance of the secondary core (Eddy current), shows up as a distant dependent resistive and inductive component on the primary side (coil). The figures below show a simplified circuit model.

Figure 7. Inductor with a Metal Target

Eddy currents generated on the surface of the target can be modeled as a transformer as shown in Figure 8. The coupling between the primary and secondary coils is a function of the distance and conductor's characteristics. In Figure 8, the inductance Ls is the coil's inductance, and Rs is the coil's parasitic series resistance. The inductance L(d), which is a function of distance d, is the coupled inductance of the metal target. Likewise, R(d) is the parasitic resistance of the eddy currents.

Figure 8. Metal Target Modeled as L and R with Circulating Eddy Currents

Generating an alternating magnetic field with just an inductor will consume a large amount of power. This power consumption can be reduced by adding a parallel capacitor, turning it into a resonator as shown in Figure 9. In this manner the power consumption is reduced to the eddy and inductor losses Rs+R(d) only.

Figure 9. LC Tank Connected to Oscillator

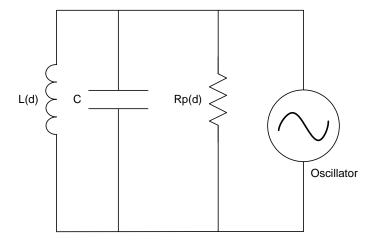

The LDC1000 doesn't measure the series resistance directly; instead it measures the equivalent parallel resonance impedance Rp (see Figure 10). This representation is equivalent to the one shown in Figure 10, where the parallel resonance impedance Rp(d) is given by: Rp(d)=(1/[Rs+R(d)])/([Ls+L(d)])/C.

Figure 10. Equivalent Resistance of R<sub>s</sub> in Parallel with LC Tank

$Rp = (1/Rs)^{*}(L/C).$

www.ti.com

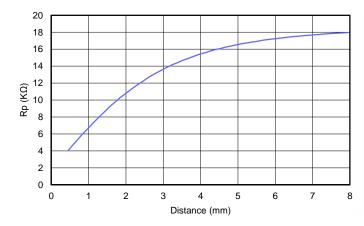

Figure 11 below shows the variation in Rp as a function of distance for a 14mm diameter PCB coil(23 turns,4 mil trace width, 4mil spacing between trace,1oz Cu thickness,FR4). Target used is a Stainless steel 2mm thick.

Figure 11. Typical Rp Vs Distance with 14mm PCB Coil

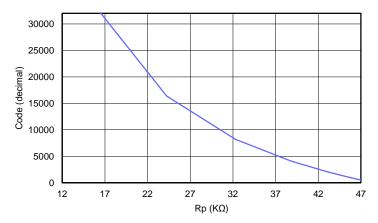

### Measuring Parallel Resonance Impedance and Inductance with LDC1000

The LDC1000 is an Inductance-to-Digital Converter that simultaneously measures the impedance and resonant frequency of an LC resonator. It accomplishes this task by regulating the oscillation amplitude in a closed loop configuration to a constant level, while monitoring the energy dissipated by the resonator. By monitoring the amount of power injected into the resonator, the LDC1000 can determine the value of Rp; it returns this as a digital value which is inversely proportional to Rp. In addition, the LDC1000 can also measure the oscillation frequency of the LC circuit; this frequency is used to determine the inductance of the LC circuit. The oscillation frequency is returned as a digital value.

The LDC1000 supports a wide range of LC combinations, with oscillation frequencies ranging from 5kHz to 5MHz and Rp ranging from 798 $\Omega$  to 3.93M $\Omega$ . This range of Rp can be viewed as the maximum input range of an ADC. As illustrated in Figure 11, the range of Rp is typically a much smaller than maximum input range supported by the LDC1000. To get better resolution in the desired sensing range, the LDC1000 offers programmable input range through the Rp\_MIN and Rp\_MAX registers. Refer to Calculation of Rp Min and Rp Max below for how to set these registers.

When the sensor's resonance impedance Rp drops below the programed Rp\_MIN, the LDC's Rp output will clip at its full scale output. This situation could for example happen when a target comes too close to the coil.

Figure 12. Transfer Characteristics of LDC1000 with Rp\_MIN= 16.160 k $\Omega$  and Rp\_MAX= 48.481 k $\Omega$

(1)

#### The resonance impedance can be calculated from the digital output code as follows:

$R_{\rm P}$  = (R\_PMAX  $\times$  R\_PMIN ) / ( R\_PMIN  $\times$  (1-Y) + R\_PMAX  $\times$  Y ) , in  $\Omega.$

Where:

- Y=Proximity Data/2<sup>15</sup>

- Proximity data is the LDC output, register address 0x21 and 0x22.

**Example:** If Proximity data (address 0x22:0x21) is 5000, Rp\_MIN is 2.394 k $\Omega$ , and Rp\_MAX is 38.785 k $\Omega$ , the resonance impedance is given by:

$Y = 5000/2^{15} = 0.1526$

RP=(38785\*2394)/(2394×(1-0.1526) + 38785×0.1526) =(92851290)/(2028.675 + 5918.591)

RP =11.683 kΩ

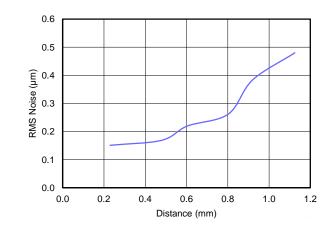

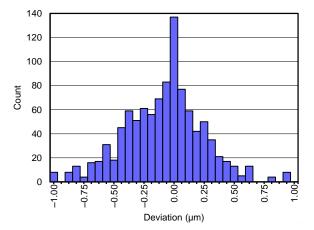

Figure 13 and Figure 14below show the change in RMS noise versus distance and a histogram of noise, with the target at 0.8mm distance from the sensor coil. Data was collected with a 14mm PCB coil(23 turns,4 mil trace width, 4mil spacing between trace,1oz Cu thickness,FR4) with a sensing range of 0.125mm to 1.125mm. At a distance of 0.8mm, the RMS noise is approximately 250nm.

Figure 13. Typical RMS Noise Vs. Distance with PCB Coil

Note that while the LDC1000 has high resolution, its absolute accuracy depends on offset and gain correction which can be achieved by two-point calibration.

### Calculation of Rp Min and Rp Max

Different sensing applications may have a different ranges of the resonance impedance Rp to measure. The LDC1000 measurement range of Rp is controlled by setting 2 registers – Rp\_MIN and Rp\_MAX. For a given application, Rp must never be outside the range set by these register values, otherwise the measured value will be clipped. For optimal sensor resolution, the range of Rp\_MIN to Rp\_MAX should not be unnecessarily large. The following procedure is recommended to determine the Rp\_MIN and Rp\_MAX register values.

### Rp\_MAX

Rp\_MAX sets the upper limit of the LDC1000 resonant impedance input range.

- Configure the sensor such that the eddy current losses are minimized. As an example, for a proximity sensing application, set the distance between the sensor and the target to the maximum sensing distance.

- Measure the resonant impedance Rp using an impedance analyzer.

- Multiply Rp by 2 and use the next higher value from Table 6.

# LDC1000

(2)

**NSTRUMENTS**

EXAS

For example, if Rp at 8mm is measured to be  $18k\Omega$ ,  $18000\times2 = 36000$ . In Table 6, then  $38.785k\Omega$  is the smallest value larger than  $36k\Omega$ ; this corresponds to Rp\_MAX value of 0x11.

Note that setting Rp\_MAX to a value not listed in Table 6 can result in indeterminate behavior.

### Rp\_MIN

Rp\_MIN sets the lower limit of the LDC1000 resonant impedance input range.

- Configure the sensor such that the eddy current losses are maximized. As an example, for a proximity sensing application, set the distance between the sensor and the metal target to the minimum sensing distance.

- Measure the resonant impedance Rp using an impedance analyzer.

- Divide the Rp value by 2 and then select the next lower Rp value from Table 8.

For example, if Rp at 1mm is measured to be  $5k\Omega$ , 5000/2 = 2500. In Table 8 ,  $2.394k\Omega$  is the smallest value lower than  $2.5k\Omega$ ; this corresponds to Rp\_MIN value of 0x3B.

Note that setting Rp\_MIN to a value not listed on Table 8 can result in indeterminate behavior. In addition, Rp\_MIN powers on with a default value of 0x14 which must be set to a value from Table 8 prior to powering on the LDC.

### **Measuring Inductance**

LDC1000 measures the sensor's frequency of oscillation by a frequency counter. The frequency counter timing is set by an external clock or crystal. Either the external clock(8MHz typical) from microcontroller can be provided on the TBCLK pin or a crystal can be connected on the XTALIN and XTALOUT pins. The clock mode is controlled through Clock Configuration register (address 0x05). The sensor resonance frequency is derived from the frequency counter registers value (see registers 0x23 through 0x25) as follows:

Sensor frequency,  $f_{sensor} = (1/3)^*(Fext/Fcount)^*(Response Time)$

where Fext is the frequency of the external clock or crystal, Fcount is the value obtained from the Frequency Counter Data register(address 0x23,0x24,0x25), and Response Time is the programmed response time (see LDC configuration register, address 0x04).

The Inductance can be calculated as follows:

L=1/[C\*(2\* $\pi$ \*f<sub>sensor</sub>)<sup>2</sup>],

where C is the parallel capacitance of the resonator.

**Example:** If Fext=6Mhz, Response time=6144, C=100pF and measured Fcount= 3000 (dec) (address 0x23 through 0x25)

$f_{sensor} = (1/3)^* (600000/3000)^* (6144) = 4.096 Mhz$

Now using, L=1/[C\* $(2^{*}\pi^{*}f_{sensor})^{2}$ ]

Inductance, L = 15.098 uH

The accuracy of measurement largely depends upon the choice of the external time-base clock (TBCLK) or the crystal oscillator (XIN/XOUT).

## **Output Data Rate**

Output data rate of LDC1000 depends on the sensor frequency, f<sub>sensor</sub> and 'Response Time' field in LDC Configuration register(Address:0x04).

Output data rate=( f<sub>sensor</sub>)/(Response Time/3), Sample per second(SPS)

Example: If f<sub>sensor</sub>=5Mhz and Response Time=192

Output data rate= (5M)/(192/3)= 78.125 KSPS

## **Choosing Filter Capacitor (CFA and CFB Pins)**

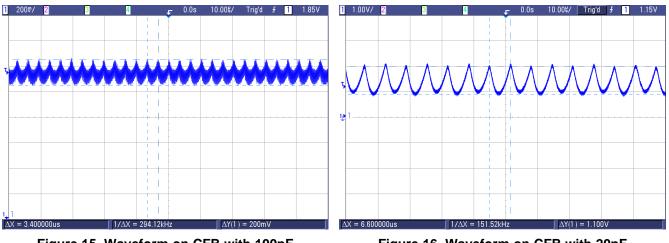

The Filter capacitor is critical to the operation of the LDC1000. The capacitor should be low leakage, temperature stable, and it must not generate any piezoelectric noise (the dielectrics of many capacitors exhibit piezoelectric characteristics and any such noise is coupled directly through Rp into the converter). The optimal capacitance values range from 20pF to 100nF. The value of the capacitor is based on the time constant and resonating frequency of the LC tank.

If a ceramic capacitor is used, then a C0G (or NP0) grade dielectric is recommended; the voltage rating should be  $\geq$ 10V. The traces connecting CFA and CFB to the capacitor should be as short as possible to minimize any parasitics.

For optimal performance, the chosen filter capacitor, connected between pins CFA and CFB, needs to be as small as possible, but large enough such that the active filter does not saturate. The size of this capacitor depends on the time constant of the sense coil, which is given by L/Rs, (L=inductance, Rs=series resistance of the inductor at oscillation frequency). The larger this time constant, the larger filter capacitor is required. Hence, this time constant reaches its maximum when there is no target present in front of the sensing coil.

The following procedure can be used to find the optimal filter capacitance:

- 1. Start with a large filter capacitor. For a ferrite core coil, 10nF is usually large enough. For an air coil or PCB coil, 100pF is usually large enough.

- 2. Power on the LDC and set the desired register values. Minimize the eddy currents losses by ensuring there is maximum clearance between the target and the sensing coil.

- Observe the signal on the CFB pin using a scope. Since this node is very sensitive to capacitive loading, it is recommended to use an active probe. As an alternative, a passive probe with a 1kΩ series resistance between the tip and the CFB pin can be used.

- 4. Vary the values of the filter capacitor until that the signal observed on the CFB pin has an amplitude of approximate 1V peak-to-peak. This signal scales linearly with the reciprocal of the filter capacitance. For example, if a 100pF filter capacitor is applied and the signal observed on the CFB pin has a peak-to-peak value of 200mV, the desired 1V peak-to-peak value is obtained using a 200mV / 1V \* 100pF = 20pF filter capacitor.

The waveforms below were taken on the CFB pin with a 14mm, 2 layer PCB coil(23 turns,4 mil trace width, 4mil spacing between trace,1oz Cu thickness,FR4):

Figure 15. Waveform on CFB with 100pF

Figure 16. Waveform on CFB with 20pF

EXAS **ISTRUMENTS**

www.ti.com

SNOSCX2-SEPTEMBER 2013

## **PROGRAMMABLE REGISTERS**

Table 3. Register Map<sup>(1)(2)(3)</sup>

|                                       |         |           |         |                   | S. Regist                |             |                |            |       |             |              |

|---------------------------------------|---------|-----------|---------|-------------------|--------------------------|-------------|----------------|------------|-------|-------------|--------------|

| Register<br>Name                      | Address | Direction | Default | Bit 7             | Bit 6                    | Bit 5       | Bit 4          | Bit 3      | Bit 2 | Bit 1       | Bit 0        |

| Device ID                             | 0x00    | RO        | 0x80    |                   |                          |             | Devi           | ce ID      | •     |             |              |

| Rp_MAX                                | 0x01    | R/W       | 0x0E    |                   |                          |             | Rp Ma          | ximum      |       |             |              |

| Rp_MIN                                | 0x02    | R/W       | 0x14    |                   | Rp Minimum               |             |                |            |       |             |              |

| Sensor<br>Frequency                   | 0x03    | R/W       | 0x45    |                   | Min Resonating Frequency |             |                |            |       |             |              |

| LDC<br>Configuration                  | 0x04    | R/W       | 0x1B    | F                 | Reserved(00              | 00)         | Amp            | itude      | R     | esponse Tir | ne           |

| Clock<br>Configuration                | 0x05    | R/W       | 0x01    |                   |                          | Reserved    | 1(000000)      |            |       | CLK_SE<br>L | CLK_PD       |

| Comparator<br>Threshold<br>High LSB   | 0x06    | R/W       | 0xFF    |                   | Threshold High LSB       |             |                |            |       |             |              |

| Comparator<br>Threshold<br>High MSB   | 0x07    | R/W       | 0xFF    |                   | Threshold High MSB       |             |                |            |       |             |              |

| Comparator<br>Threshold<br>Low LSB    | 0x08    | R/W       | 0x00    | Threshold Low LSB |                          |             |                |            |       |             |              |

| Comparator<br>Threshold<br>Low MSB    | 0x09    | R/W       | 0x00    | Threshold Low MSB |                          |             |                |            |       |             |              |

| INTB Pin<br>Configuration             | 0x0A    | R/W       | 0x00    |                   | Re                       | eserved(000 | 00)            |            |       | INTB_MODI   | E            |

| Power<br>Configuration                | 0x0B    | R/W       | 0x00    |                   |                          | Res         | erved(0000     | 000)       |       |             | PWR_M<br>ODE |

| Status                                | 0x20    | RO        |         | OSC<br>Dead       | DRDYB                    | Wake-up     | Compara<br>tor |            | Do no | ot Care     |              |

| Proximity<br>Data LSB                 | 0x21    | RO        |         |                   |                          |             | Proximity      | Data[7:0]  |       |             |              |

| Proximity<br>Data MSB                 | 0x22    | RO        |         |                   |                          |             | Proximity      | Data[15:8] |       |             |              |

| Frequency<br>Counter Data<br>LSB      | 0x23    | RO        |         | ODR LSB           |                          |             |                |            |       |             |              |

| Frequency<br>Counter Data<br>Mid-Byte | 0x24    | RO        |         | ODR Mid Byte      |                          |             |                |            |       |             |              |

| Frequency<br>Counter Data<br>MSB      | 0x25    | RO        |         |                   |                          |             | ODR            | MSB        |       |             |              |

Values of Bits which are unused should be set to default values only.

Registers 0x01 through 0x05 are Read Only when the part is awake (DIS\_STBY bit is SET)

R/W: Read/Write. RO: Read Only. WO: Write Only.

## **Register Description**

#### Table 4. Revision ID

| Address = 0x00, Default=0x80, Direction=RO |             |                         |  |  |

|--------------------------------------------|-------------|-------------------------|--|--|

| Bit Field                                  | Field Name  | Description             |  |  |

| 7:0                                        | Revision ID | Revision ID of Silicon. |  |  |

# LDC1000

SNOSCX2-SEPTEMBER 2013

www.ti.com

## Table 5. Rp\_MAX

| Address = 0x01, Default=0x0E, Direction=R/W |            |                                                                                                                                      |  |  |  |

|---------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit Field                                   | Field Name | Description                                                                                                                          |  |  |  |

| 7:0                                         | Rp Maximum | Maximum Rp that LDC1000 needs to<br>measure. Configures the input dynamic<br>range of LDC1000. See Table 6 for register<br>settings. |  |  |  |

## Table 6. Register settings for Rp\_MAX

| Register setting | Rp (kΩ)  |

|------------------|----------|

| 0x00             | 3926.991 |

| 0x01             | 3141.593 |

| 0x02             | 2243.995 |

| 0x03             | 1745.329 |

| 0x04             | 1308.997 |

| 0x05             | 981.748  |

| 0x06             | 747.998  |

| 0x07             | 581.776  |

| 0x08             | 436.332  |

| 0x09             | 349.066  |

| 0x0A             | 249.333  |

| 0x0B             | 193.926  |

| 0x0C             | 145.444  |

| 0x0D             | 109.083  |

| 0x0E             | 83.111   |

| 0x0F             | 64.642   |

| 0x10             | 48.481   |

| 0x11             | 38.785   |

| 0x12             | 27.704   |

| 0x13             | 21.547   |

| 0x14             | 16.160   |

| 0x15             | 12.120   |

| 0x16             | 9.235    |

| 0x17             | 7.182    |

| 0x18             | 5.387    |

| 0x19             | 4.309    |

| 0x1A             | 3.078    |

| 0x1B             | 2.394    |

| 0x1C             | 1.796    |

| 0x1D             | 1.347    |

| 0x1E             | 1.026    |

| 0x1F             | 0.798    |

### Table 7. Rp\_MIN

|                            | Address = 0x02, Default=0x14, Direction=R/W |                                                                                                                                            |  |  |  |

|----------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit Field Name Description |                                             |                                                                                                                                            |  |  |  |

| 7:0                        | Rp Minimum                                  | Minimum Rp that LDC1000 needs to measure. Configures the input dynamic range of LDC1000. See Table 8 for register settings. <sup>(1)</sup> |  |  |  |

(1) This Register needs a mandatory write as it defaults to 0x14.

### SNOSCX2-SEPTEMBER 2013

## Table 8. Register Settings for Rp MIN

| Table 8. Register Settings for Rp_inin |          |  |

|----------------------------------------|----------|--|

| Register setting                       | Rp (kΩ)  |  |

| 0x20                                   | 3926.991 |  |

| 0x21                                   | 3141.593 |  |

| 0x22                                   | 2243.995 |  |

| 0x23                                   | 1745.329 |  |

| 0x24                                   | 1308.997 |  |

| 0x25                                   | 981.748  |  |

| 0x26                                   | 747.998  |  |

| 0x27                                   | 581.776  |  |

| 0x28                                   | 436.332  |  |

| 0x29                                   | 349.066  |  |

| 0x2A                                   | 249.333  |  |

| 0x2B                                   | 193.926  |  |

| 0x2C                                   | 145.444  |  |

| 0x2D                                   | 109.083  |  |

| 0x2E                                   | 83.111   |  |

| 0x2F                                   | 64.642   |  |

| 0x30                                   | 48.481   |  |

| 0x31                                   | 38.785   |  |

| 0x32                                   | 27.704   |  |

| 0x33                                   | 21.547   |  |

| 0x34                                   | 16.160   |  |

| 0x35                                   | 12.120   |  |

| 0x36                                   | 9.235    |  |

| 0x37                                   | 7.182    |  |

| 0x38                                   | 5.387    |  |

| 0x39                                   | 4.309    |  |

| 0x3A                                   | 3.078    |  |

| 0x3B                                   | 2.394    |  |

| 0x3C                                   | 1.796    |  |

| 0x3D                                   | 1.347    |  |

| 0x3E                                   | 1.026    |  |

| 0x3F                                   | 0.798    |  |

|                                        |          |  |

# Table 9. Sensor Frequency<sup>(1)(2)</sup>

| Address = 0x03, Default=0x45, Direction=R/W |                          |                                                                                                                                                                                                   |

|---------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit Field                                   | Field Name               | Description                                                                                                                                                                                       |

| 7:0                                         | Min Resonating Frequency | Sets the minimum resonating frequency to approximately 20% below the lowest resonating frequency of the sensor with no target in front. Use the formula below to determine the value of register. |

(1)  $\mathbf{N} = 68.94 \times \log_{10}(F/2000)$

$\mathbf{F} = 20\%$  below resonating frequency, Hz  $\mathbf{N} = \text{Register Value. Round to nearest value.}$

(2) Example:

Sensor Frequency: 1MHz F = 0.8\*1Mhz=800Khz

N = 68.94 \* log<sub>10</sub>(800KHz/2000)= Round to nearest(179.38)=179 (Value to be programmed in Sensor Frequency register)

#### SNOSCX2-SEPTEMBER 2013

# Table 10. LDC Configuration

| Address = 0x04, Default=0x1B, Direction=R/W |               |                                |

|---------------------------------------------|---------------|--------------------------------|

| Bit Field                                   | Field Name    | Description                    |

| 7:5                                         | Reserved      | Reserved to 0                  |

| 4:3                                         | Amplitude     | Sets the oscillation amplitude |

|                                             |               | 00:1V                          |

|                                             |               | 01:2V                          |

|                                             |               | 10:4V                          |

|                                             |               | 11:Reserved                    |

| 2:0                                         | Response Time | 000: Reserved                  |

|                                             |               | 001: Reserved                  |

|                                             |               | 010: 192                       |

|                                             |               | 011: 384                       |

|                                             |               | 100: 768                       |

|                                             |               | 101: 1536                      |

|                                             |               | 110: 3072                      |

|                                             |               | 111: 6144                      |

### Table 11. Clock Configuration

|           | Address = 0x05, Default=0x01, Direction=R/W |                                                                                                                             |  |

|-----------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| Bit Field | Field Name                                  | Description                                                                                                                 |  |

| 7:2       | Reserved                                    | Reserved to 0                                                                                                               |  |

| 1         | CLK_SEL                                     | 1:External Crystal used for Frequency Counter (XIN/XOUT).<br>0:External Time-Base Clock used for Frequency Counter (TBCLK). |  |

| 0         | CLK_PD                                      | 1:Disable External time base clock. Crystal Oscillator Power Down.<br>0:Enable External time base clock.                    |  |

### Table 12. Comparator Threshold High LSB

| Address = 0x06, [ | Default=0xFF, Direction=R/W |

|-------------------|-----------------------------|

|                   |                             |

| Bit Field | Field Name                                | Description                                                                                                                                                                                                             |

|-----------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0       | Threshold High LSB<br>Threshold High[7:0] | Least Significant byte of Threshold High Register. This register is a buffer.<br>Read will reflect the current value of Threshold High [7:0] .See register<br>0x07 for details on Updating the Threshold High register. |

### Table 13. Comparator Threshold High MSB

| Address = 0x07, Default=0xFF, Direction=R/W |                                            |                                                                                                                                                                                                                                                                               |

|---------------------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit Field                                   | Field Name                                 | Description                                                                                                                                                                                                                                                                   |

| 7:0                                         | Threshold High MSB<br>Threshold High[15:8] | Most Significant byte of Threshold High Register. Write to this register copies the contents of 0x06 register and Writes to Threshold High register[15:0]. Read will return Threshold high [15:8]. To Update Threshold high register write register 0x06 first and then 0x07. |

## Table 14. Comparator Threshold Low LSB

|           | Address = 0x08, Default=0x00, Direction=R/W |                                                                                                                                                                                                                   |  |

|-----------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit Field | Field Name                                  | Description                                                                                                                                                                                                       |  |

| 7:0       | Threshold Low LSB<br>Threshold Low[7:0]     | Least Significant byte of Threshold Low Value. This register is a buffer.<br>Read will reflect the current value of Threshold Low [7:0]. See register<br>0x09 for details on Updating the Threshold Low register. |  |

TEXAS INSTRUMENTS

www.ti.com

#### SNOSCX2-SEPTEMBER 2013

### Table 15. Comparator Threshold Low MSB

| Address = 0x09, Default=0x00, Direction=R/W |                                          |                                                                                                                                                                                                                                                                                         |

|---------------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit Field                                   | Field Name                               | Description                                                                                                                                                                                                                                                                             |

| 7:0                                         | Threshold Low MSB<br>Threshold Low[15:8] | Most Significant byte of Threshold Low Register. Write to this register<br>copies the contents of 0x08 register and Writes to Threshold Low<br>register[15:0]. Read will return Threshold Low [15:8]. To Update Threshold<br>low register write register addr 0x08 first and then 0x09. |

### Table 16. INTB Pin Configuration

| Address = 0x0A, Default=0x00, Direction=R/W |            |                                                         |

|---------------------------------------------|------------|---------------------------------------------------------|

| Bit Field                                   | Field Name | Description                                             |

| 7:3                                         | Reserved   | Reserved to 0                                           |

| 2:0                                         | Mode       | 100: DRDYB Enabled on INTB pin                          |

|                                             |            | 010: INTB pin indicates the status of Comparator output |

|                                             |            | 001: Wake-up Enabled on INTB pin                        |

|                                             |            | 000: All modes disabled                                 |

|                                             |            | All other combinations are Reserved                     |

### Table 17. Power Configuration

|           | Address = 0x0B, Default=0x00, Direction=R/W |                                                         |  |

|-----------|---------------------------------------------|---------------------------------------------------------|--|

| Bit Field | Field Name                                  | Description                                             |  |

| 7:1       | Reserved                                    | Reserved to 0                                           |  |

| 0         | PWR_MODE                                    | 0:Stand-By mode<br>1:Active Mode. Conversion is Enabled |  |

### Table 18. Status

| Address = 0x20, Default=NA, Direction=RO |             |                                                                        |

|------------------------------------------|-------------|------------------------------------------------------------------------|

| Bit Field                                | Field Name  | Description                                                            |

| 7                                        | OSC status  | 1:Indicates oscillator overloaded and stopped                          |

|                                          |             | 0:Oscillator working                                                   |

| 6                                        | Data Ready  | 0:Data is ready to be read                                             |

|                                          |             | 1:No new data available                                                |

| 5                                        | Wake-up     | 0:Wake-up triggered. Proximity data is more than Threshold High value. |

|                                          |             | 1:Wake-up disabled                                                     |

| 4                                        | Comparator  | 0:Proximity data is more than Threshold High value                     |

|                                          |             | 1:Proximity data is less than Threshold Low value                      |

| 3:0                                      | Do not Care |                                                                        |

## Table 19. Proximity Data LSB

| Address = 0x21, Default=NA, Direction=RO |                     |                                          |  |

|------------------------------------------|---------------------|------------------------------------------|--|

| Bit Field                                | Field Name          | Description                              |  |

| 7:0                                      | Proximity Data[7:0] | Least Significant Byte of Proximity Data |  |

### Table 20. Proximity Data MSB

| Address = 0x22, Default=NA, Direction=RO |                       |                                         |  |

|------------------------------------------|-----------------------|-----------------------------------------|--|

| Bit Field Field Name D                   |                       | Description                             |  |

| 7:0                                      | Proximity data [15:8] | Most Significant Byte of Proximity data |  |

www.ti.com

## Table 21. Frequency Counter LSB

#### Address = 0x23 Default=NA Direction=RO

| Address = 0x23, Detault=NA, Direction=RO |                    |                                                                                                                                      |  |

|------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit Field                                | Field Name         | Description                                                                                                                          |  |

| 7:0                                      | ODR LSB (ODR[7:0]) | LSB of Output data rate. Sensor frequency can be calculated using the<br>output data rate. Please refer to the Measuring Inductance. |  |

#### Table 22. Frequency Counter Mid-Byte

| Address = 0x24, Default=NA, Direction=RO |                          |                                 |  |

|------------------------------------------|--------------------------|---------------------------------|--|

| Bit Field Name Description               |                          | Description                     |  |

| 7:0                                      | ODR Mid byte (ODR[15:8]) | Middle Byte of Output data rate |  |

#### Table 23. Frequency Counter MSB

| Address = 0x25, Default=NA, Direction=RO |                      |                         |  |

|------------------------------------------|----------------------|-------------------------|--|

| Bit Field Name Description               |                      | Description             |  |

| 7:0                                      | ODR MSB (ODR[23:16]) | MSB of Output data rate |  |

Care must be taken to ensure that Proximity Data[15:0] and Frequency Counter[23:0] are all from same conversion. Conversion data is updated to these registers only when a read is initiated on 0x21 register. If the read is delayed between subsequent conversions, these registers are not updated until another read is initiated on 0x21.

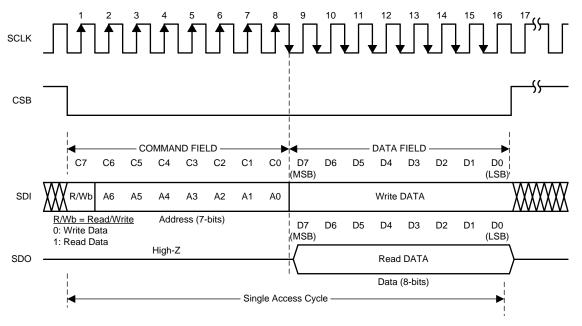

### DIGITAL INTERFACE

The LDC1000 utilizes a 4-wire SPI interface to access control and data registers. The LDC1000 is an SPI slave device and does not initiate any transactions.

#### **SPI Description**

A typical serial interface transaction begins with an 8-bit instruction, which is comprised of a read/write bit (MSB, R=1) and a 7 bit address of the register, followed by a Data field which is typically 8 bits. However, the data field can be extended to a multiple of 8 bits by providing sufficient SPI clocks. Refer to the Extended SPI Transactions section below.

Figure 17. Serial Interface Protocol

www.ti.com

Each assertion of chip select bar (CSB) starts a new register access. The R/Wb bit in the command field configures the direction of the access; a value of 0 indicates a write operation and a value of 1 indicates a read operation. All output data is driven on the falling edge of the serial clock (SCLK), and all input data is sampled on the rising edge of the serial clock (SCLK). Data is written into the register on the rising edge of the 16th clock. It is required to deassert CSB after the 16th clock; if CSB is deasserted before the 16th clock, no data write will occur.

#### **Extended SPI Transactions**

A transaction may be extended to multiple registers by keeping the CSB asserted beyond the stated 16 clocks. In this mode, the register addresses increment automatically. CSB must be asserted during 8\*(1+N) clock cycles of SCLK, where N is the amount of bytes to write or read during the transaction.

During an extended read access, SDO outputs the register contents every 8 clock cycles after the initial 8 clocks of the command field. During an extended write access, the data is written to the registers every 8 clock cycles after the initial 8 clocks of the command field.

Extended transactions can be used to read 16-bits of Proximity data and 24-bits of frequency data all in one SPI transaction by initiating a read from register 0x21.

### **INTB Pin Modes**

The INTB pin is a configurable output pin which can be used to drive an interrupt on an MCU. The LDC1000 provides three different modes on INTB Pin:

- 1. Comparator Mode

- 2. Wake-Up Mode

- 3. DRDY Mode

LDC1000 has a build-in High and Low trigger threshold registers which can be as a comparator with programmable hysteresis or a special mode which can be used to wake-up an MCU. These modes are explained in detail below.

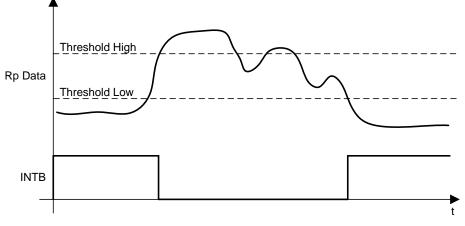

#### **Comparator Mode**

In the Comparator mode, the INTB pin is asserted or de-asserted when the proximity register value increases above Threshold High or decreases below Threshold Low registers respectively. In this mode, the LDC1000 essentially behaves as a proximity switch with programmable hysteresis.

Figure 18. Behavior of INTB Pin in Comparator Mode

## Wake-Up Mode

www.ti.com

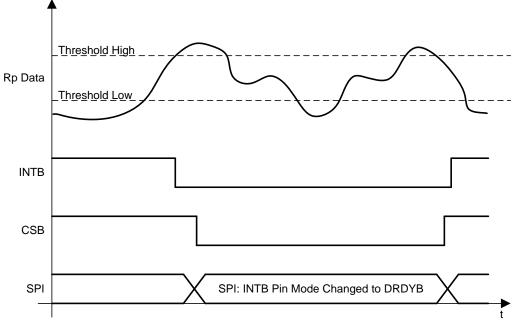

In Wake-Up mode, the INTB pin is asserted when proximity register value increases above Threshold High and de-asserted when wake-up mode is disabled in INTB pin mode register.

This Mode can be used to wake-up an MCU which is asleep, to conserve power.

Figure 19. Behavior of INTB Pin in Wake-Up Mode

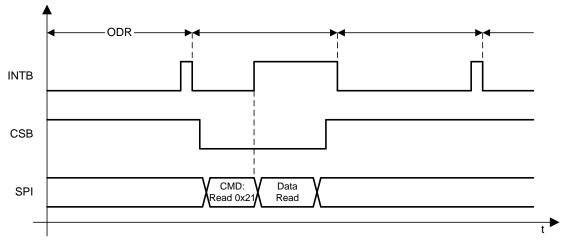

#### **DRDYB Mode**

In DRDY mode (default), the INTB pin is asserted every time the conversion data is available and de-asserted once the read command on register 0x21 is registered internally; if the read is in progress, the pin is pulsed instead.

Figure 20. Behavior of INTB Pin in DRDYB Mode

Texas Instruments

www.ti.com

SNOSCX2-SEPTEMBER 2013

## **TYPICAL APPLICATIONS**

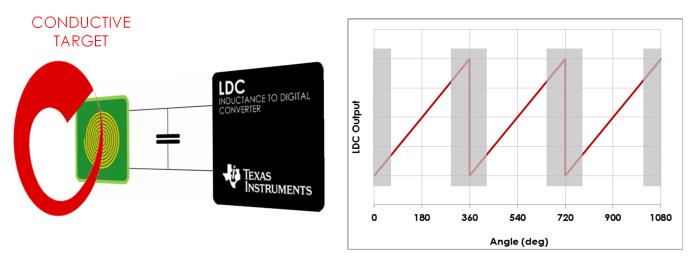

Figure 22. Linear Position Sensing

Figure 23. Angular Position Sensing

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                                 | Applications                  |                                   |

|------------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio                | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com                | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com            | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com                     | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com                      | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks               | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com                | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com                    | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com                 |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap                 | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconnectivity |                               |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated