## iC-MB4

## **BISS INTERFACE MASTER**

Rev B2, Page 1/40

#### **FEATURES**

- ♦ Bidirectional *BiSS* communication with up to 8 slaves

- ♦ Supports SSI protocol for unidirectional data transmission

- Synchronous sensor data acquisition with cyclic transfer at data rates of up to 10 Mbit/s

- ♦ Configurable interface with TTL, CMOS, RS422 or LVDS

- ♦ Slave register operations during cyclic data transfers

- ♦ Automatic compensation of line delays and conversion times

- Data lengths of up to 64 bit for sensor data, configurable for each slave

- ♦ Data verification by CRC polynomials of up to 16 bits per slave

- ♦ Separate memory banks enable free controller access during BiSS sensor data transfers

- ♦ 64 bytes memory for bidirectional slave register communication

- ♦ Parallel interface with 8 bit data/address bus services Intel and Motorola devices with combined data and address bus

- ♦ Serial controller communication by SPI<sup>TM</sup>-compatible mode

- ♦ Single 3 V to 5 V supply, industrial temperature range

#### **APPLICATIONS**

- Bidirectional communication in multi sensor systems

- ♦ Linear and rotary encoders

- ♦ Motor feedback systems

- ♦ PLC systems

- Drives

## **BISS INTERFACE MASTER**

Rev B2, Page 2/40

#### **DESCRIPTION**

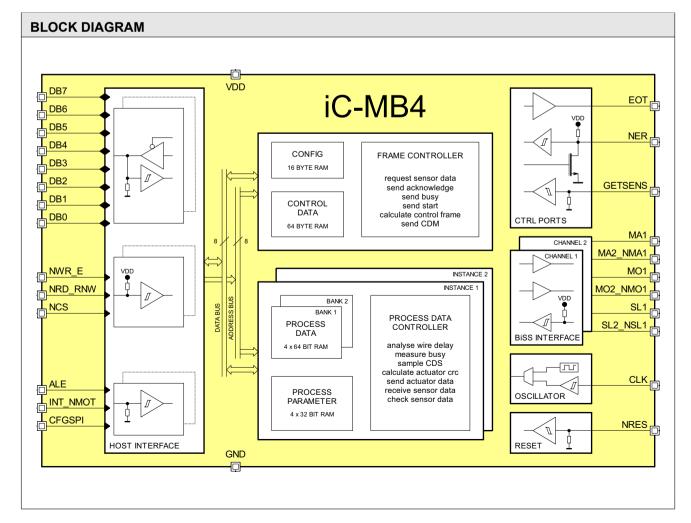

iC-MB4 is a single-chip *BiSS*/SSI interface master controller featuring an 8 bit bus interface to industrial standard microcontrollers. Alternatively an SPI interface enables serial communication between iC-MB4 and the connected microcontroller. Up to 8 *BiSS* slaves can be accessed. The *BiSS* devices are connected to clock line MA1 and data return line SL1 using RS422 transceivers (Figure 2). The *BiSS* devices can be connected directly in noise-free environments. A maximum of 8 *BiSS* slaves is supported, each with their own configurable data sections covering:

- 1. Sensor data from 0 to 64 bit (for measurement data, flags like alarm and warning, life cycle counter, ...)

- 2. Register data with 128 bytes per slave ID (e.g. for device parameters)

iC-MB4 provides two RAM memory banks for each slave, enabling parallel access of the microcontroller while new sensor data is being read in. A 64 byte memory supports register transfers. Sensor data acquisition is started by a microcontroller command or via pin GETSENS. Alternatively, iC-MB4 can also read in new sensor data automatically; the cycle time in this instance can be set as required. The end of sensor data acquisition and reading is signaled at pin

EOT by a high; if faults occur during transmission pin NER signals a low. Errors in communication can be verified by the microcontroller via a status register; a system error message can also enter this register if bidirectional message pin NER is kept low by external intervention. iC-MB4 generates a clock signal for sensor communication using an internal 20 MHz oscillator. The clock can also be supplied externally. iC-MB4 is based on the *BiSS* master IP family MB100 X.

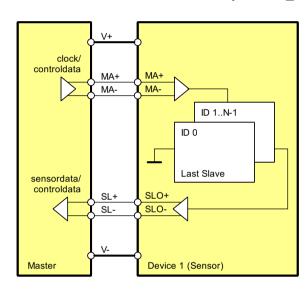

Figure 1: Point-to-point connection of iC-MB4 to one device with several slaves

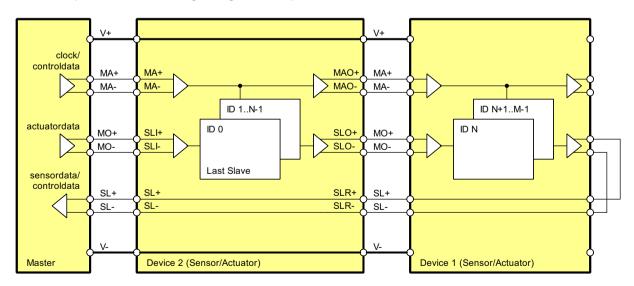

Figure 2: Example network of iC-MB4 and two devices

The device offered here is a multifunctional iC that contains integrated BiSS C interface components. The BiSS C process is protected by patent DE 10310622 B4 owned by iC-Haus GmbH. Users benefit from the open BiSS C protocol with a free license which is necessary when using the BiSS C protocol in conjunction with this iC.

Download the license at www.biss-interface.com/BUA

Rev B2, Page 3/40

#### **PACKAGING INFORMATION TO JEDEC**

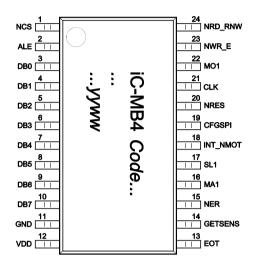

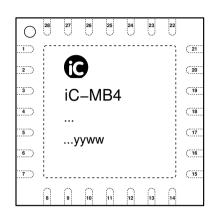

## PIN CONFIGURATION TSSOP24 (topview)

#### PIN FUNCTIONS No. Name **Function SPI Communication Mode** (CFGSPI = 1) 1 NCS SPI Chip Select Input, active low 2 ALE SPI Clock Input 3 DB0 SPI Serial Data Input 4 DB1 SPI Serial Data Output 7 DB4 SPI2 Chip Select Input, active low 8 DB5 SPI2 Clock Input SPI2 Serial Data Input 9 DB6 10 DB7 SPI2 Serial Data Output **Data Bus Communication Mode** (CFGSPI = 0)1 NCS Chip Select Input, active low 2 ALE Address Latch Enable Input Data Bus Input/Output 3 DB0 Data Bus Input/Output 4 DB1 5 DB2 Data Bus Input/Output 6 DB3 Data Bus Input/Output Data Bus Input/Output 7 DB4 8 DB5 Data Bus Input/Output 9 DB6 Data Bus Input/Output Data Bus Input/Output 10 DB7 11 GND Ground 12 VDD +3 V ... +5.5 V Supply Voltage 13 EOT End of transmission Output 14 GETSENS Sensor Data Request Input **15 NER** Error Message Input/Output. low active 16 MA1 **BiSS Clock Line Output** BiSS Data Line Input 17 SL1 Communication Mode Select Input 18 INT NMOT (Intel = 1, Motorola = 0) 19 CFGSPI Serial/Parallel Mode Select Input (serial SPI = 1, parallel = 0) 20 NRES Reset Input. low active 21 CLK External Clock Input 22 MO1 BiSS Data Line Output Intel Mode (INT\_NMOT = 1) 23 NWR E Write Input, active low 24 NRD\_RNW Read Input, active low

Motorola Mode (INT\_NMOT = 0)

Enable Input, active high

24 NRD RNW Read/Not-Write Select Input

23 NWR E

**PIN FUNCTIONS**

Rev B2, Page 4/40

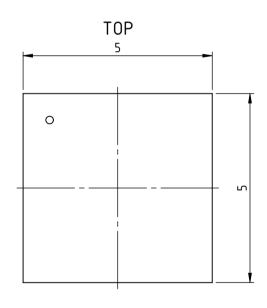

## PIN CONFIGURATION QFN28 5 mm x 5 mm (topview)

| No.                                                          | Name                                                                       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28<br>1                                                      | NCS<br>ALE<br>DB0<br>DB1                                                   | SPI Communication Mode<br>(CFGSPI = 1)<br>SPI Chip Select Input, active low<br>SPI Clock Input<br>SPI Serial Data Input<br>SPI Serial Data Output                                                                                                                                                                                                                                                                                                                                              |

| 6<br>7                                                       | DB4<br>DB5<br>DB6<br>DB7                                                   | SPI2 Chip Select Input, active low<br>SPI2 Clock Input<br>SPI2 Serial Data Input<br>SPI2 Serial Data Output                                                                                                                                                                                                                                                                                                                                                                                    |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13 | DB0 DB1 DB2 DB3 DB4 DB5 DB6 DB7 GND VDD EOT GETSENS NER  n.c. MA1 MA2_NMA1 | Data Bus Communication Mode (CFGSPI = 0) Data Bus Input/Output Coutput Data Bus Input/Output Data Bus Input/Output Data Bus Input/Output Data Bus Input/Output Coutput Coutput Coutput Sensor Data Request Input Error Message Input/Output, Iow active Iow active Iow Coutput Diss Clock Line Output Diss Clock Line Output Channel |

| 17<br>18                                                     | SL1<br>SL2_NSL1<br>INT_NMOT                                                | 2<br>BiSS Data Line Input<br>BiSS Data Line Input Channel 2<br>Communication Mode Select Input                                                                                                                                                                                                                                                                                                                                                                                                 |

| 20                                                           | CFGSPI                                                                     | (Intel = 1, Motorola = 0)<br>Serial/Parallel Mode Select Input<br>(serial SPI = 1, parallel = 0)                                                                                                                                                                                                                                                                                                                                                                                               |

| 22<br>23<br>24                                               | NRES<br>CLK<br>MO1<br>MO2_NMO1<br>NWR_E                                    | Reset Input, low active External Clock Input BiSS Data Line Output BiSS Data Line Output Channel 2 Write Input, active low (Intel) Enable Input, active high (Mo-                                                                                                                                                                                                                                                                                                                              |

| 26                                                           | NRD_RNW                                                                    | torola) Read Input, active low (Intel) Read/Not-Write Select Input                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                              | NCS<br>ALE                                                                 | (Motorola) Chip Select Input, active low Address Latch Enable Input                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TP                                                           |                                                                            | Thermal Pad (GND)                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

Rev B2, Page 5/40

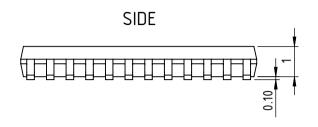

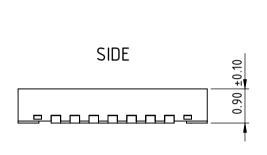

## **PACKAGE DIMENSIONS TSSOP24**

# TOP 7.80 0.65 0.25

All dimensions given in mm. Tolerances of form and position according to JEDEC MO–153

drb\_tssop24-1\_pack\_1, 8:1

Rev B2, Page 6/40

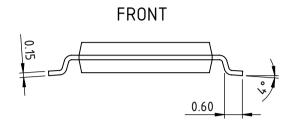

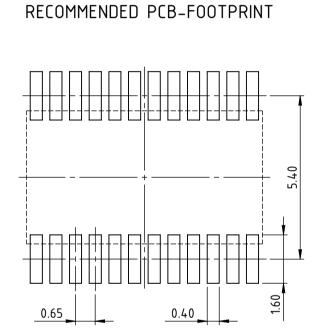

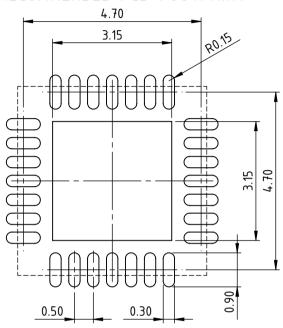

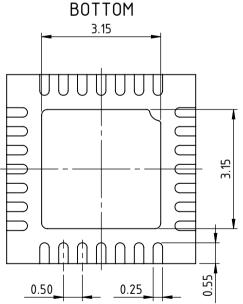

## PACKAGE DIMENSIONS QFN28 5 mm x 5 mm

## RECOMMENDED PCB-FOOTPRINT

All dimensions given in mm. Tolerances of form and position according to JEDEC MO-220.

drc\_qfn28-5x5-2\_pack\_1, 10:1

Rev B2, Page 7/40

## **ABSOLUTE MAXIMUM RATINGS**

Beyond these values damage may occur; device operation is not guaranteed.

| Item | Symbol              | Parameter                                  | Conditions                                  |            |            | Unit |

|------|---------------------|--------------------------------------------|---------------------------------------------|------------|------------|------|

| No.  | -                   |                                            |                                             | Min.       | Max.       |      |

| G001 | VDD                 | Voltage at VDD                             |                                             | -0.3       | 6          | V    |

| G002 | I(VDD)              | Current in VDD                             |                                             | -20        | 30         | mA   |

| G003 | V()                 | Voltage at all pins, excluding VDD and GND | V() VDD + 0.3 V                             | -0.3       | 6          | V    |

| G004 | I()                 | Current in all pins excluding VDD and GND  |                                             | -10        | 10         | mA   |

| G005 | V <sub>esd</sub> () | ESD Susceptibility at all pins             | HBM, 100 pF discharged through 1.5 $\Omega$ |            | 2          | kV   |

| G006 | Tj                  | Operating Junction Temperature             | VDD = 3.0 V 4.5 V<br>VDD = 4.5 V 5.5 V      | -40<br>-40 | 125<br>140 | °C   |

| G007 | Ts                  | Storage Temperature Range                  |                                             | -40        | 150        | °C   |

## **THERMAL DATA**

Operating Conditions: VDD = 3.0 V...5.5 V

| Item | Symbol                 | Parameter                                       | Conditions                                                              |      |      |      | Unit |

|------|------------------------|-------------------------------------------------|-------------------------------------------------------------------------|------|------|------|------|

| No.  |                        |                                                 |                                                                         | Min. | Тур. | Max. |      |

| T01  | Та                     | Standard Operating Ambient<br>Temperature Range |                                                                         | -40  |      | 85   | °C   |

| T02  | Ta <sub>ET</sub>       | Extended Operating Ambient<br>Temperature Range | VDD = 4.5 V 5.5 V available on request                                  | -40  |      | 125  | °C   |

| T03  | R <sub>thjaTSSOP</sub> | Thermal Resistance Chip to Ambient              | TSSOP24 surface mounted, no special heat sink                           |      | 80   |      | K/W  |

| T04  | R <sub>thjaQFN</sub>   | Thermal Resistance Chip to Ambient              | QFN28 package mounted on PCB, thermal pad at approx. 2 cm² cooling area |      | 40   |      | K/W  |

Rev B2, Page 8/40

## **ELECTRICAL CHARACTERISTICS**

Operating Conditions: VDD = 3.0 V...5.5 V. Ti = -40...125 °C. unless otherwise stated

| Item | Symbol       | Parameter                                                                        | Conditions                                                                |            |            |            | Unit     |

|------|--------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------|------------|------------|----------|

| No.  |              |                                                                                  |                                                                           | Min.       | Тур.       | Max.       |          |

|      | Device       |                                                                                  | 1                                                                         | 1 -        |            |            |          |

| 001  | VDD          | Permissible Supply Voltage                                                       |                                                                           | 3          |            | 5.5        | V        |

| 002  | I(VDD)       | Supply Current in VDD                                                            | outputs not loaded, f(CLK) = 20 MHz                                       |            |            | 20         | mA       |

| 003  | Vc()hi       | Clamp Voltage hi at all pins excluding VDD, GND, MA1, MO1, SL1                   | Vc()hi = V() - VDD, I() = 1 mA; outputs tristate                          | 0.3        |            | 1.75       | V        |

| 004  | Vc()lo       | Clamp Voltage lo at all pins ex-<br>cluding VDD, GND                             | I() = -1mA; outputs tristate                                              | -1.6       |            | -0.3       | V        |

|      |              | SPI, INT_NMOT, NCS, ALE, NRD                                                     | _RNW, NWR_E, DB70                                                         |            |            |            |          |

| A01  | Vs()hi       | Saturation Voltage hi at DB70                                                    | Vs()hi = VDD - V();<br>VDD = 4.5 V, I() = -4 mA<br>VDD = 3 V; I() = -2 mA |            |            | 0.4<br>0.4 | V<br>V   |

| A02  | Vs()lo       | Saturation Voltage lo at DB70                                                    | VDD = 4.5 V, I() = 4 mA<br>VDD = 3 V, I() = 2 mA                          |            |            | 0.4<br>0.4 | V        |

| A03  | Vt()hi       | Threshold Voltage hi at CFGSPI, INT_NMOT, NCS, ALE, NRD_RNW, NWR_E, DB70         |                                                                           |            |            | 2          | V        |

| A04  | Vt()lo       | Threshold Voltage Io at CFGSPI, INT_NMOT, NCS, ALE, NRD_RNW, NWR_E, DB70         |                                                                           | 0.8        |            |            | V        |

| A05  | Vt()hys      | Threshold Voltage Hysteresis at CFGSPI, INT_NMOT, NCS, ALE, NRD_RNW, NWR_E, DB70 |                                                                           | 150        | 250        |            | mV       |

| A06  | lpd()        | Pull-Down Current at CFGSPI, INT_NMOT, ALE, DB70                                 | VDD = 4.5 V, V() = 1 V V(VDD)<br>VDD = 3 V, V() = 1 V V(VDD)              | 6<br>3     | 30<br>30   | 60<br>60   | μA<br>μA |

| A07  | lpu()        | Pull-Up Current at NCS,<br>NRD_RNW, NWR_E                                        | VDD = 4.5 V, V() = 0 V V(VDD) - 1 V<br>VDD = 3 V, V() = 0 V V(VDD) - 1 V  | -60<br>-60 | -30<br>-30 | -6<br>-3   | μA<br>μA |

|      | Rpu()        | Pull-up Resistor at SL1,<br>SL2_NSL1                                             |                                                                           |            | 50         |            | kΩ       |

| BiSS | nterface: T  | TL/CMOS Mode (CFGIF = 00 or 01                                                   |                                                                           |            |            |            |          |

| B02  | Vs()hi       | Saturation Voltage hi at MA1,<br>MO1, MA2_NMA1, MO2_NMO2                         | V() = V(VDD) - V();<br>VDD = 4.5 V, I() = -4 mA<br>VDD = 3 V, I() = -2 mA |            |            | 0.4<br>0.4 | V        |

| B03  | Vs()lo       | Saturation Voltage lo at MA1, MO1, MA2_NMA1, MO2_NMO2                            | VDD = 4.5 V, I() = 4 mA<br>VDD = 3 V, I() = 2 mA                          |            |            | 0.4<br>0.4 | V        |

| BiSS | Interface: T | TL Mode (CFGIF = 00)                                                             |                                                                           |            |            |            |          |

| B04  | Vt()hi       | Threshold Voltage hi at SL, SL2_NSL1                                             |                                                                           |            |            | 2          | V        |

| B05  | Vt()lo       | Threshold Voltage lo at SL, SL2_NSL1                                             |                                                                           | 0.8        |            |            | V        |

| B06  | Vt()hys      | Hysteresis at at SL, SL2_NSL1                                                    |                                                                           | 150        | 300        |            | mV       |

|      | 1            | MOS Mode (CFGIF = 01)                                                            |                                                                           |            | ,          | r          |          |

| B07  | Vt()hi       | Threshold Voltage hi at SL, SL2_NSL1                                             |                                                                           |            | 62         | 70         | %VDD     |

| B08  | Vt()lo       | Threshold Voltage lo at SL, SL2_NSL1                                             |                                                                           | 33         | 39         |            | %VDD     |

| B09  | Vt()hys      | Hysteresis at at SL, SL2_NSL1                                                    |                                                                           | 0.7        | 1.13       |            | V        |

| BiSS | Interface: R | <b>S422 Mode</b> (CFGIF = 10, VDD = 4.                                           |                                                                           |            |            |            |          |

| B10  | Vs()hi       | Saturation Voltage hi at MA1, MO1, MA2_NMA1, MO2_NMO2                            | V() = V(VDD) - V(); I() = -50 mA                                          |            |            | 1.2        | V        |

| B11  | Vs()lo       | Saturation Voltage lo at MA1, MO1, MA2_NMA1, MO2_NMO2                            | I() = 50 mA                                                               |            |            | 1.2        | V        |

| B12  | Vcom()       | Input Voltage Range at SL, SL2_NSL1                                              |                                                                           | 0          |            | 3          | V        |

Rev B2, Page 9/40

## **ELECTRICAL CHARACTERISTICS**

Operating Conditions: VDD = 3.0 V...5.5 V, Tj =  $-40...125 \,^{\circ}\text{C}$ , unless otherwise stated

| Item<br>No. | Symbol        | Parameter                                                     | Conditions                                                                | Min.         | Тур.        | Max.           | Unit       |

|-------------|---------------|---------------------------------------------------------------|---------------------------------------------------------------------------|--------------|-------------|----------------|------------|

| B13         | Vtdiff()      | Threshold Voltage at SL - SL2_NSL1                            | V()=V(P) - V(N)                                                           | -300         |             | 300            | mV         |

| B14         | Vthys()       | Hysteresis Voltage at SL - SL2_NSL1                           | V()=V(P) - V(N)                                                           | 75           | 150         |                | mV         |

| BiSS        | Interface: L\ | /DS Mode (CFGIF = 11)                                         | ,                                                                         | "            |             |                |            |

| B15         | Vs()hi        | Output Voltage hi at MA1, MO1, MA2_NMA1, MO2_NMO2             | RL = 100 Ω<br>VDD = 4.5 V 5.5 V<br>VDD = 3.0 V 3.6 V                      | 1.25<br>1.0  |             | 1.6<br>1.6     | V          |

| B16         | Vs()lo        | Output Voltage lo at MA1, MO1,<br>MA2_NMA1, MO2_NMO2          | RL = 100 Ω<br>VDD = 4.5 V 5.5 V<br>VDD = 3.0 V 3.6 V                      | 0.9<br>0.7   |             | 1.125<br>1.125 | V          |

| B17         | Vadiff        | Differential Output Voltage at MA1 - MA2_NMA1, MO1 - MO2_NMO2 | RL = 100 Ω<br>VDD = 4.5 V 5.5 V<br>VDD = 3.0 V 3.6 V                      | 250<br>220   | 350<br>350  | 450<br>450     | mV<br>mV   |

| B18         | Vacm          | Common Mode Output Voltage lo at MA1, MO1, MA2_NMA1, MO2_NMO2 | RL = 100 Ω<br>VDD = 4.5 V 5.5 V<br>VDD = 3.0 V 3.6 V                      | 1.125<br>0.9 | 1.2<br>1.15 | 1.375<br>1.375 | V          |

| B19         | Vcom()        | Input Voltage Range at SL,<br>SL2_NSL1                        | VDD = 4.5 V 5.5 V<br>VDD = 3.0 V 3.6 V                                    | 0.8<br>0.8   |             | 3<br>1.8       | V          |

| B20         | Vtdiff()      | Threshold Voltage at SL - SL2_NSL1                            | V()=V(P) - V(N)                                                           | -150         |             | 150            | mV         |

| B21         | Vthys()       | Hysteresis Voltage at<br>SL - SL2_NSL1                        | V()=V(P) - V(N)<br>VDD = 4.5 V 5.5 V<br>VDD = 3.0 V 3.6 V                 | 25<br>14     | 70<br>40    |                | mV<br>mV   |

| Ports:      | EOT, NER,     | GETSENS                                                       |                                                                           |              |             |                |            |

| C01         | Vs()hi        | Saturation Voltage hi at EOT                                  | Vs()hi = VDD - V();<br>VDD = 4.5 V, I() = -4 mA<br>VDD = 3 V; I() = -2 mA |              |             | 0.4<br>0.4     | V          |

| C02         | Vs()lo        | Saturation Voltage lo at EOT, NER                             | VDD = 4.5 V, I() = 4 mA<br>VDD = 3 V, I() = 2 mA                          |              |             | 0.4<br>0.4     | V          |

| C03         | Vt()hi        | Threshold Voltage hi at NER, GETSENS                          |                                                                           |              |             | 2              | V          |

| C04         | Vt()Io        | Threshold Voltage lo at NER, GETSENS                          |                                                                           | 0.8          |             |                | V          |

| C05         | Vt()hys       | Threshold Voltage Hysteresis at NER, GETSENS                  |                                                                           | 150          | 250         |                | mV         |

| C06         | lpd()         | Pull-Down Current at GETSENS                                  | VDD = 4.5 V, V() = 1 V V(VDD)<br>VDD = 3 V, V() = 1 V V(VDD)              | 6 3          | 30<br>30    | 60<br>60       | μA<br>μA   |

|             | lpu()         | Pull-Up Current at NER                                        | V() = 0 V V(VDD) - 1 V                                                    | -950         | -300        | -35            | μA         |

| Oscill      | ator: CLK     |                                                               |                                                                           |              |             |                |            |

| D01         | f(CLK)        | Permissible Clock Rate at CLK                                 |                                                                           |              | 20          | 25             | MHz        |

| D02         | f(CLKI)       | Oscillator Clock Frequency                                    | VDD = 4.5 V 5.5 V<br>VDD = 3.0 V 3.6 V                                    | 15<br>10     | 20<br>15    | 25<br>22       | MHz<br>MHz |

| D03         | Vt(CLK)hi     | Threshold Voltage hi                                          |                                                                           |              |             | 2              | V          |

| D04         | Vt(CLK)lo     | Threshold Voltage lo                                          |                                                                           | 0.4          |             |                | V          |

| D05         | Vt(CLK)hys    | • •                                                           |                                                                           | 300          | 500         |                | mV         |

| D06         | lpd()         | Pull-Down Current at CLK                                      | VDD = 4.5 V, V() = 1.5 V VDD<br>VDD = 3 V, V() = 1.5 V VDD                | 6 3          | 30<br>30    | 60<br>60       | μA<br>μA   |

Rev B2, Page 10/40

## **ELECTRICAL CHARACTERISTICS**

Operating Conditions: VDD = 3.0 V...5.5 V, Tj = -40...125 °C, unless otherwise stated

| ltem  | Symbol  | Parameter                     | Conditions              |      |      |      | Unit |

|-------|---------|-------------------------------|-------------------------|------|------|------|------|

| No.   | -       |                               |                         | Min. | Тур. | Max. |      |

| Reset | NRES    |                               |                         |      |      |      |      |

| E01   | VDDoff  | Undervoltage Reset            | VDD decreasing          | 1.4  |      | 2.6  | V    |

| E02   | VDDon   | Undervoltage Release          | VDD increasing          | 1.6  |      | 2.8  | V    |

| E03   | VDDhys  | Undervoltage Hysteresis       | VDDhys = VDDon - VDDoff | 200  |      |      | mV   |

| E04   | Vt()hi  | Threshold Voltage hi          |                         |      |      | 2    | V    |

| E05   | Vt()lo  | Threshold Voltage lo          |                         | 0.4  |      |      | V    |

| E06   | Vt()hys | Threshold Voltage Hysteresis  |                         | 300  | 500  |      | mV   |

| E07   | lpd()   | Pull-Down Current             | V() = 1.5 V VDD         | 4    | 35   | 70   | μA   |

| E08   | td()res | Required Reset Pulse Duration | At NRES                 | 250  |      |      | ns   |

Rev B2, Page 11/40

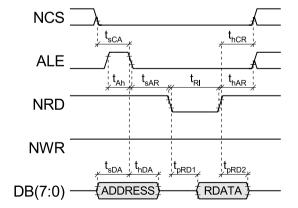

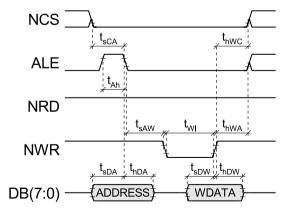

## OPERATING REQUIREMENTS: µC Interface, INTEL mode

Operating conditions: CFGSPI = 0, INT\_NMOT = 1, VDD =  $3.0 \dots 5.5$  V, Tj =  $-40 \dots 125$  °C lo input level =  $0 \dots 0.8$  V, hi input level = 2.0 V ... VDD, lo output level =  $0 \dots 0.4$  V, hi output level = 2.4 V ... VDD Alias: NRD = NRD\_RNW, NWR = NWR\_E

| ltem<br>No. | Symbol | Parameter                                                        | Conditions           | Min. | Max. | Unit |

|-------------|--------|------------------------------------------------------------------|----------------------|------|------|------|

| 1001        | tsCA   | Setup Time:<br>NCS lo before ALE hi→lo                           |                      | 10   |      | ns   |

| 1002        | tsDA   | Setup Time:<br>Data stable before ALE hi→lo                      |                      | 15   |      | ns   |

| 1003        | thDA   | Hold Time:<br>Data stable after ALE hi→lo                        |                      | 15   |      | ns   |

| 1004        | tAh    | Signal Duration:<br>ALE at high level                            |                      | 10   |      | ns   |

| 1005        | tsAR   | Setup Time:<br>ALE lo before NRD hi→lo                           |                      | 10   |      | ns   |

| 1006        | thAR   | Hold Time:<br>ALE lo after NRD lo→hi                             | NCS = Io             | 10   |      | ns   |

| 1007        | tRI    | Signal Duration:<br>NRD at low level                             | NCS = Io             | 10   |      | ns   |

| 1008        | tpRD1  | Propagation Delay:<br>Data stable after NRD hi→lo                | NCS = Io, CL = 50 pF |      | 25   | ns   |

| 1009        | tpRD2  | Propagation Delay:<br>Data bus high impedance after NRD<br>lo→hi | NCS = Io, CL = 50 pF |      | 25   | ns   |

| 1010        | thCR   | Hold Time:<br>NCS lo after NRD lo→hi                             |                      | 10   |      | ns   |

| 1011        | tsAW   | Setup Time:<br>ALE lo before NWR hi→lo                           |                      | 10   |      | ns   |

| 1012        | thAW   | Hold Time:<br>ALE lo after NWR lo→hi                             | NCS = Io             | 10   |      | ns   |

| 1013        | tWI    | Signal Duration:<br>NWR at low level                             | NCS = Io             | 10   |      | ns   |

| 1014        | tsDW   | Setup Time:<br>Data stable before NWR lo→hi                      | NCS = Io             | 15   |      | ns   |

| 1015        | thDW   | Hold Time:<br>Data stable after NWR lo→hi                        | NCS = Io             | 15   |      | ns   |

| 1016        | thCW   | Hold Time:<br>NCS lo after NWR lo→hi                             |                      | 10   |      | ns   |

Figure 3: Read cycle (Intel mode)

Figure 4: Write cycle (Intel mode)

Rev B2, Page 12/40

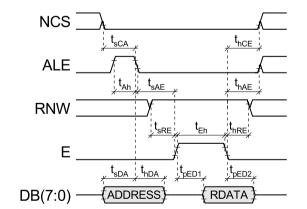

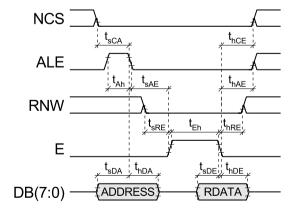

## OPERATING REQUIREMENTS: µC Interface, MOTOROLA mode

Operating conditions: CFGSPI = 0, INT\_NMOT = 0 VDD =  $3.0 \dots 5.5 \text{ V}$ , Tj =  $-40 \dots 125 \,^{\circ}\text{C}$ ; lo input level =  $0 \dots 0.8 \,^{\circ}\text{V}$ , hi input level =  $2.0 \,^{\circ}\text{V} \dots \text{VDD}$ , lo output level =  $0 \dots 0.4 \,^{\circ}\text{V}$ , hi output level =  $2.4 \,^{\circ}\text{V} \dots \text{VDD}$  Alias: RNW = NRD\_RNW, E = NWR\_E

| Item | Symbol | Parameter                                                   | Conditions           |      |      | Unit |

|------|--------|-------------------------------------------------------------|----------------------|------|------|------|

| No.  |        |                                                             |                      | Min. | Max. |      |

| l101 | tsCA   | Setup Time:<br>NCS lo before ALE hi→lo                      |                      | 10   |      | ns   |

| I102 | tsDA   | Setup Time:<br>Data stable before ALE hi→lo                 |                      | 15   |      | ns   |

| 1103 | thDA   | Hold Time:<br>Data stable after ALE hi→lo                   |                      | 15   |      | ns   |

| l104 | tAh    | Signal Duration:<br>ALE at high level                       |                      | 10   |      | ns   |

| l105 | tsAE   | Setup Time:<br>ALE lo before E lo→hi                        |                      | 10   |      | ns   |

| I106 | thAE   | Hold Time:<br>ALE lo after E hi→lo                          | NCS = Io             | 10   |      | ns   |

| l107 | tsRE   | Setup Time:<br>RNW stable before E lo→hi                    | NCS = Io             | 10   |      | ns   |

| l108 | thRE   | Hold Time:<br>RNW stable after E hi→lo                      | NCS = Io             | 10   |      | ns   |

| l109 | tEh    | Signal Duration:<br>E at high level                         | NCS = Io             | 10   |      | ns   |

| I110 | tpED1  | Propagation Delay:<br>Data stable after E lo→hi             | NCS = Io, CL = 50 pF |      | 25   | ns   |

| I111 | tpED2  | Propagation Delay:<br>Data bus high impedance after E hi→lo | NCS = Io, CL = 50 pF |      | 25   | ns   |

| I112 | tsDE   | Setup Time:<br>Data stable before E hi→lo                   | NCS = Io             | 15   |      | ns   |

| I113 | thDE   | Hold Time:<br>Data stable after E hi→lo                     | NCS = Io             | 15   |      | ns   |

| I114 | thCE   | Hold Time:<br>NCS lo after E hi→lo                          |                      | 10   |      | ns   |

Figure 5: Read cycle (Motorola mode)

Figure 6: Write cycle (Motorola mode)

Rev B2, Page 13/40

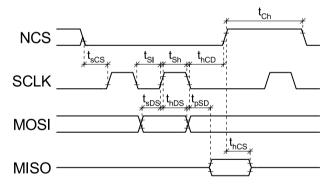

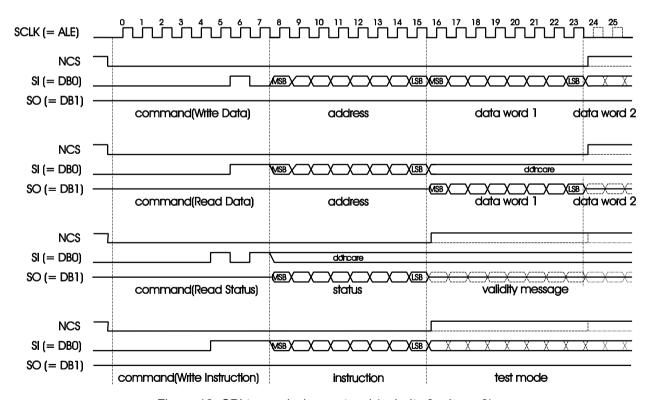

## OPERATING REQUIREMENTS: µC Interface, SPI mode

Operating conditions: CFGSPI = 1 VDD = 3.0...5.5 V, Tj = -40...125 °C; lo input level = 0...0.8 V, hi input level = 2.0 V ... VDD, lo output level = 0...0.4 V, hi output level = 2.4 V ... VDD Alias: NCS = NCS/DB4, SCLK = ALE/DB5, MOSI = DB0/DB6, MISO = DB1/DB7

| Item | Symbol | Parameter                                                 | Conditions                                         |      |      | Unit |

|------|--------|-----------------------------------------------------------|----------------------------------------------------|------|------|------|

| No.  | -      |                                                           |                                                    | Min. | Max. |      |

| 1201 | tsCS   | Setup Time:<br>NCS lo before SCLK lo→hi                   |                                                    | 10   |      | ns   |

| 1202 | thCS   | Hold Time:<br>NCS lo after SCLK hi→lo                     |                                                    | 10   |      | ns   |

| 1203 | tSI    | Signal Duration:<br>SCLK lo                               |                                                    | 10   |      | ns   |

| 1204 | tSh    | Signal Duration:<br>SCLK hi                               |                                                    | 10   |      | ns   |

|      |        |                                                           | during command 'ReadData' between address and data | 100  |      | ns   |

| 1205 | tsDS   | Setup Time:<br>MOSI stable before SCLK lo→hi              |                                                    | 7.5  |      | ns   |

| 1206 | thDS   | Hold Time:<br>MOSI stable after SCLK lo→hi                |                                                    | 7.5  |      | ns   |

| 1207 | tpSD   | Propagation Delay:<br>MISO stable after SCLK hi→lo        | CL = 50 pF                                         |      | 25   | ns   |

| 1208 | tpCD   | Propagation Delay:<br>MISO high impedance after NCS lo→hi | CL = 50 pF                                         |      | 25   | ns   |

| 1209 | tCh    | Signal Duration:<br>NCS hi                                |                                                    | 10   |      | ns   |

Figure 7: Read/write access (SPI mode)

Rev B2, Page 14/40

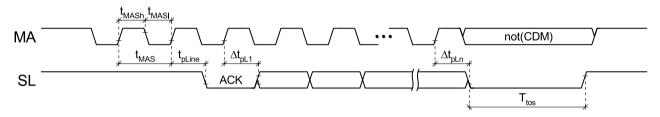

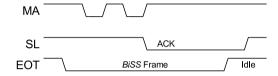

## **OPERATING REQUIREMENTS: BISS Interface - BISS Frame**

Operating conditions: register bit SELSSI = 0 VDD = 3.0  $\dots$  5.5 V, Tj = -40  $\dots$  125 °C Alias: MA = MA1/MA2\_NMA1, SL = SL1/SL2\_NSL1

| Item   | Symbol    | Parameter                                                                          | Conditions                                                             |      |            | Unit      |

|--------|-----------|------------------------------------------------------------------------------------|------------------------------------------------------------------------|------|------------|-----------|

| No.    |           |                                                                                    |                                                                        | Min. | Max.       |           |

| Sensor | Data Cycl | e                                                                                  |                                                                        |      |            |           |

| I301   | TMAS      | Clock Period                                                                       | FreqSens via FREQ(4:0) selected in accordance with table 45 on page 29 | 2    | 320        | 1/f(CLK)  |

| 1302   | tMASI     | Clock Signal Lo Level Duration                                                     |                                                                        | 50   | 50         | %<br>TMAS |

| 1303   | tMASh     | Clock Signal Hi Level Duration                                                     |                                                                        | 50   | 50         | %<br>TMAS |

| 1304   | tpLine    | Permissible Line Delay                                                             |                                                                        | 0    | indefinite |           |

| 1305   | ∆ tpL     | Permissible Propagation Delay of<br>Subsequent Clock Cycles vs. 1st Clock<br>Cycle | $\Delta$ tpL = max( tpLine - tpLx ); x= 1 n                            |      | 25         | %<br>TMAS |

| 1306   | Ttos      | Permissible Timeout (Slave)                                                        |                                                                        | 55   |            | %<br>TMAS |

Figure 8: Timing diagram BiSS Frame

## SLx line sampling

With BiSS line delays longer than one clock cycle are permissible, with the result that line delays during communication are negligible. The evaluation of the sensor response is delayed until the first falling edge at SLx while the clock signal continues to be output at MAx .

Within one MAx clock cycle four equally distributed sampling instances are available. Following the falling edge at SLx is the slaves acknowledge signal. The SL1 level is evaluated by two sampling instances, close to the center of the transmitted bit.

Rev B2, Page 15/40

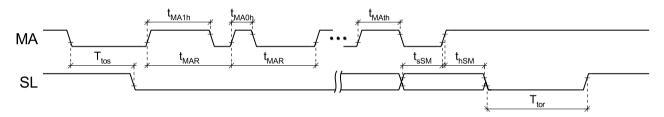

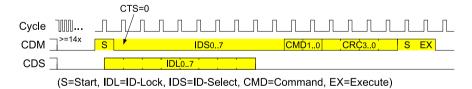

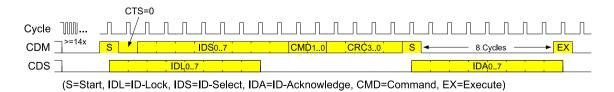

## OPERATING REQUIREMENTS: BiSS Interface - Register Data Cycle (BiSS B)

Operating conditions: register bit SELSSI = 0 VDD = 3.0...5.5 V, Tj = -40...125 °C Alias: MA = MA1/MA2\_NMA1, SL = SL1/SL2\_NSL1

| Item   | Symbol    | Parameter                             | Conditions                                                          |      |      | Unit      |

|--------|-----------|---------------------------------------|---------------------------------------------------------------------|------|------|-----------|

| No.    |           |                                       |                                                                     | Min. | Max. |           |

| Your c | opied row | s:                                    |                                                                     |      |      |           |

| I401   | TMAR      | Clock Period                          | FreqReg via FREQ(7:5) selected in accordance with table on page XXX | 2    | 256  | TMAS      |

| 1402   | tMA0h     | "Logic 0" Hi Level Duration           |                                                                     | 25   | 25   | %<br>TMAR |

| I403   | tMA1h     | "Logic 1" Hi Level Duration           |                                                                     | 75   | 75   | %<br>TMAR |

| 1404   | tMAth     | Clock Signal Hi Level Duration        | register data readout                                               | 50   | 50   | %<br>TMAR |

| 1405   | tsSM      | Setup Time: SL stable before MA lo→hi |                                                                     | 30   |      | ns        |

| 1406   | thSM      | Hold Time: SL stable after MA lo→hi   |                                                                     | 0    |      | ns        |

| 1407   | Ttor      | Permissible Timeout (Slave)           |                                                                     | 80   |      | %<br>TMAR |

Figure 9: Timing diagram BiSS B register access

Rev B2, Page 16/40

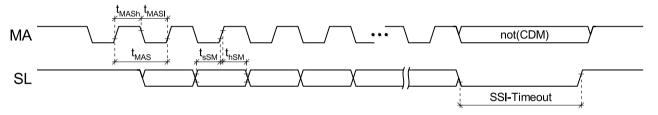

## **OPERATING REQUIREMENTS: BISS Interface (SSI mode)**

Operating conditions: register bit SELSSI = 1; VDD = 3. . . 5.5 V, Tj = -40 . . . 125 °C Alias: MA = MA1/MA2\_NMA1, SL = SL1/SL2\_NSL1

| Item | Symbol | Parameter                             | Conditions                                                             |      |      | Unit      |

|------|--------|---------------------------------------|------------------------------------------------------------------------|------|------|-----------|

| No.  |        |                                       |                                                                        | Min. | Max. |           |

| 1501 | TMAS   | Clock Period                          | FreqSens via FREQ(4:0) selected in accordance with table 45 on page 29 | 2    | 320  | 1/f(CLK)  |

| 1502 | tMASh  | Clock Signal Hi Level Duration        |                                                                        | 50   | 50   | %<br>TMAS |

| 1503 | tMASI  | Clock Signal Lo Level Duration        |                                                                        | 50   | 50   | %<br>TMAS |

| 1504 | tsDC   | Setup Time: SL stable before MA lo→hi |                                                                        | 30   |      | ns        |

| 1505 | thDC   | Hold Time: SL stable after MA lo→hi   |                                                                        | 0    |      | ns        |

Figure 10: Timing diagram SSI mode

## SLx line sampling

In SSI interface mode SL1 values are sampled with the rising edge at MA1. An overall delay of the sensor response to the clock at MA1, caused by process times in the sensor or transmission times, is permissible up to the length of one clock cycle.

## iC-MB4

## **BISS INTERFACE MASTER**

Rev B2, Page 17/40

## **PROGRAMMING**

MOBUSY:

Delay of start bit at output MOx

| Register Layo        | ut, Overview Page 18                     | <b>Channel Conf</b> | iguration Page 32                             |

|----------------------|------------------------------------------|---------------------|-----------------------------------------------|

|                      |                                          | SLAVELOC:           | Slave location                                |

|                      |                                          | CHCFGx:             | Channel configuration                         |

| Sensor Data .        | Page 24                                  | ACTnSENS:           | Sensor or actuator data selector              |

| SCDATAx:             | Single cycle data (SCD)                  |                     |                                               |

|                      | (sensor resp. actuator data, 64 bit per  | Status Informa      | ation Page 35                                 |

|                      | slave, 2 banks)                          | EOT:                | Data transmission completed                   |

|                      |                                          | nERR:               | Error at NER pin                              |

| <b>Register Data</b> | Page 26                                  | REGEND:             | Register data transmission completed          |

| RDATAx:              | Register data (64 byte)                  | nREGERR:            | Error in register data transmission           |

|                      | riogisto: asia (o r syto)                | nSCDERR:            | Error in single cycle data transmission       |

| Slave Configu        | ration Page 32                           | nDELAYERR:          | Missing start bit during register com-        |

| SCDLENx:             | Single cycle data length                 |                     | munication                                    |

| ENSCDx:              | Enable single cycle data                 | nAGSERR:            | Unable to start SCD frame                     |

| GRAYSx:              | Enable SCD gray to binary conversion     | SVALIDx:            | Single cycle data valid                       |

| Or trox.             | (SSI only)                               | REGBYTES:           | Number of valid register data transmit-       |

| SCRCPOLYx.           | Polynomial for SCD CRC check             |                     | ted in case of error                          |

| SCRCLENx:            | Polynomial selection by length for SCD   | CDSSEL:             | Register bit of data transmission (se-        |

|                      | CRC check                                |                     | lected channel)                               |

| SELCRCSx:            | Selection between polynomial or          | CDMTIME-            | Control data timeout met                      |

|                      | length for SCD CRC polynomial            | OUT:                |                                               |

| SCRCSTARTX:          | Start value for polynomial SCD CRC       |                     |                                               |

|                      | calculation                              | Instruction Re      | egister Page 28                               |

|                      |                                          | INSTR:              | Instruction                                   |

| <b>Control Comm</b>  | nunication Configuration Page 26         | AGS:                | AutoGetSens                                   |

| REGADR:              | Register address                         | INIT:               | Initialize                                    |

| WNR:                 | Read/write selector                      | SWBANK:             | Switch RAM banks                              |

| REGNUM:              | Register data count                      | HOLDBANK:           | Inhibit RAM bank switching                    |

| CHSEL:               | Channel selector                         | BREAK:              | Data transmission interrupt                   |

| SLAVEID:             | Slave selector                           | CLKENI:             | Enable internal clock                         |

| REGVERS:             | BiSS model A/B or C selector             | ENTEST:             | Enable test interface                         |

| CTS:                 | Register transmission or instruction se- | CFGIF:              | Configure physical interfaces                 |

|                      | lector                                   | MAFS:               | Master line control (selected channel)        |

| HOLDCDM:             | Hold CDM (control data master)           | MAVS:               | Master line control (selected channel)        |

| EN_MO:               | Enable output at MOx for actuator data   | MAFO:               | Master line control (deselected chan-         |

|                      | or delayed start bit                     | MAVO:               | nel)                                          |

|                      |                                          | MAVO.               | Master line control (deselected chan-<br>nel) |

| _                    | uration Page 29                          |                     | riei)                                         |

| FREQS:               | Frequency division                       | Status Informa      | ation 2 Page 36                               |

| FREQR:               | Frequency division register communi-     |                     | <u>•</u>                                      |

|                      | cation BiSS B                            | SLx:                | Current SL line level                         |

| FRGAGS:              | AutoGetSens Frequency division           | CDSx:               | Control data bit slave                        |

| REVISION:            | Revision                                 | SWBANK-             | Bank switching for single cycle data          |

| VERSION:             | Device identifier                        | FAILS:              | failed                                        |

|                      | Use of only one RAM bank for SCD         |                     |                                               |

| NOCRC:               | CRC for SCD not to be stored in RAM      |                     |                                               |

Rev B2, Page 18/40

## **REGISTER LAYOUT, OVERVIEW**

| OVERV             | 'IEW                                                    |                             |       |               |                 |            |       |          |  |

|-------------------|---------------------------------------------------------|-----------------------------|-------|---------------|-----------------|------------|-------|----------|--|

| Addr              | Bit 7                                                   | Bit 6                       | Bit 5 | Bit 4         | Bit 3           | Bit 2      | Bit 1 | Bit 0    |  |

| Sensor            | and Actuator Data                                       |                             |       |               |                 |            |       |          |  |

| 0x00              | SCDATA1(7:0)                                            |                             |       |               |                 |            |       |          |  |

| 0x01<br>0x07      |                                                         | SCDATA1(63:8)               |       |               |                 |            |       |          |  |

| 0x08<br>0x3F      |                                                         | SCDATA2(63:0) SCDATA8(63:0) |       |               |                 |            |       |          |  |

| 0x40<br>0x7F      |                                                         | _*                          |       |               |                 |            |       |          |  |

| Registe           | r Data                                                  |                             |       |               |                 |            |       |          |  |

| 0x80 <sup>†</sup> |                                                         |                             |       | RDATA         | A1(7:0)         |            |       |          |  |

| 0x80 <sup>‡</sup> |                                                         |                             |       | IDS           | (7:0)           |            |       |          |  |

| 0x81<br>0xBF      |                                                         |                             |       | RDATA2(7:0) . | . RDATA64(7:0)  |            |       |          |  |

| Configu           | ration Slave                                            | 1                           |       |               |                 |            |       |          |  |

| 0xC0              | GRAYS1 /<br>LSTOP1                                      | ENSCD1                      |       |               | SCDLE           | EN1(5:0)   |       |          |  |

| 0xC1              | SELCRCS1                                                |                             |       | SCRCLEN       | N1(6:0) / SCRCF | POLY1(7:1) |       |          |  |

| 0xC2              |                                                         |                             |       | SCRCST        | ART1(7:0)       |            |       |          |  |

| 0xC3              |                                                         |                             |       | SCRCSTA       | ART1(15:8)      |            |       |          |  |

| 0xC4<br>0xDF      | Configuration Slave 2(31:0) Configuration Slave 8(31:0) |                             |       |               |                 |            |       |          |  |

| Control           | Communicat                                              | ion Configura               | tion  |               |                 |            |       |          |  |

| 0xE0              | _*                                                      |                             |       |               |                 |            |       |          |  |

| 0xE1              | -*                                                      |                             |       |               |                 |            |       |          |  |

| 0xE2              | WNR REGADR(6:0)                                         |                             |       |               |                 |            |       |          |  |

| 0xE3              | _* REGNUM(5:0)                                          |                             |       |               |                 |            |       |          |  |

| 0xE4              |                                                         |                             | _     | . *           |                 |            | CHS   | SEL(2:1) |  |

| 0xE5 †            | CTS                                                     | REGVERS                     |       | SLAVEID(2:0)  |                 | -*         | EN_MO | HOLDCDM  |  |

| 0xE5 ‡            | CTS                                                     | REGVERS                     | CME   | 0(1:0)        | IDA_TEST        | - *        | EN_MO | HOLDCDM  |  |

| Master (          | Configuration                                           | 1                           |       |               |                 |            |       |          |  |

| 0xE6              | FREQR(2:0) FREQS(4:0)                                   |                             |       |               |                 |            |       |          |  |

| 0xE7              | -* NOCRC SINGLEBANK                                     |                             |       |               |                 |            |       |          |  |

| 0xE8              | FREQAGS(7:0)                                            |                             |       |               |                 |            |       |          |  |

| 0xE9              | MO_BUSY(7:0)                                            |                             |       |               |                 |            |       |          |  |

| 0xEA              |                                                         | REVISION(7:0) <sup>§</sup>  |       |               |                 |            |       |          |  |

| 0xEB              |                                                         | VERSION(7:0) <sup>§</sup>   |       |               |                 |            |       |          |  |

| Channe            | l Configuration                                         | on                          |       |               |                 |            |       |          |  |

| 0xEC              | '0'                                                     | '0'                         | '0'   | SLAVELOC5     | '0'             | '0'        | '0'   | '1'      |  |

| 0xED              |                                                         | -* CFGCH2(1:0) CFGCH1(1:0)  |       |               |                 |            |       |          |  |

| 0xEE              |                                                         | _*                          |       |               |                 |            |       |          |  |

<sup>\*</sup> Reserved or unused register bits highlighted as "-" need to be written with 0 if a byte wide register write access is required.

† Using register access in control communication.

<sup>&</sup>lt;sup>‡</sup> Using command/instructions in control communication. § Register bits with constant "0" or "1" are ROM-based values and can not be changed through writing.

Rev B2, Page 19/40

| OVERV        | OVERVIEW             |          |               |         |                   |        |         |                  |

|--------------|----------------------|----------|---------------|---------|-------------------|--------|---------|------------------|

| Addr         | Bit 7                | Bit 6    | Bit 5         | Bit 4   | Bit 3             | Bit 2  | Bit 1   | Bit 0            |

|              |                      |          |               |         |                   |        |         | Dit 0            |

|              | onfiguration 2       | 2        |               |         |                   |        |         |                  |

| 0xEF         |                      |          |               | ACTnSE  | ENS(8:1)          |        |         |                  |

| Status II    | nformation           |          |               |         |                   |        |         |                  |

| 0xF0         | nERR                 | nAGSERR  | nDELAYERR     | nSCDERR | nREGERR           | REGEND | '1'     | EOT              |

| 0xF1         | SVALID4              | '0'      | SVALID3       | '0'     | SVALID2           | '0'    | SVALID1 | '0'              |

| 0xF2         | SVALID8              | '0'      | SVALID7       | '0'     | SVALID6           | '0'    | SVALID5 | '0'              |

| 0xF3         | CDMTIME-<br>OUT      | CDSSEL   | REGBYTES(5:0) |         |                   |        |         |                  |

| Instructi    | Instruction Register |          |               |         |                   |        |         |                  |

| 0xF4         | BREAK                | HOLDBANK | SWBANK        | INIT    | INSTR(2:0)        |        |         | AGS              |

| 0xF5         | MAVO                 | MAFO     | MAVS          | MAFS    | CFGIF(1:0) ENTEST |        | ENTEST  | CLKENI           |

| 0xF6         | _                    | _        | _             | _       | _                 | _      | _       | _                |

| 0xF7         | _                    | _        | _             | _       | _                 | _      | _       | _                |

| Status II    | nformation 2         |          |               |         |                   |        |         |                  |

| 0xF8         | 0                    | 1        | 0             | 1       | CDS2              | SL2    | CDS1    | SL1              |

| 0xF9         | 0                    | 1        | 0             | 1       | 0                 | 1      | 0       | 1                |

| 0xFA         | _                    | _        | _             | _       | _                 | _      | _       | _                |

| 0xFB         | _                    | _        | _             | _       | _                 | _      | _       | SWBANK-<br>FAILS |

| Reserve      | d                    |          |               |         |                   |        |         |                  |

| 0xFC<br>0xFF | _                    | _        | _             | _       | _                 | _      | _       | _                |

Table 10: Register layout

iC-MB4 does reset all RAM registers to 0 on a power on reset.

Rev B2, Page 20/40

#### **FUNCTIONAL DESCRIPTION**

#### **BiSS C Frame**

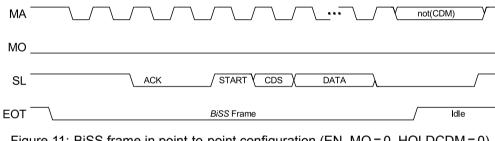

BiSS uses in the point-to-point configuration a clock line (MA) from the master to the slave and a data line (SL) from the slave to the master. A device may contain multiple slaves. The data input (SLI) of the last slave is set to low, the slaves are daisychained (SLO  $\rightarrow$  SLI), and the data output (SLO) of the first slave is directed to the master. A data line from the master to the slave is not mandatory (see figure 1).

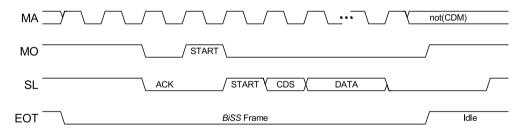

At the end of the cycle the master sends the CDM bit (inverted) on the MA clock line. After detecting the slaves timeout with SLO = 1 the master changes the MA clock line state to high. If the BiSS frame has not been clocked out finally, e.g. for a faster configuration phase and higher control data transmission rates, the HOLDCDM needs to be enabled to keep the clock line constant until the next cycle starts. The difference is explained in figures 11 and 12.

BiSS C provides the additional bus configuration with the data output line (MO) from the master to the slaves. With EN MO = 1 the master emulates a slave without sensor data at the MO line. The parameterized processing time for sensor data (i.e. the "start bit delay") is configured by the MO BUSY parameter.

Figure 11: BiSS frame in point-to-point configuration (EN MO = 0, HOLDCDM = 0)

Figure 12: BiSS frame in bus configuration (EN MO = 1, HOLDCDM = 1)

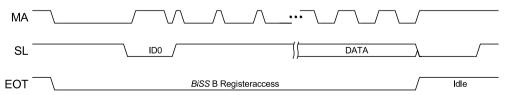

#### **BiSS B Register Communication**

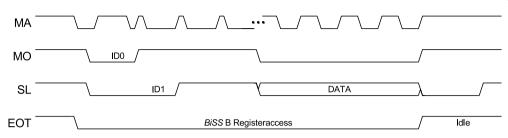

In BiSS B the register communication is started by a timing condition and a handshake at the beginning of the cycle (see figure 13). Alternatively the register com-

munication can be selected at the cycle start with the MO line. With EN MO=1 the slave ID "0" remains unused.

Figure 13: BiSS B register access (EN\_MO = 0)

Rev B2, Page 21/40

Figure 14: BiSS B register access (EN\_MO = 1)

## **Extended SSI BiSS C Register Communication**

With extended SSI the BiSS C register write access is possible to the SSI slave. The master is able to transmit a BiSS C register write access to the slave without the slaves CDS feedback. The master cannot verify if the BiSS C register write access to the slave did succeed or not. At the end of the cycle the master sends the CDM bit inverted on the MA clock line.

#### **BiSS C Init Sequence**

In the init sequence two 0 pulses are generated at MA. The slave should answer with a falling edge and after the BiSS timeout with a rising edge at SL. The gap between the second rising edge at MA and the falling edge at SL is measured as line delay and stored in the single cycle data RAM. The BiSS C init is selected with REGVERS=1 and executed with INIT=1.

Figure 15: BiSS init sequence

With an INIT sequence the iC-MB4 does store the measured channel 1 line delay in the SCDATA1(7:0) and the channel 2 line delay in the SCDATA5(7:0). The unit of this value is the 1/4 of the configured MA clock frequency.

$$t_{\text{Line Delay Channel 1}} = \frac{SCDATA1(7:0)}{4*f_{MA}}$$

$$t_{\text{Line Delay Channel 2}} = \frac{SCDATA5(7:0)}{4*f_{MA}}$$

For the INIT sequence the maximum line delay is 255. On exceeding this limit while INIT the INIT sequence is aborted and an AGSERR is set.

Rev B2, Page 22/40

#### **MICROCONTROLLER INTERFACE**

With pin CFGSPI the microcontroller interface is selected between an 8 bit parallel interface or an SPI serial interface. With pin CFGSPI = 0 the 8 bit parallel microcontroller interface is selected in which the bidirectional data bus alternately transmits addresses and data in blocks of 8 bits (see figures 3). With pin INT\_NMOT = 0 for an Intel 8051 controller or INT\_NMOT = 1 for a 68HC11 Motorola controller communication type is selected.

| CFGSPI | INT_NMOT | Mode            |

|--------|----------|-----------------|

| 0      | 0        | Motorola 68HC11 |

| 0      | 1        | Intel 8051      |

Table 11: Parallel communication modes

| <b>SPI Serial Micro</b> | controller | Interface |

|-------------------------|------------|-----------|

|-------------------------|------------|-----------|

With pin CFGSPI = 1 the SPI serial microcontroller interface is selected.

| CFGSPI | INT_NMOT | Mode                           |

|--------|----------|--------------------------------|

| 1      | -        | SPI1 (polarity = 0, phase = 0) |

Table 12: SPI communication modes

When operated in conjunction with an SPI controller, pin ALE is used as a clock input (SCK) and pin NCS as an enable input (NCS), with DB0 as the data input (SI) and DB1 as the data output (SO). Data is transmitted serially in successive blocks of 8 bits (command, address and data). Six commands are available:

- WriteData (0x02 = 0b0000 0010)

- ReadData (0x03 = 0b0000 0011)

- ReadStatus (0x05 = 0b0000 0101)

- WriteInstruction (0x07 = 0b0000 0111)

- ReadData0 (0x09 = 0b0000 1001)

- WriteData0 (0x0B = 0b0000 1011)

Figure 16: SPI transmission protocol (polarity 0, phase 0)

## iC-MB4

## **BISS INTERFACE MASTER**

Rev B2, Page 23/40

The first two commands can be used to write data to or read data from iC-MB4's registers. The latter commands are shortend write commands and read commands with a set start address. In the read data command a delay between the address and the first data is necessary.

For fast access use the SPI commands "ReadStatus", "WriteInstruction" and "ReadData0".

- ReadStatus to read the status register in 0xF0

- WriteInstruction to write the instruction register in 0xF4

- ReadData0 to read SDATA register starting at 0x00

This means that it is not necessary to give an address, with the data directly adhering to the command. With all commands it is possible to transmit several bytes of data consecutively if the NCS signal is not reset and ALE/SCK continues to be clocked. The address transmitted (240 for ReadStatus and 244 for WriteInstruction) is then the start address which is internally increased by 1 following each transmitted byte.

Additional 2nd SPI Serial Microcontroller Interface With the active SPI serial microcontroller interface an additional SPI interface can be addressed for dedicated register access and reduced function set.

| CFGSPI | NWR_E | Mode                                     |

|--------|-------|------------------------------------------|

| 1      | 0     | SPI2, optional (polarity = 0, phase = 0) |

Table 13: SPI communication modes

An additional SPI interface at DB4 ... DB7 is available for exclusive read access to the SCD single cycle data RAM of the slaves 5 to 8. The 2nd SPI interface is enabled with NWR\_E = 0. Access to status, instruction and parameter register is not possible.

The 2. SPI does only provide the SPI command "Read-Data" with a limited address range of 0x40 ... 0x7F.

• ReadData (0x03 = 0b0000 0011)

The 2nd SPI can neither be used to configure nor to read status.

This 2nd SPI can only be used to read SCDATA from 0x40 ... 0x7F.

Rev B2, Page 24/40

#### **SENSOR DATA**

The transmission of sensor data begins when the master outputs the clock signal at pin MA1 with the clock frequency selected by FREQ. The line delay, i.e. the transmission propagation until an acknowledgement is generated at SL1, is determined from the second falling edge onwards. While the clock continues to be output at MA1, the master waits for the slaves start bit (1) signaling the start of data transmission. Afterwards this the actual clocking out of sensor data begins, i.e. the sensors place a new bit on the SL1 line with each rising edge on the MA1 line.

The sensor data being input into the master and the subsequent sets of CRC data are written to the appropriate sensor data RAM. At the same time the new CRC value is calculated in accordance with the CRC polynomial stored in the configuration RAM. Should the system ascertain after entry of the last CRC bit, that transmission was faulty, the relevant validity message is deleted and error message nSENSERR set in the status register. At the same time the sensor data RAM banks are swapped.

In order for new sensor data to be read in during controller accesses, iC-MB4 has dual memory banks for sensor data. While sensor data is being read and written into the first RAM bank, the second RAM bank section with the prior read sensor data can be read out by the controller. The relevant sensor data memory banks are swapped at the end of the reading procedure. This can be prevented by the controller entering the command register bit HOLDBANK. Simultaneously the status information 1 (validity register in address 0xF1 ... 0xF2) and status information 2 (CDS2 and CDS1 in address 0xF8) are also swapped.

## Arrangement of Sensor Data in the RAM

The sensor data memory bank has 8 bytes of memory for each slave which can be interpreted as 64 bits of memory in the array 0bxxxx.x111 to 0bxxxx.x000. The sensor data is written to memory area [SDLEN - 1:0] with SDLEN marking the length of the relevant data. If there is space in the available memory for the processed CRC bits and NOCRC = 0, the read CRC bits are stored with the above data at positions [63:63 - (CRCLEN-1)].

| SCDATA       | Addr. 0x00 0x3F;<br>7:0 | bit | R/W |

|--------------|-------------------------|-----|-----|

| 0x00         | SCDATA1(7:0)            |     |     |

| 0x01         | SCDATA1(15:8)           |     |     |

| 0x02         | SCDATA1(23:16)          |     |     |

| 0x03         | SCDATA1(31:24)          |     |     |

| 0x04         | SCDATA1(39:32)          |     |     |

| 0x05         | SCDATA1(47:40)          |     |     |

| 0x06         | SCDATA1(55:48)          |     |     |

| 0x07         | SCDATA1(63:56)          |     |     |

| 0x08<br>0x0F | SCDATA2(63:0)           |     |     |

| 0x10<br>0x17 | SCDATA3(63:0)           |     |     |

| 0x18<br>0x1F | SCDATA4(63:0)           |     |     |

| 0x20<br>0x27 | SCDATA5(63:0)           |     |     |

| 0x28<br>0x2F | SCDATA6(63:0)           |     |     |

| 0x30<br>0x37 | SCDATA7(63:0)           |     |     |

| 0x38<br>0x3F | SCDATA8(63:0)           |     |     |

Table 14: Address mapping of sensor data

## iC-MB4

## **BISS INTERFACE MASTER**

Rev B2, Page 25/40

## **Example: BiSS Sensor Bus with 3 Slaves**

The following example indicates the sensor data position and content in the sensor data of three slaves.

Slave 1: 19+2 bits of sensor data, 6 bits of CRC => total length of 27 bits

Slave 2: 12+2 bits of sensor data, 6 bits of CRC => total length of 20 bits

Slave 3: 13+2 bits of sensor data, 6 bits of CRC => total length of 21 bits

| A al al a | Contont                                       |

|-----------|-----------------------------------------------|

| Addr.     | Content                                       |

| 0x000x07  | Sensor data 1(63:0)                           |

| 0x00      | Sensor data 1(7:0)                            |

| 0x01      | Sensor data 1(15:8)                           |

| 0x02      | Sensor data 1(20:16) in bit 4:0               |

| 0x03      | not changed                                   |

| 0x04      | not changed                                   |

| 0x05      | not changed                                   |

| 0x06      | not changed                                   |

| 0x07      | Received CRC of sensor data 1(5:0) in bit 7:2 |

| 0x08 0x0F | Sensor data 2(63:0)                           |

| 0x08      | Sensor data 2(7:0)                            |

| 0x09      | Sensor data 2(13:8) in bit 5:0                |

| 0x0A      | not changed                                   |

| 0x0B      | not changed                                   |

| 0x0C      | not changed                                   |

| 0x0D      | not changed                                   |

| 0x0E      | not changed                                   |

| 0x0F      | Received CRC of sensor data 2(5:0) in bit 7:2 |

| 0x10 0x17 | Sensor data 3(63:0)                           |

| 0x10      | Sensor data 3(7:0)                            |

| 0x11      | Sensor data 3(14:8) in bit 6:0                |

| 0x12      | Sensor data                                   |

| 0x13      | not changed                                   |

| 0x14      | not changed                                   |

| 0x15      | not changed                                   |

| 0x16      | not changed                                   |

| 0x17      | Received CRC of sensor data 3(5:0) in         |

|           | bit 7:2                                       |

| 0x18 0x1F | not changed                                   |

| 0x20 0x27 | not changed                                   |

| 0x28 0x2F | not changed                                   |

| 0x30 0x37 | not changed                                   |

| 0x38 0x3F | not changed                                   |

Table 15: Address mapping of sensor data

## **Dual SPI Interface Operation**

iC-MB4 can be operated with two SPI interfaces on a single BiSS interface. With activated second SPI (NWR\_E = 0) the SCDATA range is splitted into two sections, each SPI with 4 SCD data section. The SPI2 can only access the related SCDATA. The SPI2 has no access to the configuration nor status information.

| Addr.     | Content               |

|-----------|-----------------------|

| 0x00      | SPI1: SCDATA 1(7:0)   |

| 0x01      | SPI1: SCDATA 1(15:8)  |

| 0x02      | SPI1: SCDATA 1(23:16) |

| 0x03      | SPI1: SCDATA 1(31:24) |

| 0x04      | SPI1: SCDATA 1(39:32) |

| 0x05      | SPI1: SCDATA 1(47:40) |

| 0x06      | SPI1: SCDATA 1(55:48) |

| 0x07      | SPI1: SCDATA 1(63:56) |

| 0x08 0x0F | SPI1: SCDATA 2(63:0)  |

| 0x10 0x17 | SPI1: SCDATA 3(63:0)  |

| 0x18 0x1F | SPI1: SCDATA 4(63:0)  |

| 0x20 0x27 | SPI2: SCDATA 1(63:0)  |

| 0x28 0x2F | SPI2: SCDATA 2(63:0)  |

| 0x30 0x37 | SPI2: SCDATA 3(63:0)  |

| 0x38 0x3F | SPI2: SCDATA 4(63:0)  |

Table 16: Address mapping of sensor data access by SPI1 and SPI2

The second BiSS interface channel 2 is only available with iC-MB4 QFN28.

Rev B2, Page 26/40

#### **CONTROL COMMUNICATION**

For the interim storage of register information read out from or writing to the slaves, iC-MB4 has an individual storage area (addresses 0x80 ... 0xBF) which can temporarily store up to 64 bytes of data. Just one single command starts the transmission (writing to the slave or read from the slave). The slave addressed is set by the SLAVEID(2:0) and the first address for the register data access is set by REGADR. The transfer of register data may take longer than a sensor data transfer cycle, so that the content of the sensor data RAM is then often obsolete.

### **Configuration of Register Communication**