FEDL7074-003DIGEST-01

# **OKI Semiconductor**

# Issue Date: Oct. 27, 2003

# ML7074-003 GA

**VoIP CODEC**

#### **GENERAL DESCRIPTION**

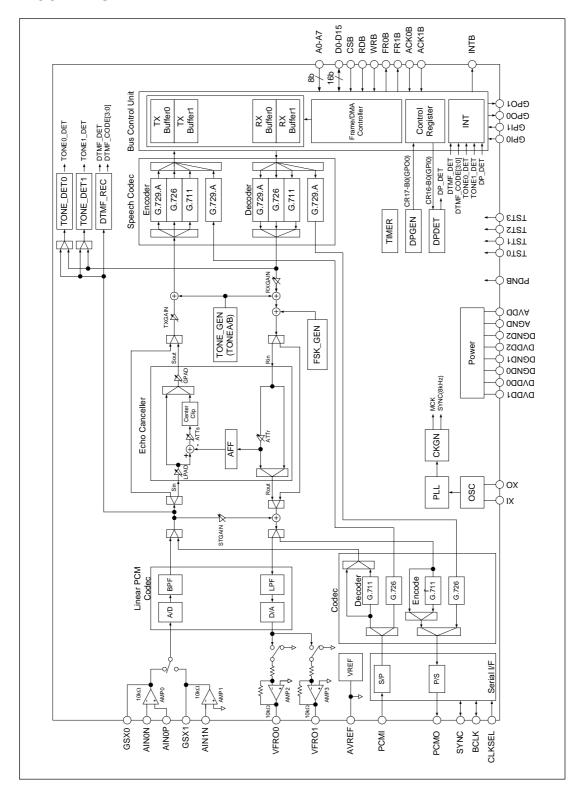

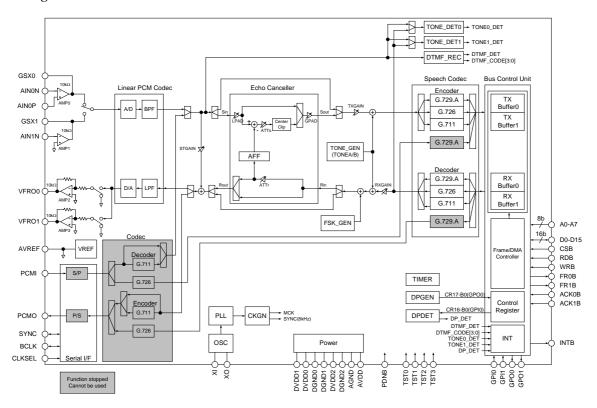

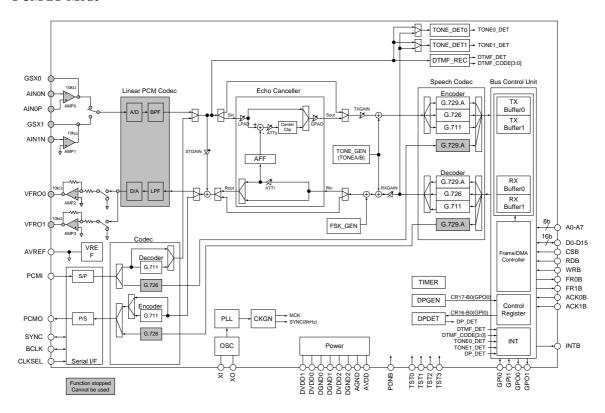

The ML7074-003GA is a speech CODEC for VoIP. This LSI allows selection of G.729.A, G.726, or G.711 standard as a speech CODEC. The LSI is optimum for adding VoIP functions to TAs, routers, etc., since it has the functions of an echo canceller for 32 msec delay, DTMF detection, tone detection, tone generation, etc.

# **FEATURES**

- Single 3.3 V power supply operation (DV<sub>DD</sub>0, 1, 2, AV<sub>DD</sub>: 3.0 to 3.6 V)

- Speech CODEC:

Selectable among G.729.A (8 kbps), G726 (32 kbps), G.711 (64 kbps)  $\mu$ -law, and A-law Mutual conversion function between G.729.A (8 kbps) and G.726 (32 kbps).

- Echo canceller for 32 ms delay

- DTMF detect function

- Tone detect function: 2 systems (1650 Hz, 2100 Hz: Detect frequency can be changed.)

- Tone generate function

- FSK generate function

- Dial pulse detect function

- Dial pulse transmit function

- Internal 1-channel 16-bit timer

- Built-in FIFO buffers (640 bytes) for transferring transmit and receive data Frame/DMA (slave) interface selectable.

- Master clock frequency: 4.096 MHz (crystal oscillation or external input)

- Hardware or software power down operation possible.

- Analog input/output type:

Two built-in input amplifiers,  $10~M\Omega$  driving Two built-in output amplifiers,  $10~k\Omega$  driving

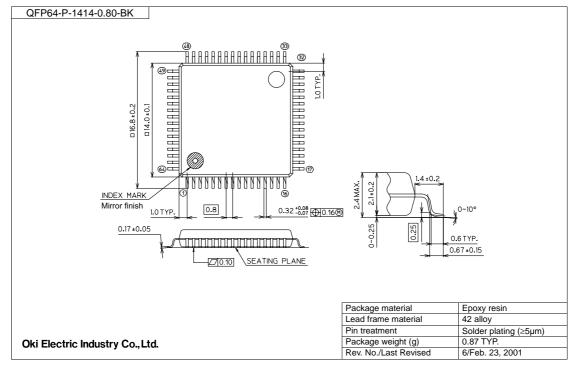

• Package:

64-pin plastic QFP (QFP64-P-1414-0.80-BK)

• Ordering part number:

ML7074-003GA

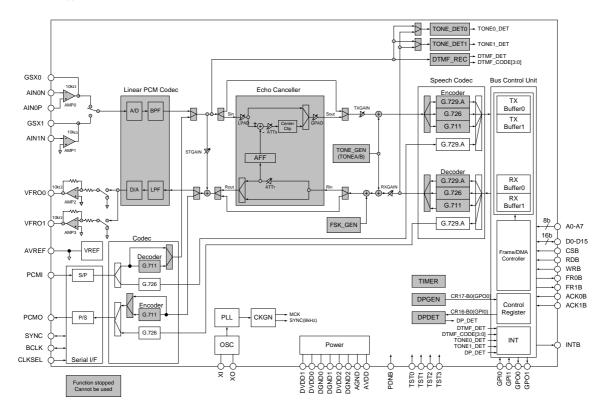

# **BLOCK DIAGRAM**

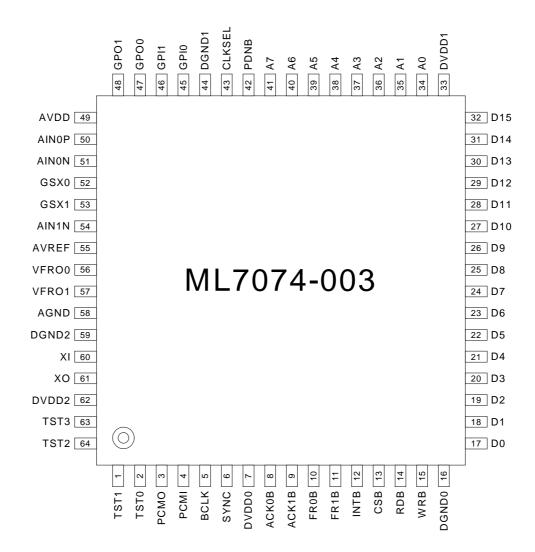

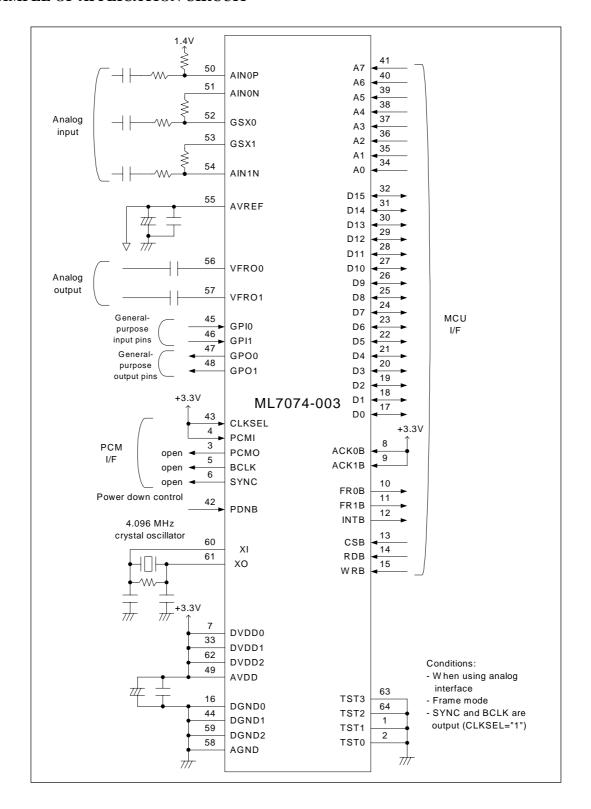

# PIN ASSIGNMENT (TOP VIEW)

64-pin plastic QFP

# PIN DESCRIPTIONS

| Pin<br>No. | Symbol     | I/O | PDNB = "0"                            | 100                                                                    |

|------------|------------|-----|---------------------------------------|------------------------------------------------------------------------|

| 1          | TST1       | I   | "0"                                   | Test control input 1: Normally input "0".                              |

| 2          | TST0       | I   | "0"                                   | Test control input 0: Normally input "0".                              |

| 3          | PCMO       | 0   | "Hi-z"                                | PCM data output                                                        |

| 4          | PCMI       | I   | I                                     | PCM data input                                                         |

|            |            |     |                                       | CLKSEL = "0"                                                           |

| 5          | BCLK       | 1/0 | ı                                     | PCM shift clock input                                                  |

| 3          | DOLK       | 1/0 | "L"                                   | CLKSEL = "1"                                                           |

|            |            |     | L                                     | PCM shift clock output                                                 |

|            |            |     | ı                                     | CLKSEL = "0"                                                           |

| 6          | SYNC       | I/O |                                       | PCM sync signal 8 kHz input                                            |

| Ü          | 01110      | 1/0 | "L"                                   | CLKSEL = "1"                                                           |

|            |            |     | L                                     | PCM sync signal 8 kHz output                                           |

| 7          | $DV_{DD}0$ | _   |                                       | Digital power supply                                                   |

| 8          | ACK0B      | I   | I                                     | Transmit buffer DMA access acknowledge signal input                    |

| 9          | ACK1B      | -   | I                                     | Receive buffer DMA access acknowledge signal input                     |

|            |            |     |                                       | FR0B: (CR11-B7 = "0")                                                  |

| 10         | FR0B       | 0   | "H"                                   | Transmit buffer frame signal output                                    |

| 10         | (DMARQ0B)  | "   | 11                                    | DMARQ0B: (CR11-B7 = "1")                                               |

|            |            |     |                                       | Transmit buffer DMA access request signal output                       |

|            |            |     |                                       | FR1B: (CR11-B7 = "0")                                                  |

| 11         | FR1B       | 0   | "H"                                   | Receive buffer frame signal output                                     |

|            | (DMARQ1B)  |     | ''                                    | DMARQ1B: (CR11-B7 = "1")                                               |

|            |            |     |                                       | Receive buffer DMA access request signal output                        |

| 12         | INTB       | 0   | "H"                                   | Interrupt request output                                               |

|            |            |     | 11                                    | "L" level is output for about 1.0 μsec when an interrupt is generated. |

| _13        | CSB        | I   | I                                     | Chip select control input                                              |

| 14         | RDB        | I   | I                                     | Read control input                                                     |

| 15         | WRB        | I   | I                                     | Write control input                                                    |

| 16         | DGND0      | _   | I                                     | Digital ground (0.0 V)                                                 |

| 17         | D0         | I/O | I                                     | Data input/output                                                      |

| 18         | D1         | I/O | I                                     | Data input/output                                                      |

| 19         | D2         | I/O | I                                     | Data input/output                                                      |

| 20         | D3         | I/O | I                                     | Data input/output                                                      |

| 21         | D4         | I/O | I                                     | Data input/output                                                      |

| 22         | D5         | I/O | I                                     | Data input/output                                                      |

| 23         | D6         | I/O | I                                     | Data input/output                                                      |

| 24         | D7         | I/O |                                       | Data input/output                                                      |

| 25         | D8         | I/O | 1                                     | Data input/output                                                      |

| 20         | Do         | 1/0 | ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' | Fix to input state when using in 8-bit bus access (CR11-B5 = "1").     |

| 26 | D9                 | I/O            | ı        | Data input/output                                                                        |

|----|--------------------|----------------|----------|------------------------------------------------------------------------------------------|

|    |                    | 1,0            | '        | Fix to input state when using in 8-bit bus access (CR11-B5 = "1").                       |

| 27 | D10                | I/O            | ı        | Data input/output                                                                        |

|    |                    | ","            | •        | Fix to input state when using in 8-bit bus access (CR11-B5 = "1").                       |

| 28 | D11                | 1/0            | 1        | Data input/output                                                                        |

|    |                    | - " -          | •        | Fix to input state when using in 8-bit bus access (CR11-B5 = "1").                       |

| 29 | D12                | 1/0            | 1        | Data input/output                                                                        |

|    |                    |                |          | Fix to input state when using in 8-bit bus access (CR11-B5 = "1").                       |

| 30 | D13                | I/O            | I        | Data input/output                                                                        |

|    |                    |                |          | Fix to input state when using in 8-bit bus access (CR11-B5 = "1").                       |

| 31 | D14                | I/O            | I        | Data input/output                                                                        |

|    |                    |                |          | Fix to input state when using in 8-bit bus access (CR11-B5 = "1").                       |

| 32 | D15                | I/O            | 1        | Data input/output                                                                        |

| 22 | D\/ 1              |                |          | Fix to input state when using in 8-bit bus access (CR11-B5 = "1").  Digital power supply |

| 33 | DV <sub>DD</sub> 1 | <del>  -</del> |          |                                                                                          |

| 34 | A0                 | I              | <u> </u> | Address input                                                                            |

| 35 | A1                 | ı              |          | Address input                                                                            |

| 36 | A2                 | I              | ı        | Address input                                                                            |

| 37 | A3                 | I              | I        | Address input                                                                            |

| 38 | A4                 | I              | ı        | Address input                                                                            |

| 39 | A5                 | ı              | l        | Address input                                                                            |

| 40 | A6                 | I              | I        | Address input                                                                            |

| 41 | A7                 | ı              | I        | Address input                                                                            |

|    |                    |                |          | Power down input                                                                         |

| 42 | PDNB               | 1              | "0"      | "0": Power down reset                                                                    |

|    |                    |                |          | "1": Normal operation                                                                    |

|    |                    |                |          | SYNC and BCLK I/O control input                                                          |

| 43 | CLKSEL             | 1              | 1        | "0": SYNC and BCLK become inputs                                                         |

|    |                    |                |          | "1": SYNC and BCLK become outputs                                                        |

| 44 | DGND1              | _              |          | Digital ground (0.0 V)                                                                   |

| 45 | ODIO               | Ι.             |          | General-purpose input pin 0 (5 V tolerant input)                                         |

| 45 | GPI0               | I              | I        | /Secondary function: Dial pulse detect input pin                                         |

| 46 | GPI1               | I              | I        | General-purpose input pin 1 (5 V tolerant input)                                         |

|    |                    |                |          | General-purpose output pin 0 (5 V tolerant output, can be pulled up                      |

| 47 | GPO0               | 0              | "L"      | externally)                                                                              |

|    |                    |                |          | /Secondary function: Dial pulse transmit pin                                             |

| 48 | GPO1               | 0              | "[ "     | General-purpose output pin 1 (5 V tolerant output, can be pulled up                      |

|    |                    |                | L        | externally)                                                                              |

| 49 | $AV_{DD}$          |                |          | Analog power supply                                                                      |

| 50 | AIN0P              | - 1            |          | AMP0 non-inverted input                                                                  |

| 51 | AIN0N              | - 1            |          | AMP0 inverted input                                                                      |

| 52 | GSX0               | 0              | "Hi-z"   | AMP0 output (10 kΩ driving)                                                              |

| 53 | GSX1               | 0              | "Hi-z"   | AMP1 output (10 kΩ driving)                                                              |

| 54 | AIN1N              | l              | I        | AMP1 inverted input                                                                      |

| 55 | AVREF              | 0              | "L"      | Analog signal ground (1.4 V)                                                             |

|    |                    |                |          |                                                                                          |

| 56 | VFRO0              | 0 | "Hi-z" | AMP2 Output (10 kΩ driving)                             |

|----|--------------------|---|--------|---------------------------------------------------------|

| 57 | VFRO1              | 0 | "Hi-z" | AMP3 Output (10 k $\Omega$ driving)                     |

| 58 | AGND               | _ |        | Analog ground (0.0 V)                                   |

| 59 | DGND2              | _ |        | Digital ground (0.0 V)                                  |

| 60 | XI                 | I | 1      | 4.096 MHz crystal oscillator I/F, 4.096 MHz clock input |

| 61 | XO                 | 0 | "H"    | 4.096 MHz crystal oscillator I/F                        |

| 62 | DV <sub>DD</sub> 2 | _ |        | Digital power supply                                    |

| 63 | TST3               | ı | "0"    | Test control input 3: Normally input "0".               |

| 64 | TST2               | I | "0"    | Test control input 2: Normally input "0".               |

# ABSOLUTE MAXIMUM RATINGS

| Parameter                    | Symbol   | Conditions          | Rating                   | Unit |

|------------------------------|----------|---------------------|--------------------------|------|

| Analog power supply voltage  | VDA      | _                   | -0.3 to 5.0              | V    |

| Digital power supply voltage | $V_{DD}$ | _                   | -0.3 to 5.0              | V    |

| Analog input voltage         | VAIN     | Analog pins         | $-0.3$ to $V_{DD} + 0.3$ | V    |

| Digital input valtage        | VDIN1    | Normal digital pins | $-0.3$ to $V_{DD} + 0.3$ | V    |

| Digital input voltage        | VDIN2    | 5 V tolerant pins   | -0.3 to 6.0              | V    |

| Storage temperature range    | Tstg     | _                   | −55 to +150              | °C   |

# RECOMMENDED OPERATING CONDITIONS

| Parameter                                 | Symbol   | Conditions                 | Min.    | Тур.  | Max.                  | Unit |

|-------------------------------------------|----------|----------------------------|---------|-------|-----------------------|------|

| Analog power supply voltage               | VDA      |                            | 3.0     | 3.3   | 3.6                   | V    |

| Digital power supply voltage              | $V_{DD}$ | _                          | 3.0     | 3.3   | 3.6                   | V    |

| Operating temperature range               | Ta       | _                          | -20     | _     | 60                    | °C   |

| Digital high level input voltage          | VIH1     | Digital input pins         | 2.0     | _     | V <sub>DD</sub> + 0.3 | V    |

|                                           | VIH2     | GPI0 and GPI1 pins         | 2.0     | _     | 5.5                   | V    |

| Digital low level input voltage           | VIL      | Digital pins               | -0.3    | _     | 0.8                   | V    |

| Digital input rise time                   | tIR      | Digital pins               | _       | 2     | 20                    | ns   |

| Digital input fall time                   | tIF      | Digital pins               |         | 2     | 20                    | ns   |

| Digital output load capacitance           | CDL      | Digital pins               |         |       | 50                    | pF   |

| Capacitance of bypass capacitor for AVREF | Cvref    | Between AVREF and AGND     | 2.2+0.1 | _     | 4.7+0.1               | μF   |

| Master clock frequency                    | Fmck     | MCK                        | -0.01%  | 4.096 | +0.01%                | MHz  |

| PCM shift clock frequency                 | Fbclk    | BCLK (at input)            | 64      |       | 2048                  | kHz  |

| PCM sync signal frequency                 | Fsync    | SYNC (at input)            | _       | 8.0   | _                     | kHz  |

| Clock duty ratio                          | DRCLK    | MCK, BCLK (at input)       | 40      | 50    | 60                    | %    |

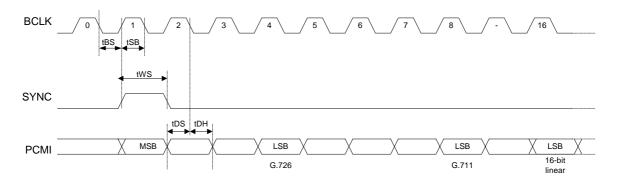

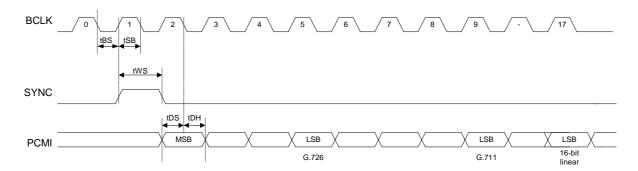

| PCM sync timing                           | tBS      | BCLK to SYNC<br>(at input) | 100     | _     |                       | ns   |

| T OW Syric unning                         | tSB      | SYNC to BCLK<br>(at input) | 100     | _     | _                     | ns   |

| PCM sync signal width                     | tWS      | SYNC (at input)            | 1BCLK   | _     | 100                   | μS   |

# **ELECTRICAL CHARACTERISTICS**

$\begin{array}{l} \textbf{DC Characteristics} \\ \text{(Unless otherwise specified, AV}_{DD} = 3.0 \text{ to } 3.6 \text{ V, DV}_{DD}0, \ 1, \ 2 = 3.0 \text{ to } 3.6 \text{ V, AGND} = \text{DGND0, 1, 2} = 0.0 \text{ V,} \\ \end{array}$  $Ta = -20 \text{ to } +60^{\circ}\text{C}$

| Parameter                 | Symbol            | Conditions                                                                                                                                                              | Min. | Тур.  | Max. | Unit |

|---------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|------|

|                           | ISS               | Standby state<br>(PDNB = "0", V <sub>DD</sub> = 3.3 V, Ta = 25°C)                                                                                                       | _    | 5.0   | 20.0 | μΑ   |

| Power supply current      | I <sub>DD</sub> 1 | Operating state 1 In the PCM/IF mode (SC_EN = "1", PCMIF_EN = "1", AFE_EN = "1", TRANS_EN = "1") Connect a 4.096 MHz crystal oscillator between XI and XO.              | _    | 45.0  | 55.0 | mA   |

|                           | I <sub>DD</sub> 2 | Operating state 2 When operating the whole system (SC_EN = "1", PCMIF_EN = "0", TRANS_EN = "0", AFE_EN = "0") Connect a 4.096 MHz crystal oscillator between XI and XO. | _    | 50.0  | 65.0 | mA   |

| Digital input pin         | IIH               | $Vin = DV_{DD}$                                                                                                                                                         |      | 0.01  | 1.0  | μΑ   |

| input leakage current     | IIL               | Vin = DGND                                                                                                                                                              | -1.0 | -0.01 | _    | μΑ   |

| Digital I/O pin           | IOZH              | $Vout = DV_{DD}$                                                                                                                                                        | _    | 0.01  | 1.0  | μΑ   |

| output leakage current    | IOZL              | Vout = DGND                                                                                                                                                             | -1.0 | -0.01 | _    | μΑ   |

| High level output voltage | VOH               | Digital output pins, I/O pins<br>IOH = 4.0 mA<br>IOH = 1.0 mA (XO pin)                                                                                                  | 2.2  | _     | _    | V    |

| Low level output voltage  | VOL               | Digital output pins, I/O pins<br>IOL = -4.0 mA<br>IOL = -1.0 mA (XO pin)                                                                                                | _    | _     | 0.4  | V    |

| Input capacitance *1      | CIN               | Input pins                                                                                                                                                              | _    | 8     | 12   | pF   |

Note: \*1 Guaranteed design value

# **Analog Interface**

(Unless otherwise specified,  $AV_{DD} = 3.0$  to 3.6 V,  $DV_{DD}0$ , 1, 2 = 3.0 to 3.6 V, AGND = DGND0, 1, 2 = 0.0 V, Ta = -20 to +60°C)

| Parameter               | Symbol | Conditions                                     | Min. | Тур. | Max. | Unit |

|-------------------------|--------|------------------------------------------------|------|------|------|------|

| Input resistance *1     | RIN    | AINON, AINOP, AIN1N                            | 10   | _    | _    | MΩ   |

| Output load resistance  | RL     | GSX0, GSX1, VFRO0, VFRO1                       | 10   | _    | _    | kΩ   |

| Output load capacitance | CL     | Analog output pins                             | _    | _    | 50   | pF   |

| Offset voltage          | VOF    | VFRO0, VFRO1                                   | -40  | _    | 40   | mV   |

| Output voltage level *2 | VO     | GSX0, GSX1, VFRO0, VFRO1<br>RL = 10 k $\Omega$ | _    | _    | 1.3  | Vpp  |

# Notes:

<sup>\*1</sup> Guaranteed design value

<sup>\*2</sup>  $-7.7 \text{ dBm } (600\Omega) = 0 \text{ dBm0}, +3.17 \text{ dBm0} = 1.3 \text{ Vpp}$

# **AC Characteristics**

CODEC (Speech CODEC in G.711 ( $\mu$ -law) Mode) (Unless otherwise specified, AV<sub>DD</sub> = 3.0 to 3.6 V, DV<sub>DD</sub>0, 1, 2 = 3.0 to 3.6 V, AGND = DGND0, 1, 2 = 0.0 V, Ta = -20 to +60°C)

| Donomoton                           | Curah al | Condition                                 | ons                  | NAin  | T        | Max   | 1.1   |

|-------------------------------------|----------|-------------------------------------------|----------------------|-------|----------|-------|-------|

| Parameter                           | Symbol   | Frequency (Hz)                            | Level (dBm0)         | Min.  | Тур.     | Max.  | Unit  |

|                                     | LT1      | 0 to 60                                   |                      | 25    | _        | _     | dB    |

|                                     | LT2      | 300 to 3000                               |                      | -0.15 |          | 0.20  | dB    |

| Transmit frequency                  | LT3      | 1020                                      | 0                    | Refe  |          |       |       |

| characteristics                     | LT4      | 3300                                      | 0                    | -0.15 | _        | 0.80  | dB    |

|                                     | LT5      | 3400                                      |                      | 0     | _        | 0.80  | dB    |

|                                     | LT6      | 3968.75                                   |                      | 13    | _        |       | dB    |

|                                     | LR2      | 0 to 3000                                 |                      | -0.15 | _        | 0.20  | dB    |

| Describes for succession            | LR3      | 1020                                      |                      | Refe  |          |       |       |

| Receive frequency characteristics   | LR4      | 3300                                      | 0                    | -0.15 |          | 0.80  | dB    |

| Characteristics                     | LR5      | 3400                                      |                      | 0     | _        | 0.80  | dB    |

|                                     | LR6      | 3968.75                                   |                      | 13    | _        |       | dB    |

|                                     | SDT1     |                                           | 3                    | 35    | _        |       | dBp   |

| <b>-</b>                            | SDT2     |                                           | 0                    | 35    | _        |       | dBp   |

| Transmit signal to noise ratio [*1] | SDT3     | 1020                                      | -30                  | 35    | _        |       | dBp   |

|                                     | SDT4     |                                           | -40                  | 28    | _        |       | dBp   |

|                                     | SDT5     |                                           | -45                  | 23    | _        |       | dBp   |

| December signal to waite            | SDR1     |                                           | 3                    | 35    |          |       | dBp   |

|                                     | SDR2     |                                           | 0                    | 35    | _        |       | dBp   |

| Receive signal to noise             | SDR3     | 1020                                      | -30                  | 35    | _        |       | dBp   |

| ratio [*1]                          | SDR4     |                                           | -40                  | 28    | _        |       | dBp   |

|                                     | SDR5     |                                           | -45                  | 23    | _        |       | dBp   |

|                                     | GTT1     |                                           | 3                    | -0.2  | _        | 0.2   | dB    |

| Too a small in too love !           | GTT2     |                                           | -10                  | Refe  | erence v |       |       |

| Transmit inter-level                | GTT3     | 1020                                      | -40                  | -0.2  |          | 0.2   | dB    |

| loss error                          | GTT4     |                                           | -50                  | -0.6  | _        | 0.6   | dB    |

|                                     | GTT5     |                                           | -55                  | -1.2  |          | 1.2   | dB    |

|                                     | GTR1     |                                           | 3                    | -0.2  | _        | 0.2   | dB    |

| 5                                   | GTR2     |                                           | -10                  | Refe  | erence v | alue  | _     |

| Receive inter-level loss            | GTR3     | 1020                                      | -40                  | -0.2  | _        | 0.2   | dB    |

| error                               | GTR4     |                                           | -50                  | -0.6  |          | 0.6   | dB    |

|                                     | GTR5     |                                           | -55                  | -1.2  |          | 1.2   | dB    |

| Idle channel noise                  | NIDLT    | _                                         | Analog input = AVREF | _     | _        | -68   | dBm0p |

| [*1]                                | NIDLR    | _                                         | PCMI = "1"           | _     |          | -72   | dBm0p |

| Transmit absolute level [*2]        | AVT      | 1020                                      | 0                    | 0.285 | 0.320    | 0.359 | Vrms  |

| Receive absolute level [*2]         | AVR      | 1020                                      | 0                    | 0.285 | 0.320    | 0.359 | Vrms  |

| Power supply noise                  | PSRRT    | Noise frequency                           |                      | 30    | —        |       | dB    |

| reject ratio                        | PSRRR    | range: 0 to 50 kHz<br>Noise level: 50mVpp | _                    | 30    | _        | _     | dB    |

Notes: \*1 Using P-message filter

<sup>\*2 0.320</sup> Vrms = 0 dBm0 = -7.7 dBm (600 $\Omega$ )

# Gain Setting (Speech CODEC in G.711 (μ-law) Mode)

(Unless otherwise specified,  $AV_{DD} = 3.0$  to 3.6 V,  $DV_{DD}0$ , 1, 2 = 3.0 to 3.6 V, AGND = DGND0, 1, 2 = 0.0 V,

$Ta = -20 \text{ to } +60^{\circ}\text{C}$

| Parameter             | Symbol | Conditions | Min. | Тур. | Max. | Unit |

|-----------------------|--------|------------|------|------|------|------|

| Transmit and receive  | GAC    |            | 1.0  |      | 1.0  | dB   |

| gain setting accuracy | GAC    | _          | -1.0 |      | 1.0  | uБ   |

# Tone Output (Speech CODEC in G.711 (µ-law) Mode)

(Unless otherwise specified,  $AV_{DD} = 3.0$  to 3.6 V,  $DV_{DD}0$ , 1, 2 = 3.0 to 3.6 V, AGND = DGND0, 1, 2 = 0.0 V,

$Ta = -20 \text{ to } +60^{\circ}\text{C}$

| Parameter           | Symbol | Conditions                | Min. | Тур. | Max. | Unit |

|---------------------|--------|---------------------------|------|------|------|------|

| Frequency deviation | fDFT   | Relative to set frequency | -1.5 | _    | 1.5  | %    |

| Output level        | oLEV   | Relative to set gain      | -2.0 | _    | 2.0  | dB   |

# DTMF Detector, Other Detectors (Speech CODEC in G.711 (µ-law) Mode)

(Unless otherwise specified,  $AV_{DD} = 3.0$  to 3.6 V,  $DV_{DD}0$ , 1, 2 = 3.0 to 3.6 V, AGND = DGND0, 1, 2 = 0.0 V,

Ta =  $-20 \text{ to } +60^{\circ}\text{C}$

| Parameter             | Symbol | Conditions                   | Min. | Тур. | Max. | Unit |

|-----------------------|--------|------------------------------|------|------|------|------|

| Detect level accuracy | dLAC   | Relative to set detect level | -2.5 |      | 2.5  | dB   |

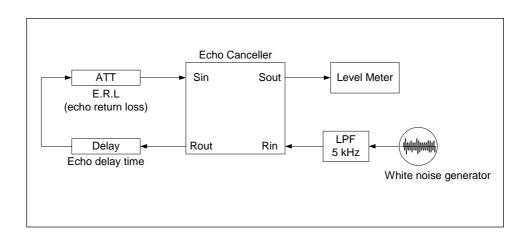

#### **Echo Canceller**

(Unless otherwise specified,  $AV_{DD} = 3.0$  to 3.6 V,  $DV_{DD}0$ , 1, 2 = 3.0 to 3.6 V, AGND = DGND0, 1, 2 = 0.0 V,

$Ta = -20 \text{ to } +60^{\circ}\text{C}$

| Parameter                | Symbol | Conditions                                                                             | Min. | Тур.     | Max. | Unit |

|--------------------------|--------|----------------------------------------------------------------------------------------|------|----------|------|------|

| Echo attenuation         | eRES   | In the analog I/F mode In the PCM I/F (16-bit linear) mode In the PCM I/F (G.711) mode |      | 35<br>30 | _    | dB   |

| Erasable echo delay time | tECT   | _                                                                                      | _    | _        | 32   | ms   |

#### Measurement method

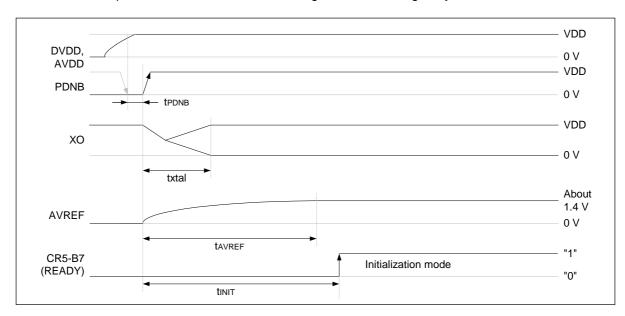

# PDNB, XO, AVREF Timings

| 1a = -20 to +00 0)                |                      |                                                                |      |      |      |      |

|-----------------------------------|----------------------|----------------------------------------------------------------|------|------|------|------|

| Parameter                         | er Symbol Conditions |                                                                | Min. | Тур. | Max. | Unit |

| Power down signal pulse width     | tPDNB                | PDNB pin                                                       | 1    | _    | _    | μS   |

| Oscillation start-up time         | txtal                |                                                                | _    | 2+α  | 100  | ms   |

| AVREF rise time                   | tAVREF               | AVREF = 1.4 (90%)<br>C5 = 4.7 μF, C6 = 0.1 μF<br>(See Fig. 9.) | _    | _    | 600  | ms   |

| Initialization mode start-up time | tINIT                | _                                                              | _    | 1    | _    | s    |

<sup>\*</sup>  $\alpha$  is a value that depends on the oscillation stabilizing time when using a crystal oscillator.

Fig. 1 PDNB, XO, and AVREF timings

# PCM I/F Mode

| Ta | = -20  to | +60°C) |

|----|-----------|--------|

| ıα | 20 10     | TOO 01 |

| 14 - 20 10 100 0)            |        |                                         |       |      |       |      |

|------------------------------|--------|-----------------------------------------|-------|------|-------|------|

| Parameter                    | Symbol | Conditions                              | Min.  | Тур. | Max.  | Unit |

| Bit clock frequency          | fBCLK  | CDL = 20pF(at output)                   | -0.1% | 64   | +0.1% | kHz  |

| Bit clock duty ratio         | dBCLK  | CDL = 20pF(at output)                   | 45    | 50   | 55    | %    |

| Sync signal frequency        | fSYNC  | CDL = 20pF(at output)                   | -0.1% | 8    | +0.1% | kHz  |

| Syna signal duty ratio       | dSYNC1 | CDL = 20pF(at output) At 64 kHz output  | 12.4  | 12.5 | 12.6  | %    |

| Sync signal duty ratio       | dSYNC2 | CDL = 20pF(at output) At 128 kHz output | 6.24  | 6.25 | 6.26  | %    |

| Transmit/receive signal sync | tBS    | BCLK to SYNC<br>(at output)             | 100   | _    | _     | ns   |

| timing                       | tSB    | SYNC to BCLK<br>(at output)             | 100   | _    | _     | ns   |

| Input setup time             | tDS    | _                                       | 100   |      | _     | ns   |

| Input hold time              | tDH    | _                                       | 100   |      | _     | ns   |

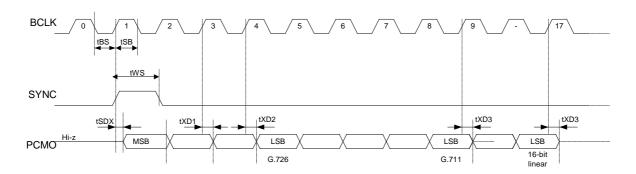

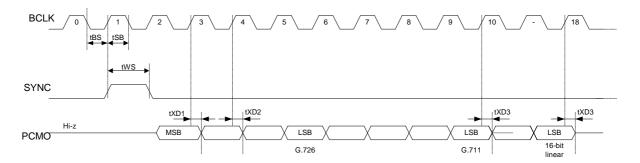

| Digital output dalay time    | tSDX   | DCMO min                                |       |      | 100   | ns   |

| Digital output delay time    | tXD1   | PCMO pin Pull-up, pull-down resistors   | _     | _    | 100   | ns   |

| Digital output hold time     | tXD2   | RDL = 1 k $\Omega$ , CDL = 50 pF        | _     | _    | 100   | ns   |

| Digital output hold time     | tXD3   | RDL = 1  Ks2, CDL = 50  pr              | _     | _    | 100   | ns   |

Fig. 2 PCM I/F mode input timing (long frame)

Fig. 3 PCM I/F mode input timing (short frame)

Fig. 4 PCM I/F mode output timing (long frame)

Fig. 5 PCM I/F mode output timing (short frame)

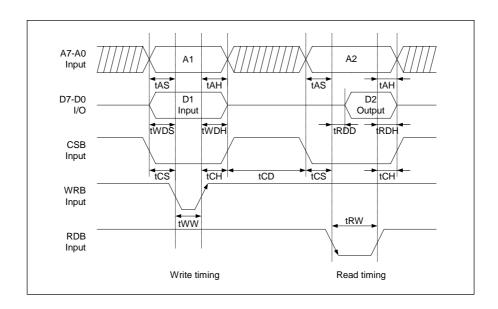

# **Control Register Interface**

| Parameter                   | Symbol | Conditions | Min. | Тур. | Max. | Unit |

|-----------------------------|--------|------------|------|------|------|------|

| Address setup time          | tAS    |            | 10   | —    | _    | ns   |

| Address hold time           | tAH    |            | 10   |      |      | ns   |

| Write data setup time       | tWDS   |            | 10   | _    | _    | ns   |

| Write data hold time        | tWDH   |            | 10   | _    | 1    | ns   |

| CSB setup time              | tCS    |            | 10   |      |      | ns   |

| CSB hold time               | tCH    | CL = 50 pF | 10   |      |      | ns   |

| WRB pulse width             | tWW    |            | 10   |      |      | ns   |

| Read data output delay time | tRDD   |            | _    | _    | 20   | ns   |

| Read data output hold time  | tRDH   |            | 3    |      |      | ns   |

| RDB pulse width             | tRW    |            | 25   |      |      | ns   |

| CSB disable time            | tCD    |            | 10   | _    | 1    | ns   |

Fig. 6 Control register interface

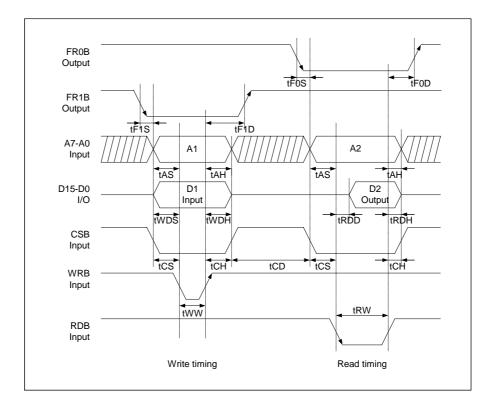

# Transmit and Receive Buffer Interface (in Frame Mode)

| Parameter                   | Symbol | Conditions | Min. | Тур. | Max. | Unit |

|-----------------------------|--------|------------|------|------|------|------|

| FR1B setup time             | tF1S   |            | 3    |      | _    | ns   |

| FR1B output delay time      | tF1D   |            | _    | _    | 20   | ns   |

| Address setup time          | tAS    |            | 10   |      | _    | ns   |

| Address hold time           | tAH    |            | 10   | _    | _    | ns   |

| Write data setup time       | tWDS   |            | 10   | —    | _    | ns   |

| Write data hold time        | tWDH   |            | 10   | _    | _    | ns   |

| CSB setup time              | tCS    | CL = 50 pF | 10   |      | _    | ns   |

| CSB hold time               | tCH    |            | 10   | _    | _    | ns   |

| WRB pulse width             | tWW    |            | 10   | _    | _    | ns   |

| FR0B setup time             | tF0S   |            | 3    |      | _    | ns   |

| FR0B output delay time      | tF0D   |            | _    | _    | 20   | ns   |

| Read data output delay time | tRDD   |            | _    | —    | 30   | ns   |

| Read data output hold time  | tRDH   |            | 3    | —    | _    | ns   |

| RDB pulse width             | tRW    |            | 35   |      |      | ns   |

| CSB disable time            | tCD    |            | 10   | _    | _    | ns   |

Fig. 7 Transmit and receive buffer interface (in frame mode)

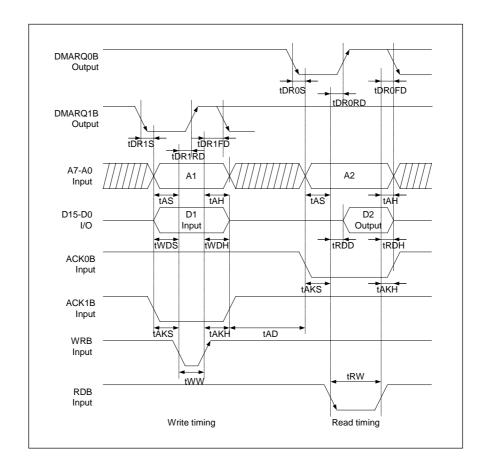

# Transmit and Receive Buffer Interface (in DMA Mode)

| Parameter                    | Symbol | Conditions | Min. | Тур. | Max. | Unit |

|------------------------------|--------|------------|------|------|------|------|

| DMARQ1B setup time           | tDR1S  |            | 3    | —    | —    | ns   |

| DMARQ1B output delay time    | tDR1RD |            | _    | _    | 25   | ns   |

| DIVIARQ 16 output delay time | tDR1FD |            | _    | _    | 25   | ns   |

| Address setup time           | tAS    |            | 10   | _    | _    | ns   |

| Address hold time            | tAH    |            | 10   |      | _    | ns   |

| Write data setup time        | tWDS   |            | 10   | _    | _    | ns   |

| Write data hold time         | tWDH   | CL = 50 pF | 10   | _    | _    | ns   |

| ACK setup time               | tAKS   |            | 10   | _    | _    | ns   |

| ACK hold time                | tAKH   |            | 10   | —    | —    | ns   |

| WRB pulse width              | tWW    |            | 10   | _    | _    | ns   |

| DMARQ0B setup time           | tDR0S  |            | 3    | _    | _    | ns   |

| DMARQ0B output delay time    | tDR0RD |            |      |      | 20   | ns   |

| DIVIANGOB output delay time  | tDR0FD |            | _    | —    | 25   | ns   |

| Read data output delay time  | tRDD   |            | _    | _    | 30   | ns   |

| Read data output hold time   | tRDH   |            | 3    |      |      | ns   |

| RDB pulse width              | tRW    |            | 35   |      | _    | ns   |

| ACKB disable time            | tAD    |            | 10   |      | _    | ns   |

Fig. 8 Transmit and receive buffer interface (in DMA mode)

#### PIN FUNCTION DESCRIPTIONS

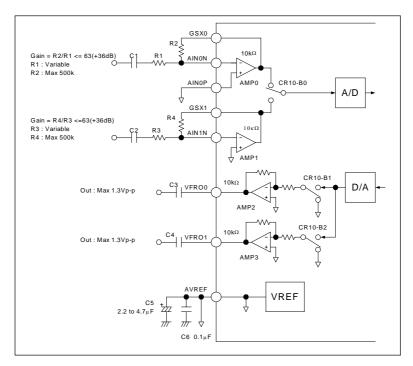

# AINON, AINOP, GSX0, AIN1N, GSX1

These are the analog transmit input and transmit level adjust pins. Each of AIN0N and AIN1N is connected to each of the inverting input pins of the built-in transmit amplifiers AMP0 and AMP1, and AIN0P is connected to the non-inverting input pin of AMP0. In addition, GSX0 and GSX1 are connected to the output pins of AMP0 and AMP1, respectively. The selection between AMP0 and AMP1 is made by CR10-B0. See Fig. 9 for the method of making level adjustment. During the power down mode (when PDNB = "0" or CR0-B7 = "1"), the outputs of GSX0 and GSX1 go to the high impedance state. If AMP0 is not used in the specific application of this LSI, short GSX0 with AIN0N and connect AIN0P with AVREF. When AMP1 is not used, short GSX1 with AIN1N.

#### Notice:

It is recommended to select the amplifier to be used before the conversation starts, since a small amount of noise will be generated if the amplifier selection is changed while conversation is in progress.

# VFRO0, VFRO1

These are analog receive output pins and are connected to the output pins of the built-in receive amplifiers AMP2 and AMP3, respectively. The output signals of VFRO0 and VFRO1 can be selected using CR10-B1 and CR10-B2, respectively. When selected ("1"), the received signal will be output, and when deselected ("0"), the AVREF signal (about 1.4 V) will be output. In the power down mode, these pins will be in the high impedance state. It is recommended to use these output signals via DC coupling capacitors.

# Notice:

It is recommended to select the amplifier to be used before the conversation starts, since a small amount of noise is generated if the output selection is changed while the conversation is in progress.

At the time of resetting or releasing from the reset state, it is recommended to select the AVREF as outputs of VFRO0 and VFRO1.

Fig. 9 Analog interface

#### **AVREF**

This is the output pin for the analog signal ground potential. The output potential at this pin will be about 1.4 V. Connect a 2.2 to 4.7  $\mu$ F (aluminum electrolytic type) capacitor and a 0.1  $\mu$ F (ceramic type) capacitor in parallel between this pin and the GND pin as bypass capacitors. The output at the AVREF pin goes to 0.0 V in the power down mode. The voltage starts rising after the power down mode is released (PDNB = "1" and also CR0-B7 = "0"). The rise time is about 0.6 sec.

#### XI, XO

These are the pins for either connecting the crystal oscillator for the master clock or for inputting an external master clock signal.

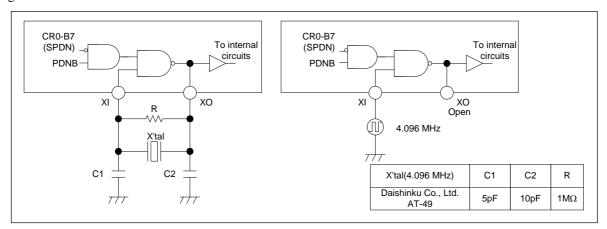

The oscillations of the master clock oscillator will be stopped during a power down due to the PDNB signal or during a software power down due to CR0-B7 (SPDN). The oscillations start when the power down condition is released, and the internal clock supply of the LSI will be started after counting up the oscillation stabilization period (of about 16 ms). Examples of crystal oscillator connection and external master clock input are shown in Fig. 10.

Fig. 10 Examples of oscillator circuit and clock input

# **PDNB**

This is the power down control input pin. The power down mode is entered when this pin goes to "0". In addition, this pin also has the function of resetting the LSI. In order to prevent wrong operation of the LSI, carry out the initial power-down reset after switching on the power using this PDNB pin. Also, keep the PDNB pin at "0" level for 1 µs or more to initiate the power down state.

Further, it is possible to carry out a power down reset of the LSI when the power is being supplied by performing control of CR0-B7 (SPDN) in the sequence "0"  $\rightarrow$  "1"  $\rightarrow$  "0".

The READY signal (CR5-B7) goes to "1" about 1.0 second after the power down mode is released thereby entering the mode of setting various functions (initialization mode). See Fig. 1 for the timings of PDNB and AVREF, XO, and the initialization mode.

Notice: At the time of switching on the power, start from the power down mode using PDNB.

# $DV_{DD}0$ , $DV_{DD}1$ , $DV_{DD}2$ , $AV_{DD}$

These are power supply pins.  $DV_{DD}0$ , 1, 2 are the power supply pins for the digital circuits while  $AV_{DD}$  is the power supply pin for the analog circuits of the LSI. Connect these pins together in the neighborhood of the LSI and connect as bypass capacitors a 10  $\mu$ F electrolytic capacitor and a 0.1  $\mu$ F ceramic capacitor in parallel between the DGND and AGND pins.

# DGND0, DGND1, DGND2, AGND

These are ground pins. GDND0, 1, 2 are the ground pins for the digital circuits and AGND is the ground pin for the analog circuits of the LSI. Connect these pins together in the neighborhood of the LSI.

# TST0, TST1, TST2, TST3

These are input pins for testing purposes only. Keep the inputs to these pins at the "0" level during normal use conditions.

#### **INTB**

This is the interrupt request output pin. An "L" level is output for a duration of about 1.0  $\mu$ sec at this pin when there is a change in state of an interrupt cause.

This output will be maintained at the "H" level when there is no change in state of any of the interrupt causes. The actual interrupt cause generating the interrupt can be verified by reading CR3 and CR4. The different interrupt causes are described below.

# • Underflow error (CR3-B0)

An interrupt is generated when an internal read from the receive buffer occurs before the writing into the receive buffer from the MCU has been completed.

An interrupt is generated when a normal writing is made in the receive buffer by the MCU and the underflow error is released.

#### • Overrun error (CR3-B1)

An interrupt is generated when an internal write of the next data into the transmit buffer occurs before the transmit buffer data read out from the MCU has been completed.

An interrupt is generated when a normal read out is made from the transmit buffer by the MCU and the overrun error is released.

- When a dial pulse is detected (CR4-B6).

- When a DTMF signal is detected (CR4-B4).

- When DTMF\_CODEC0, 1, 2, 3 are detected (CR4-B0, B1, B2, B3).

An interrupt is generated when a DTMF signal is detected.

An interrupt is generated when there is a change from the DTMF signal detected state to the no-detected state. An interrupt is generated when there is a change in the detected code (CR4-B0, B1, B2, B3) in the condition in which a DTMF signal is being detected.

# • When TONE0 is detected (CR3-B3).

An interrupt is generated when a 1650 Hz tone signal is detected.

An interrupt is generated when there is a change to the non-detection condition in the tone signal detection condition.

#### • When TONE1 is detected (CR3-B4).

An interrupt is generated when a 2100 Hz tone signal is detected.

An interrupt is generated when there is a change to the non-detection condition in the tone signal detection condition.

# • When FGEN\_RQ is generated (CR3-B6).

An interrupt is generated when the FSK generator makes a request for the next data to be transmitted.

An interrupt is generated when there is a change from the condition in which the FSK generator is requesting for transmission data to the condition in which there is no request for internal fetch of the data to be transmitted next.

# • When DSP\_ERR is detected (CR3-B7).

An interrupt is generated when any error occurs in the DSP inside the LSI.

# A0 to A7

These are the address input pins for use during an access of the frame, DMA, or control registers. The different addresses will be the following.

Transmit buffer (TX Buffer)

A7 to A0 = 10xxxxxxb (the lower 6 bits are not valid)

Receive buffer (RX Buffer)

A7 to A0 = 01xxxxxxb (the lower 6 bits are not valid)

Control register (CR)

A7 to A0 = 00xxxxxxb

#### D0 to D15

These are the data input/output pins for use during an access of the frame, DMA, or control registers. Connect pull-up resistors to these pins since they are I/O pins. When the 8-bit bus access method is selected by CR11-B5, only D0 to D7 become valid. Since the higher 8 bits D8 to D15 will always be in the input state when the 8-bit bus access method is selected (CR11-B5 = "1"), tie them to "0" or "1" inputs.

#### CSB

This is the chip select input pin for use during a frame or control register access.

#### RDB

This is the read enable input pin for use during a frame, DMA, or control register access.

#### **WRB**

This is the write enable input pin for use during a frame, DMA, or control register access.

# FR0B (DMARQ0B)

• FR0B (In frame mode, CR11-B7 = "0")

This is the transmit frame output pin which outputs the signal when the transmit buffer is full during frame access. This pin outputs an "L" level when the transmit buffer becomes full, and maintains that "L" level output until a specific number of words are read out from the MCU.

• DMARQ0B (In DMA mode, CR11-B7 = "1")

This is the DMA request output pin which outputs the signal when the transmit buffer is full during DMA access. This output becomes "L" when the transmit buffer becomes full, and returns to the "H" level automatically on the falling edge of the read enable signal (RDB = "1"  $\rightarrow$  "0") when there is an acknowledgement signal (ACK0B = "0") from the MCU. This relationship is repeated until a specific number of words are read out from the MCU.

# FR1B (DMARQ1B)

• FR1B (In frame mode, CR11-B7 = "0")

This is the receive frame output pin which outputs the signal when the receive buffer is empty during frame access. This pin outputs an "L" level when the receive buffer becomes empty, and maintains that "L" level output until a specific number of words are written from the MCU.

• DMARQ1B (In DMA mode, CR11-B7 = "1")

This is the DMA request output pin which outputs the signal when the receive buffer is empty during DMA access. This output becomes "L" when the receive buffer becomes empty, and returns to the "H" level automatically on the falling edge of the write enable signal (WRB = "1"  $\rightarrow$  "0") when there is an acknowledgement signal (ACK1B = "0") from the MCU. This relationship is repeated until a specific number of words are written from the MCU.

#### ACK0B

This is the DMA acknowledgement input pin for the DMARQ0B signal during DMA access of the transmit buffer and becomes valid in the DMA mode (CR11-B7 = "1").

Tie this pin to "1" when using this LSI in the frame access mode (CR11-B7 = "0").

# ACK1B

This is the DMA acknowledgement input pin for the DMARQ1B signal during DMA access of the receive buffer and becomes valid in the DMA mode (CR11-B7 = "1").

Tie this pin to "1" when using this LSI in the frame access mode (CR11-B7 = "0").

# GPI0, GPI1

These are general-purpose input pins. The state ("1" or "0") of each of these GPI0 and GPI1 pins can be read out respectively from CR16-B0 and CR16-B1. Further, GPI0 becomes the input pin for the dial pulse detector (DPDET) in the secondary functions.

# GPO0, GPO1

These are general-purpose output pins. The values set in CR17-B0 and CR17-B1 are output at these pins GPO0 and GPO1, respectively. Further, GPO0 becomes the output pin for the dial pulse generator (DPGEN) in the secondary functions.

#### CLKSEL

This is the input/output control input pin of SYNC and BCLK. The pin becomes input at "0" level and output at "1" level.

#### SYNC

This is the 8 kHz sync signal input/output pin of PCM signals. When CLKSEL is "0", input continuously an 8 kHz clock synchronous with BCLK. Further, when CLKSEL is "1", this pin outputs an 8 kHz clock synchronous with BCLK. Long frame synchronization is used when CR0-B1 (LONG/SHORT) is "0" and short frame synchronization is used when it is "1".

#### **BCLK**

This is the shift clock input/output pin for the PCM signal. When CLKSEL is "0", it is necessary to input to this pin a clock signal that is synchronous with SYNC. Input a 64 to 2048 kHz clock when the G.711 mode or the G.726 mode has been selected, and input a 128 to 2048 kHz clock when the 16-bit linear mode has been selected. When CLKSEL is "1", this pin outputs a clock that is synchronous with SYNC. This pin outputs a 64 kHz clock when the G.711 mode or the G.726 mode has been selected, and outputs an 128 kHz clock when the 16-bit linear mode or G.729.A mode has been selected.

Note: The input/output control and frequencies of the above SYNC and BLCK signals will be as shown in Table 1 below.

Table 1 Input/output control of SYNC and BCLK

| CLKSEL | SYNC              | BCLK                          | Remarks                                                                                                                                                                                    |

|--------|-------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "0"    | Input<br>(8 kHz)  | Input<br>(64 kHz to 2048 kHz) | Input a continuous clock after starting the power supply. Input a 64 to 2048 kHz clock when G.711 or G.726 is selected. Input a 128 to 2048 kHz clock when 16-bit linear mode is selected. |

| "1"    | Output<br>(8 kHz) | Output<br>(64 kHz or 128 kHz) | An "L" level is output during the power down mode. A 64 kHz clock is output when G.711 or G.726 is selected. A 128 kHz clock is output when G.729.A or 16-bit linear mode is selected.     |

#### PCMO

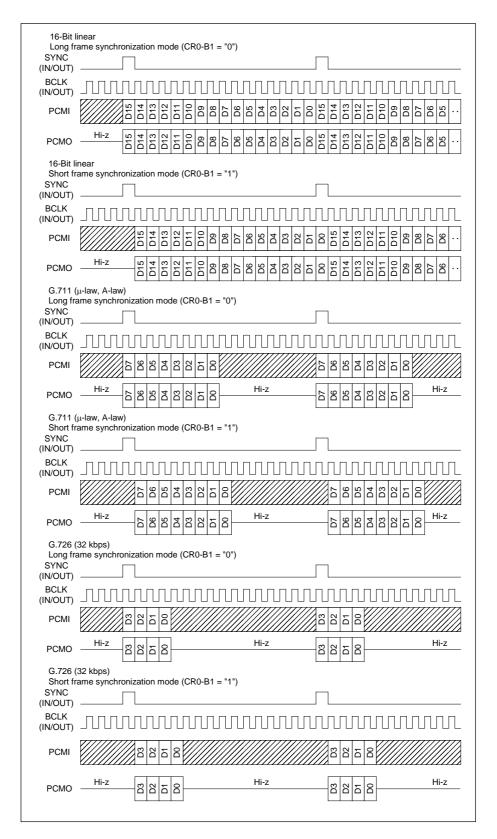

This is the PCM signal output pin for the transmitting section. The PCM signal is output in synchronization with the rising edges of SYNC and BCLK. The PCMO outputs the data only during the valid data segment in the selected coding format and goes to the high impedance state during all other segments. The basic timing chart of the PCM I/F mode is shown in Fig. 11. The PCMO output will be in the high impedance state when the mutual conversion function is not used (CR11-B0 = "0") or when the PCM I/F mode is not used (CR12-B0 = "0").

#### **PCMI**

This is the PCM signal input pin for the receiving section. The data is entered starting from the MSB by shift on the falling edge of BCLK.

The basic timing chart of the PCM I/F mode is shown in Fig. 11.

Fix input with "0" or "1" when the mutual conversion function is not used (CR11-B0 = "0") or when the PCM I/F mode (CR12-B0 = "0") is not used.

Fig. 11 PCM I/F mode timing diagram

# **FUNCTION DESCRIPTION**

# **Echo Canceller**

The block diagram of the echo canceller is shown in Fig. 39.

# **EXAMPLE OF CONFIGURATION**

# Analog I/F mode

Example of settings in the initialization mode

- $\cdot$  CR15 = 40h \* This is mandatory.

- · CR6=01h,CR7=16h,CR8=00h,CR9=01h,CR1=80h (Address: 0116h, Data: 0001h)

- \* This is mandatory. As for how to set them, refer to Method of Accessing and Controlling Internal Data Memory.

- $\cdot$  CR11 = 00h (Frame/10 ms/16B/Speech CODEC = G.729.A)

- · Various settings

- $\cdot$  CR0 = 09h (OPE\_STAT = "1")

# PCM I/F Mode

Examples of settings in the initialization mode

- $\cdot$  CR15 = 40h \* This is mandatory.

- · CR6=01h,CR7=16h,CR8=00h,CR9=01h,CR1=80h (Address: 0116h, Data: 0001h)

- \* This is mandatory. As for how to set them, refer to Method of Accessing and Controlling Internal Data Memory.

- $\cdot$  CR10 = 00h (VFRO1 = AVREF/VFRO0 = AVREF)

- $\cdot$  CR11 = 00h (Frame/10 ms/16B/PCMIF = 16-bit linear)

- $\cdot$  CR12 = 01h (Speech CODEC = G.729.A/PCMIF\_EN = "1")

- · Various settings

- $\cdot$  CR0 = 29h (AFE\_EN = Power down/LONG/OPE\_STAT = "1")

# G.729.A ↔ G.726 Mutual Conversion

Examples of settings in the initialization mode

- $\cdot$  CR15 = 40h \* This is mandatory.

- · CR6=01h,CR7=16h,CR8=00h,CR9=01h,CR1=80h (Address: 0116h, Data: 0001h)

- \* This is mandatory. As for how to set them, refer to Method of Accessing and Controlling Internal Data Memory.

- $\cdot$  CR11 = 05h (Frame/10 ms/16B/G.726/TRANS\_EN= "1")

- $\cdot$  CR10 = 00h (VFRO1 = AVREF/VFRO0 = AVREF)

- · Various settings

- $\cdot$  CR0 = 29h (AFE\_EN = Power down/LONG/OPE\_STAT = "1")

# **EXAMPLE OF APPLICATION CIRCUIT**

# PACKAGE DIMENSIONS

Notes for Mounting the Surface Mount Type Package

The surface mount type packages are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

# **REVISION HISTORY**

| Document            |               | Page                |                    |                 |

|---------------------|---------------|---------------------|--------------------|-----------------|

| No.                 | Date          | Previous<br>Edition | Current<br>Edition | Description     |

| FEDL7074-003FULL-01 | Oct. 27, 2003 | _                   | -                  | Final edition 1 |

# NOTICE

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

Copyright 2003 Oki Electric Industry Co., Ltd.