# 8932-A

#### **VOICE-COIL MOTOR DRIVER**

Providing control and drive of the voice-coil motor used for head positioning in 5 V disk drive applications, the second-generation A8932CLWA is a full-bridge driver that can be configured so that its output current is a direct function of an externally applied control voltage or current. This linear current control function is supplemented by additional circuitry to protect the heads and the data disk during system failure or normal system shutdown.

The two ±500 mA MOS driver outputs provide very low saturation voltage and minimal power dissipation. Additional headroom is achieved by the sense-FET structure eliminating the need for an external current-sense resistor. Internal circuitry can be configured to provide closed-loop velocity control of the actuator by utilizing the generated back-EMF of the voice-coil motor. Thermal protection and under-voltage lockout disables the system in a controlled sequence if a fault condition occurs.

#### **FEATURES**

- $\blacksquare$  Class-B, 2  $\Omega$   $\mathbf{r}_{DS(on)}$  at 500 mA Output

- Lossless Current Sensing

- Zero Current-Loop Deadband

- High Transconductance Bandwidth

- User-Adjustable Transconductance Gain

- Digital Transconductance Gain Switch (4:1 Ratio)

- 5 Volt Monitor with Selectable UV Trip Point

- Retract Circuitry Functional to 0 Volts

- Sleep Mode Function

- Internal Back-EMF Velocity Loop Option

- Internal Thermal Shutdown Circuitry

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltages, V <sub>CC</sub> and V <sub>DD</sub> <b>6.0 V</b> |

|-------------------------------------------------------------------|

| Output Current, I <sub>OUT</sub> (peak) ± <b>600 mA</b>           |

| (continuous) ±500 mA                                              |

| Analog Input Voltage Range,                                       |

| V <sub>IN</sub> 0.3 V to V <sub>CC</sub>                          |

| Logic Input Voltage Range,                                        |

| V <sub>IN</sub> 0.3 V to +6.0 V                                   |

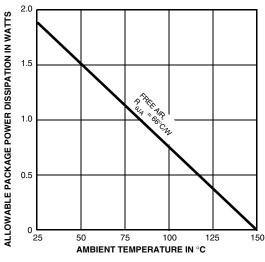

| Package Power Dissipation,                                        |

| P <sub>D</sub> See Graph                                          |

| Operating Temperature Range,                                      |

| T <sub>A</sub> 0°C to +70°C                                       |

| Junction Temperature, T <sub>J</sub> +150°C <sup>†</sup>          |

| Storage Temperature Range,                                        |

† Fault conditions that produce excessive junction temperature will activate device thermal shutdown circuitry. These conditions can be tolerated, but should be avoided.

T<sub>S</sub> ......-55°C to +150°C

Output current rating may be restricted to a value determined by system concerns and factors. These include: system duty cycle and timing, ambient temperature, and use of any heatsinking and/or forced cooling. For reliable operation the specified maximum junction temperature should not be exceeded.

Always order by complete part number, e.g., A8932CLWA.

Dwg. GP-034

# ELECTRICAL CHARACTERISTICS at T<sub>A</sub> = +25°C, V<sub>CC</sub> = V<sub>DD</sub> = 5.0 V, V<sub>REF</sub> = V<sub>IN</sub> = 2.0 V, Load = 150 $\mu$ H/3.5 $\Omega$ (unless otherwise noted).

|                              |                      |                                                                                   |          | Lin  | nits |       |  |

|------------------------------|----------------------|-----------------------------------------------------------------------------------|----------|------|------|-------|--|

| Characteristic               | Symbol               | Test Conditions                                                                   | Min.     | Тур. | Max. | Units |  |

| Error Amplifier              | •                    |                                                                                   | •        |      |      | •     |  |

| Input Offset Voltage         | V <sub>IO</sub>      | I <sub>LOAD</sub> = 0 mA                                                          | _        | _    | ±50  | mV    |  |

| Current Gain                 | A <sub>iH</sub>      | H GAIN ≥ 3.5 V                                                                    | 7200     | 8000 | 8800 | _     |  |

|                              | A <sub>iL</sub>      | H GAIN ≤ 0.7 V                                                                    | 1800     | 2000 | 2200 | _     |  |

| Current Gain Linearity       | E <sub>L(adj)</sub>  | $I_{OUT} = 5$ mA to 500 mA, $A_i = A_{iL}$                                        |          | _    | ±10  | %     |  |

|                              |                      | I <sub>OUT</sub> = 5 mA to 500 mA, A <sub>i</sub> = A <sub>iH</sub>               |          | _    | ±10  | %     |  |

| Reference Voltage Range      | V <sub>REF</sub>     |                                                                                   | 1.5      | _    | 2.5  | V     |  |

| Voltage-Sense Amplifier      | •                    |                                                                                   | <u>'</u> |      |      |       |  |

| Voltage Gain                 | A <sub>VD</sub>      |                                                                                   | 0.36     | 0.40 | 0.44 | _     |  |

| Output Offset Voltage        | V <sub>oo</sub>      | I <sub>LOAD</sub> = 0 mA                                                          |          | _    | ±25  | mV    |  |

| Current-Sense Amplifier      | •                    |                                                                                   | <u>'</u> |      |      |       |  |

| Amplifier Error              | E <sub>VD</sub>      | (R <sub>s</sub> x I <sub>LOAD</sub> / (A <sub>i</sub> x V <sub>SENSE</sub> )) - 1 |          | 1.0  | _    | _     |  |

| Input Offset Voltage         | V <sub>iO</sub>      | $I_{LOAD} = 0 \text{ mA}, A_i = A_{iL}$                                           |          | _    | ±25  | mV    |  |

| Output Drivers               | Output Drivers       |                                                                                   |          |      |      |       |  |

| Total On Resistance          | r <sub>DS(on)</sub>  | I <sub>LOAD</sub> = 100 mA                                                        |          | 2.0  | 2.5  | Ω     |  |

| (Source + Sink)              |                      | I <sub>LOAD</sub> = 500 mA                                                        | _        | 2.0  | 2.5  | Ω     |  |

| Retract Output Voltage Error | E <sub>OUT(PN)</sub> | V <sub>OUT(P)</sub> - V <sub>OUT(N)</sub> - V <sub>RETSET</sub>                   |          | _    | ±100 | mV    |  |

| Full Power Bandwidth         | BW                   | -3 dB                                                                             | 1.0      | _    | _    | kHz   |  |

| Uncommitted Op Amp           | •                    |                                                                                   | •        |      |      |       |  |

| Voltage Gain                 | A <sub>VS</sub>      |                                                                                   |          | 91   | _    | dB    |  |

| Unity Gain Bandwidth         | BW                   |                                                                                   | _        | 1.0  | _    | MHz   |  |

| Max. Load Capacitance        | C <sub>LOAD</sub>    |                                                                                   |          | 40   | _    | pF    |  |

| Slew Rate                    | SR                   |                                                                                   |          | 4.2  | _    | V/μs  |  |

| Output Voltage               | Vo                   | V <sub>SWITCH</sub> ≤ 0.7 V                                                       | 2.5      | _    | 3.5  | ٧     |  |

|                              | V <sub>OSW</sub>     | V <sub>SWITCH</sub> ≥ 3.5 V                                                       | 2.5      | _    | 3.5  | V     |  |

| Max. Output Current          | Io                   |                                                                                   | _        | ±250 | _    | μА    |  |

| Input Offset Voltage         | V <sub>IO</sub>      |                                                                                   |          | <±10 | _    | mV    |  |

Continued next page...

Negative current is defined as coming out of (sourcing) the specified device terminal.

Typical Data is for design information only.

# ELECTRICAL CHARACTERISTICS at T $_{\rm A}$ = +25°C, V $_{\rm CC}$ = V $_{\rm DD}$ = 5.0 V, V $_{\rm REF}$ = V $_{\rm IN}$ = 2.0 V, Load = 150 $\mu$ H/3.5 $\Omega$ (unless otherwise noted).

|                               |                                   |                                                            | Limits |      |      |       |

|-------------------------------|-----------------------------------|------------------------------------------------------------|--------|------|------|-------|

| Characteristic                | Symbol                            | Test Conditions                                            | Min.   | Тур. | Max. | Units |

| Miscellaneous                 |                                   |                                                            |        |      |      |       |

| Supply Voltage                | V <sub>CC</sub>                   | Operating                                                  | 4.5    | 5.0  | 5.5  | V     |

|                               | $V_{DD}$                          | Operating                                                  | 4.5    | 5.0  | 5.5  | V     |

| Under-Voltage Lockout Voltage | V <sub>CC</sub>                   | $V_{CC} = V_{DD}$                                          | 3.9    | 4.2  | 4.35 | V     |

| Fault Logic Output            | V <sub>FAULT</sub>                | V <sub>RETRACT</sub> ≥ 3.5 V                               | _      | _    | 500  | mV    |

|                               |                                   | V <sub>RETRACT</sub> ≤ 0.7 V                               | 4.5    | _    | _    | V     |

|                               | I <sub>FAULT</sub>                | V <sub>FLT</sub> = 2.25 V                                  | _      | >20  | _    | μΑ    |

| Power-On Reset                | V <sub>MPRESET</sub>              | V <sub>RETRACT</sub> ≥ 3.5 V                               | 4.5    | _    | _    | V     |

|                               |                                   | V <sub>RETRACT</sub> ≤ 0.7 V, I <sub>MPREST</sub> = 1.5 mA |        | _    | 800  | mV    |

| Total Supply Current          | I <sub>CC</sub> + I <sub>DD</sub> | Outputs Balanced, No Load                                  | _      | _    | 10   | mA    |

|                               |                                   | Sleep Mode, PWR OFF = V <sub>CC</sub>                      |        | _    | 2.0  | mA    |

| Logic Input Voltage           | V <sub>IN(0)</sub>                |                                                            |        | _    | 0.7  | V     |

|                               | V <sub>IN(1)</sub>                |                                                            | 3.5    |      |      | V     |

| Thermal Shutdown Temperature  | T <sub>J</sub>                    |                                                            |        | 165  |      | °C    |

| Thermal Shutdown Hysteresis   | $\DeltaT_J$                       |                                                            |        | 20   | _    | °C    |

Negative current is defined as coming out of (sourcing) the specified device terminal.

Typical Data is for design information only.

The products described here are manufactured under one or more U.S. patents or U.S. patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro products are not authorized for use as critical components in life-support devices or systems without express written approval.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

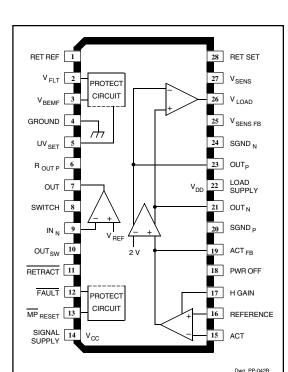

#### **TERMINAL FUNCTIONS**

| Term. | Terminal Name        | Function                                                                                                                                     |  |

|-------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1     | RET REF              | The reference supply for setting the voltage across the load during retract.                                                                 |  |

| 2     | $V_{FLT}$            | Reservoir (energy storage) capacitor used to operate fault circuitry.                                                                        |  |

| 3     | $V_{BEMF}$           | Back-EMF voltage from spindle motor used to retract heads during loss of power.                                                              |  |

| 4     | GROUND               | Circuit reference.                                                                                                                           |  |

| 5     | UV <sub>SET</sub>    | Under-voltage trip point reference input. Set internally to 4.2 V but may be overridden by external resistor divider. (Equation 4).          |  |

| 6     | R <sub>OUT P</sub>   | Source driver used for retract; externally connected to OUT <sub>P</sub> .                                                                   |  |

| 7     | OUT                  | Output of uncommitted operational amplifier.                                                                                                 |  |

| 8     | SWITCH               | Logic input for transmission gate; a high level connects OUT to OUT <sub>SW</sub> .                                                          |  |

| 9     | IN <sub>N</sub>      | Inverting input to uncommitted operational amplifier.                                                                                        |  |

| 10    | OUT <sub>SW</sub>    | Transmission-gated output of uncommitted operational amplifier.                                                                              |  |

| 11    | RETRACT              | An active-low logic input that initiates the retract sequence.                                                                               |  |

| 12    | FAULT                | A logic low at this MOS output indicates a thermal shutdown, under-voltage fault, or retract command.                                        |  |

| 13    | MP <sub>RESET</sub>  | (Power-On Reset) A logic low at this open-collector output may be used to reset the system on under-voltage fault or power on.               |  |

| 14    | SIGNAL SUPPLY        | V <sub>CC</sub> ; low-current supply voltage in the range of 4.5 V to 5.5 V.                                                                 |  |

| 15    | ACT                  | Input which controls the current in the load. Transconductance gain is set with an external resistor in series with this input (Equation 1). |  |

| 16    | REFERENCE            | V <sub>REF</sub> ; reference input for all amplifiers; ac ground.                                                                            |  |

| 17    | H GAIN               | Logic input to switch the error amplifier transconductance gain: LOW = 2000, HIGH = 8000.                                                    |  |

| 18    | PWR OFF              | An active-high logic input that puts the device in a "sleep mode". All fault circuitry remains active.                                       |  |

| 19    | ACT <sub>FB</sub>    | Input connection for feedback network which sets the error amplifier gain and bandwidth.                                                     |  |

| 20    | SGND <sub>P</sub>    | Power ground for the OUT <sub>P</sub> sink driver.                                                                                           |  |

| 21    | OUT <sub>N</sub>     | Power output. Sinks current when $V_{ACT} < V_{REF}$ .                                                                                       |  |

| 22    | LOAD SUPPLY          | V <sub>DD</sub> ; high-current supply voltage for the voice-coil motor.                                                                      |  |

| 23    | OUT <sub>P</sub>     | Power output. Sinks current when $V_{ACT} > V_{REF}$ .                                                                                       |  |

| 24    | SGND <sub>N</sub>    | Power ground for the OUT <sub>N</sub> sink driver.                                                                                           |  |

| 25    | V <sub>SENS FB</sub> | Input connection for feedback network which sets the current-sense amplifier gain and bandwidth. Also called gm SET.                         |  |

| 26    | $V_{LOAD}$           | An output voltage proportional to the load voltage. Used in conjunction with closed-loop velocity control.                                   |  |

| 27    | V <sub>SENS</sub>    | Voltage output representing load current (Equation 2). Also called MONITOR.                                                                  |  |

| 28    | RET SET              | An external resistor divider to set the retract voltage across the load. Used in conjunction with $V_{\text{RET-REF}}$ (Equation 3).         |  |

#### **DEVICE DESCRIPTION**

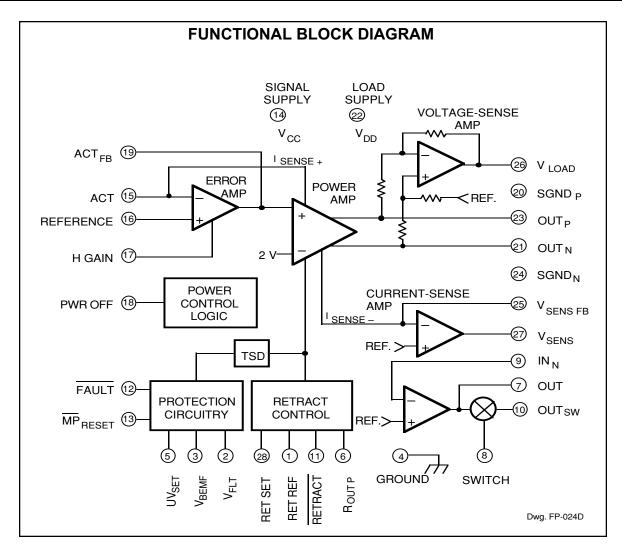

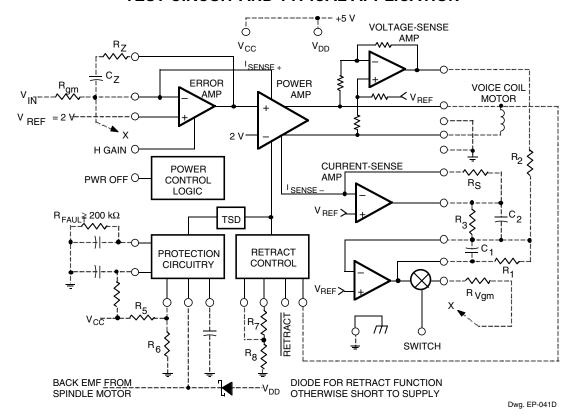

**Current Amplifier.** The A8932CLWA voice-coil motor driver features a wide transcon-ductance bandwidth and minimal crossover distortion. The transconductance gain is user selectable:

$$g_{m} = \frac{A_{i}}{R_{gm}}$$

(Equation 1)

where  $A_i$  is either 2000 (H GAIN = Low) or 8000 (H GAIN = High).

The error amplifier's bandwidth and load compensation zero are set utilizing external resistor and capacitor feedback components around the amplifier.

The actuator main loop compensation can be set by applying a square wave and adjusting  $\rm R_z$  and  $\rm C_z$  for optimum response.

**Current and Voltage Sensing.** The load current is sensed internally. Three auxiliary amplifiers are also included to allow various control functions to be implemented. The first of these amplifiers provides a voltage output that is proportional to the load current:

$$V_{SENSE} = \frac{R_S I_{LOAD}}{A_i}$$

(Equation 2)

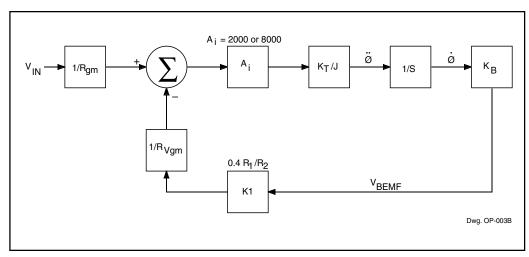

The second and third auxiliary amplifiers may be used in conjunction with the first to provide a closed-loop velocity control system for the actuator arm during a controlled retract for head parking. This is achieved by determining the back-EMF voltage generated by the voice coil and feeding back this information to the main actuator control input. The back-EMF feedback voltage can be switched in as required by means of the SWITCH logic input.

The back-EMF voltage represents the velocity of the actuator. By subtracting the  $I_{\tiny{LOAD}}R_{\tiny{LOAD}}$  voltage component from the voltage across the load, the back-EMF term can be isolated and fed back to close a velocity control loop.

The amplifier output voltage  $V_{\scriptscriptstyle LOAD}$  is proportional to the voltage across the load  $(A_{\scriptscriptstyle VD}[V_{\scriptscriptstyle OUTP}-V_{\scriptscriptstyle OUTP}])$ .  $R_{\scriptscriptstyle S}$  is selected so that  $V_{\scriptscriptstyle SENSE}$  represents  $I_{\scriptscriptstyle LOAD}$  while  $R_{\scriptscriptstyle 3}$  is dependent on  $R_{\scriptscriptstyle LOAD}$  as shown in the following equations:

$$V_{LOAD} = -A_{VD} ([I_{LOAD} R_{LOAD}] + V_{BEMF})$$

$$V_{SENSE} = R_{S} I_{LOAD} / A_{ii}$$

where  $A_i = 2000$  (H GAIN = logic Low)

$$OUT_{SW} = 0.4 (V_{BEMF} R_1/R_2)$$

$$R_3 = \frac{R_2 R_S}{0.4 A_i R_{1.0AD}}$$

$$\frac{V_{\text{BEMF}}}{V_{\text{IN}}} = \frac{R_2 R_{\text{Vgm}}}{0.4 R_{\text{qm}} R_1}$$

$$BW = 0.4 \frac{R_1 K_B K_T A_i}{2\pi R_{VGM} R_2 J}$$

where J is the moment of inertia,  $K_{\rm B}$  is the back-EMF motor constant, and  $K_{\rm T}$  is the torque constant.

Velocity loop compensation =  $L_{I,OAD}/R_{I,OAD} = R_1 C_1 = R_3 C_2$ .

**Retract and Brake.** A retract-brake sequence is initiated on receiving a fault indication from the internal thermal shutdown (TSD), or under-voltage lockout (UVLO), or an externally applied logic High at the RETRACT input.

If the velocity control scheme is implemented, the head can be retracted under the full control of  $V_{\rm IN}$  in conjunction with OUT $_{\rm SW}$  back-EMF voltage if no fault condition exists. If a fault condition were to occur however, the retract velocity would be controlled by applying a constant user-defined voltage across the load:

$$V_{RET-SET} = \frac{2 R_8}{1000 + R_7 + R_8}$$

(Equation 3)

where  $R_7 + R_8 >> 1000 \Omega$ .

When the sequence is operated, the output voltage is forced to approximately  $V_{\text{RET-SET}}$  to retract the heads, and then a fault command ("brake") is sent to the spindle motor driver. The user determines the total time for the retract sequence, before the spindle brake is enabled, by the choice of an external resistor and capacitor at the FAULT output.

Power for the retract function is provided by the rectified back EMF of the spindle motor by way of the V<sub>BEMF</sub> terminal. The A8932CLWA will perform the retract function under low supply conditions (nominally down to 2 V). Operation down to almost 0 V requires an energy-storage capacitor at the  $V_{\rm FLT}$  terminal.

**Protective Features.** The A8932CLWA has a number of protective features incorporated into the design. Undervoltage lockout provides system protection in the event of reduced primary supply voltages. The under-voltage trip point is internally set at approximately 4.2 V. It can be user-defined with an external resistor voltage divider:

$$UV_{TRIP} = \frac{2 (R_5 + R_6)}{R_6}$$

(Equation 4)

where  $R_5 + R_6 \ll 200 \text{ k}\Omega$ .

Thermal shutdown circuitry is included to protect the device from excessive junction temperature. It is only intended to protect the chip from catastrophic failures due to excessive junction temperature.

#### TEST CIRCUIT AND TYPICAL APPLICATION

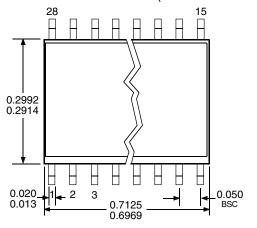

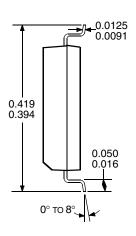

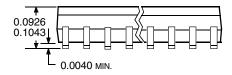

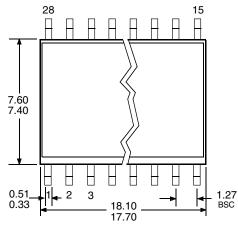

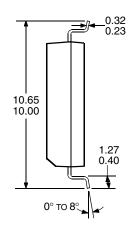

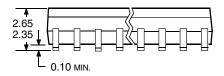

#### **Dimensions in Inches**

(for reference only)

Dwg. MA-008-28A in

#### **Dimensions in Millimeters**

(controlling dimensions)

Dwg. MA-008-28A mm

#### NOTES: 1. Lead spacing tolerance is non-cumulative.

- 2. Exact body and lead configuration at vendor's option within limits shown.

- 3. Supplied in standard sticks/tubes of 27 devices or add "TR" to part number for tape and reel.