#### **USB Charging Port Power Switch and Controller**

#### **Features**

- Meets Battery Charging Specification BC1.2 for DCP and CDP

- Meets Chinese Telecommunications Industry Standard YD/T 1591-2009

- Support Non-BC1.2 Charging Mode by Automatic Detection:

- Divider 1, 2 Supports Most Available Apple

Device

- 1.2V Mode Pull High Supports Samsung device

- Automatic SDP/CDP Swapping for BC1.2 noncompatible Devices That do not Recognize CDP Ports

- Supports Sleep Mode Charging and LS & HS HID (Mouse/Keyboard) Wake Up

- Load Detection for both Power Supply Control in S4/S5 Charging and Port Power Management in all Charge Modes

- 62mW Power Switch Meets USB2.0 & USB3.0

Power Switch Requirement

- VIN Operating Range: 4.5 ~ 5.5V

- Low Quiescent Current:

- <240mA When Device Enabled

- <2mA When Device Disabled

- High Bandwidth Data Switch Supports USB 2.0

- Adjustable Current Limit Up to 3.0A (typical)

- Output Discharge

- · UL Approved-File No.E328191

- TUV NORD IECEE CB Scheme Certified, No.DE 7-0364

- TUV NORD IEC 60950-1:2005+ A1:2009+ AE:2013 and/or EN 60950-1:2006+ A11:2009+ A1:2010+ A12:2011+ A2:2013 Certified, No.44 780 15 406747-008

- Lead Free and Green Devices (RoHS Compliant)

#### **General Description**

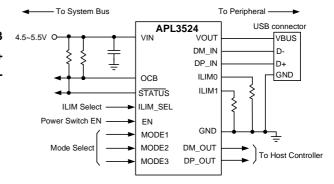

The APL3524 is an USB charging port controller which integrates USB 2.0 high-speed data line (D+/D-) switches and a power switch. The charging schemes comply with battery charging BC1.2 and Chinese Telecommunications Industry Standard YD/T 1591-2009.

The APL3524 also implements some dedicated charging schemes to support non-BC1.2 compatible device, such as divider1, divider2 mode or 1.2V shorted mode. The APL3524 features power wake and port power management (PPM) via STATUS pin in supporting power management. Power wake allows for power supply control in S4/S5 charging and PPM the ability to manage port power in a multi-port application. Furthermore, the APL3524 supports mouse/keyboard wake up from S3. The  $62m\Omega$  power switch with current limit and short circuit protections supports load current up to 2.5A. Two current limit thresholds set by two programming pin provide flexibility in current limit and load detection settings.

### **Applications**

- NB.

- · AIO PC

- USB Ports

- Universal Wall Charging Adapters

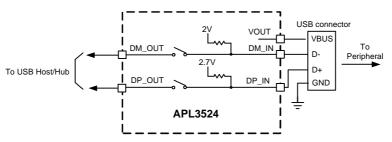

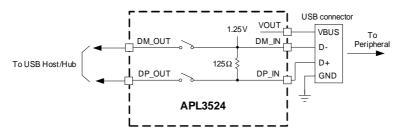

### **Simplified Application Circuit**

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise customers to obtain the latest version of relevant information to verify before placing orders.

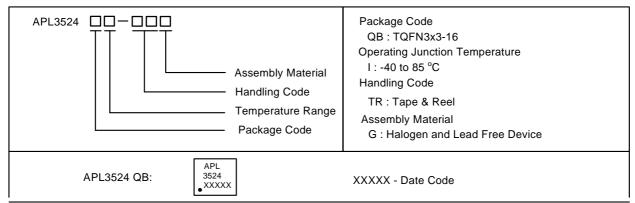

### **Ordering and Marking Information**

Note: ANPEC lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which are fully compliant with RoHS. ANPEC lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J-STD-020D for MSL classification at lead-free peak reflow temperature. ANPEC defines "Green" to mean lead-free (RoHS compliant) and halogen free (Br or Cl does not exceed 900ppm by weight in homogeneous material and total of Br and Cl does not exceed 1500ppm by weight).

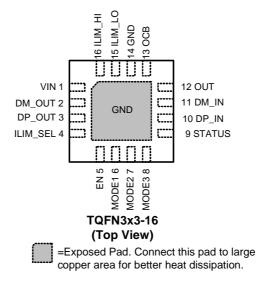

### **Pin Configuration**

### Absolute Maximum Ratings (Note 1)

| V <sub>VIN</sub> VIN Input Voltage (VIN to GND)                                                                                                                                                | -0.3~7             | V  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----|

| N N                                                                                                                                                                                            |                    | •  |

| $ \begin{vmatrix} V_{\text{EN}}, V_{\text{ILIM\_LO}}, \\ V_{\text{ILIM\_HI}}, \\ V_{\text{ILIM\_SEL}}, \\ V_{\text{MODE3}}, V_{\text{MODE2}}, \end{vmatrix}                                  $ | DDE3 to GND -0.3~7 | V  |

| V <sub>VOUT</sub> , V <sub>OCB</sub> VOUT, OCB, STATUS to GND Voltage                                                                                                                          | -0.3~7             | V  |

| V <sub>VIN-VOUT</sub> VIN to VOUT Voltage                                                                                                                                                      | -7~7               | V  |

| V <sub>DP_IN</sub> , V <sub>DM_IN</sub> , V <sub>DP_OUT</sub> , DP_IN, DM_IN, DP_OUT, DM_OUT to GND Voltage                                                                                    | -0.3~5.7           | V  |

| DP_IN, DM_IN, DP_OUT, DM_OUT Input Clamp Current                                                                                                                                               | -20~20             | mA |

| I <sub>DP_IN-DP_OUT</sub> , DP_IN to DP_OUT, DM_IN to DM_OUT Continuous Current In CDP Mode                                                                                                    | SDP or -100~100    | mA |

| I <sub>DP_IN-DM_IN</sub> DP_IN to DM_IN Current In BC1.2 DCP Mode                                                                                                                              | -35~35             | mA |

| I <sub>OUT</sub> Continuous Output Current                                                                                                                                                     | Internally Limited |    |

| I <sub>OCB</sub> OCB Continuous Sink Current                                                                                                                                                   | 25                 | mA |

| I <sub>ILIM_LO</sub> , I <sub>ILIM_HI</sub> ILIM_LO, ILIM_HI Continuous Source Current                                                                                                         | 1                  | mA |

| P <sub>D</sub> Continuous Total Power Dissipation                                                                                                                                              | Internally Limited |    |

| HMB ESD Rating, Human Body Model VIN, EN, ILIM_LO, ILIM_HI MODE1, MODE2, MODE3, N/C                                                                                                            |                    | kV |

| DP_IN, DM_IN, DP_OUT,                                                                                                                                                                          | DM_OUT 8           |    |

| CDM ESD Rating, Charged Device Model                                                                                                                                                           | 500                | V  |

| T <sub>J</sub> Junction Temperature                                                                                                                                                            | Internally Limited | °C |

| T <sub>STG</sub> Storage Temperature                                                                                                                                                           | -65 ~ 150          | °C |

| T <sub>SDR</sub> Maximum Lead Soldering Temperature(10 Seconds)                                                                                                                                | 260                | °C |

Note1: Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Thermal Characteristics**

| Symbol        | Parameter                                   | Typical Value | Unit |

|---------------|---------------------------------------------|---------------|------|

| $\theta_{JA}$ | Junction-to-Ambient Resistance in free air. | 55            | °C/W |

| θις           | Junction-to-Caset Resistance in free air.   | 10            | °C/W |

Note 2: 2 layered 5 in 2 printed circuit boards with 2oz trace and copper through several thermal vias. The thermal pad is soldered on the PCB.

Note 3: The case temperature is measured at the center of the exposed pad on the underside of the TQFN3x3-16 packages.

## **Recommended Operating Conditions (Note 4)**

| Symbol                                                                                                       | Parameter                                                              | Range      | Unit |

|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------------|------|

| V <sub>VIN</sub>                                                                                             | VIN Input Voltage (VIN to GND)                                         | 4.5 ~ 5.5  | V    |

| V <sub>EN</sub> , V <sub>ILIM_SEL</sub> ,<br>V <sub>MODE1</sub> , V <sub>MODE2</sub> ,<br>V <sub>MODE3</sub> | EN, ILIM_SEL, MODE1, MODE2, MODE3 to GND Input Voltage                 | 0 ~ 5.5    | V    |

| $\begin{matrix} V_{DP\_IN}, V_{DM\_IN}, \\ V_{DP\_OUT}, \\ V_{DM\_OUT} \end{matrix}$                         | DP_IN, DM_IN, DP_OUT, DM_OUT to GND Input Voltage                      | 0 ~ 5.5    | ٧    |

| I <sub>DP_IN-DP_OUT</sub> ,<br>I <sub>DM_IN-DM_OUT</sub>                                                     | DP_IN to DP_OUT, DM_IN to DM_OUT Continuous Current In SDP or CDP Mode | -30 ~ 30   | mA   |

| I <sub>DP_IN-DM_IN</sub>                                                                                     | DP_IN to DM_IN Current In BC1.2 DCP Mode                               | -10 ~ 10   | mA   |

| I <sub>OUT</sub>                                                                                             | Continuous Output Current                                              | 0 ~ 2.5    | Α    |

| $R_{\text{ILIM\_LO}}, R_{\text{ILIM\_HI}}$                                                                   | ILIM0, ILIM1 Set Resistors (ILIM_LO, ILIM_HI to GND)                   | 16.9 ~ 750 | kΩ   |

| TJ                                                                                                           | Operating Virtual Junction Temperature                                 | -40 ~ 125  | °C   |

Note 4: Refer to the typical application circuit.

### **Electrical Characteristics**

Unless otherwise specified, these specifications apply over  $V_{\text{IN}} = V_{\text{EN}} = 5\text{V}$ ,  $R_{\text{FAULT}} = 10\text{k}\Omega$ ,  $R_{\text{IILIM\_LO}} = 210\text{k}\Omega$ ,  $R_{\text{IILIM\_HI}} = 20\text{k}\Omega$ , MODE1=MODE2=low, MODE3=high, and  $T_{\text{A}} = -40$  to 85°C. Typical values are at  $T_{\text{A}} = 25$ °C.

| Cumbal                | Parameter                                | Test Conditions                                                                    |     | APL3524 |     | Unit |

|-----------------------|------------------------------------------|------------------------------------------------------------------------------------|-----|---------|-----|------|

| Symbol                | Parameter Test Conditions                |                                                                                    | Min | Тур     | Max | Unit |

| SUPPLY C              | CURRENT                                  |                                                                                    |     |         |     |      |

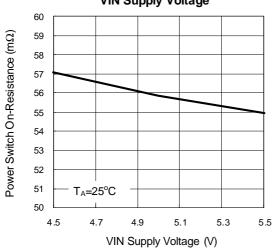

| I <sub>VIN</sub>      | VIN Supply Current                       | V <sub>EN</sub> =5V, T <sub>A</sub> =25 °C                                         | -   | 180     | 240 | μА   |

| I <sub>VIN_SD</sub>   | VIN Shutdown Supply Current              | V <sub>EN</sub> =0V, T <sub>A</sub> =25 °C                                         | -   | 0.1     | 2.0 | μА   |

| UNDER-VO              | OLTAGE LOCKOUT                           |                                                                                    |     |         |     |      |

| V <sub>UVLO</sub>     | VIN UVLO Threshold Voltage               | V <sub>IN</sub> rising                                                             | 3.9 | 4.1     | 4.3 | V    |

| V <sub>UVLO_HYS</sub> | VIN UVLO Threshold Voltage<br>Hysteresis | V <sub>IN</sub> falling                                                            | -   | 100     | -   | mV   |

|                       |                                          |                                                                                    |     |         |     |      |

| POWER S               | WITCH                                    |                                                                                    |     |         |     |      |

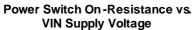

| В                     | Static Drain-Source On-state             | I <sub>OUT</sub> =2A, ILIM_SEL=high, T <sub>A</sub> = -40 to 85 °C                 | -   | 62      | 78  | mΩ   |

| R <sub>DS(on)</sub>   | Resistance                               | I <sub>OUT</sub> =2A, ILIM_SEL=low, T <sub>A</sub> = 25 °C                         | -   | 62      | 72  | mΩ   |

|                       | VOUT Rise Time                           | C <sub>OUT</sub> =1μF, R <sub>OUT</sub> =100Ω (V <sub>OUT</sub> 10-90%)            | 0.7 | 1       | 1.6 | ms   |

|                       | VOUT Fall Time                           | C <sub>OUT</sub> =1μF, R <sub>OUT</sub> =100Ω (V <sub>OUT</sub> 90-10%)            | 0.2 | -       | 0.5 | ms   |

|                       | Leakage Current                          | $V_{\text{IN}}$ =5.5V, $V_{\text{EN}}$ =0V, $T_{\text{J}}$ =25°C, VOUT tied to GND | -   | -       | 1   | μА   |

|                       | Reverse Leakage Current                  | $V_{OUT}$ =5.5V, $V_{EN}$ =0V, $T_J$ =25°C, VIN tied to GND                        | -   | -       | 1   | μА   |

### **Electrical Characteristics**

Unless otherwise specified, these specifications apply over  $V_{IN} = V_{EN} = 5V$ ,  $R_{FAULT} = 10k\Omega$ ,  $R_{IILIM\_LO} = 210k\Omega$ ,  $R_{IILIM\_HI} = 20k\Omega$ , MODE1=MODE2=MODE3=high, and  $T_A = -40$  to 85°C. Typical values are at  $T_A = 25$ °C.

| 0                     | Parameter Test Conditions                 |                                                                             |                              |      | AP L3 524 |      | 11 |

|-----------------------|-------------------------------------------|-----------------------------------------------------------------------------|------------------------------|------|-----------|------|----|

| Symbol                | Parameter                                 | Min                                                                         | Тур                          | Max  | Unit      |      |    |

| CURRENT               | LIMIT                                     |                                                                             |                              |      |           |      |    |

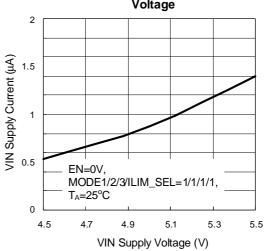

|                       | ILIM_SEL Logic Input Threshold            | V <sub>ILIM_SEL</sub> rising                                                |                              | 1.1  | 1.3       | 1.85 | V  |

|                       | ILIM_SEL Logic Threshold<br>Hysteresis    | V <sub>ILIM_SEL</sub> falling                                               |                              | -    | 200       | -    | mV |

|                       | ILIM_SELInput Current                     | V <sub>ILIM_SEL</sub> =0V or 5.5V                                           |                              | -0.5 | -         | 0.5  | μΑ |

|                       |                                           |                                                                             | $R_{LIM\_LO}=210k\Omega$     | 205  | 240       | -    |    |

|                       |                                           | ILIM_SEL=low, VOUT short to ground.                                         | $R_{LM\_LO}=80.6k\Omega$     | 575  | 625       | -    |    |

| I <sub>LIM</sub>      | Current Limit Threshold                   | Voor short to ground.                                                       | R <sub>LM_LO</sub> =22.1kΩ   | 2120 | 2275      | -    | mA |

|                       |                                           | ILIM_SEL=high,                                                              | R <sub>LIM_H</sub> =20kΩ     | 2340 | 2510      | -    |    |

|                       |                                           | VOUT short to ground.                                                       | R <sub>LIM_H</sub> =16.9kΩ   | 2770 | 2970      | -    |    |

|                       | Response Time to Short Circuit            | I <sub>OUT</sub> slew rate=20A/μs                                           | R <sub>LIM_XX</sub> =20kΩ    | -    | 1         | -    | μs |

| ENABLE,               | OUTPUT DISCHARGE                          |                                                                             |                              |      |           |      |    |

| V <sub>EN_TH</sub>    | EN Logic Input Threshold                  |                                                                             |                              | 1.1  | 1.3       | 1.85 | V  |

|                       | EN Logic Input Threshold<br>Hysteresis    |                                                                             |                              | -    | 200       | -    | mV |

|                       | EN Input Current                          | V <sub>EN</sub> =0 or 5.5 V                                                 |                              | -0.5 | -         | 0.5  | μА |

|                       | Turn-on Time                              | $C_{OUT} = 1 \mu F$ , $R_{OUT} = 100 \Omega$ , $V_E$ 90% $V_{OUT}$          | <sub>EN</sub> rising edge to | -    | -         | 11   | ms |

|                       | Turn-off Time                             | $C_{OUT}$ =1 $\mu$ F, $R_{OUT}$ =100 $\Omega$ , $V_{EN}$ 10% $V_{OUT}$      | fallng edge to               | -    | 1.7       | 3    | ms |

|                       | VOUT Discharge Resistance                 | V <sub>OUT</sub> =4V, V <sub>EN</sub> =0V                                   | 400                          | 500  | 630       | Ω    |    |

| t <sub>DCHG</sub>     | VOUT Discharge Hold Time                  | Time start to count when V <sub>OUT</sub> falls below 0.8 V during DCH mode |                              | 1.3  | 2         | 2.9  | s  |

| ОСВ                   |                                           |                                                                             |                              |      |           |      |    |

|                       | OCB Output Low Voltage                    | I <sub>OCB</sub> =1mA                                                       |                              | -    | 1         | 100  | mV |

|                       | Off-state Leakage                         |                                                                             |                              | -    | -         | 1    | μА |

| t <sub>D(OCB)</sub>   | OCB Deglitch Time                         |                                                                             |                              | 5    | 8.2       | 12   | ms |

| MODE1, M              | ODE2, MODE3 Inputs                        |                                                                             |                              |      |           |      |    |

| $V_{\text{MODE\_TH}}$ | MODEx Logic Input Threshold               | V <sub>MODEx</sub> rising                                                   |                              | 1.1  | 1.3       | 1.85 | V  |

|                       | MODEx Logic Input Threshold<br>Hysteresis | V <sub>MODEx</sub> falling                                                  |                              | -    | 200       | -    | mV |

|                       | MODEx Input Current                       | V <sub>MODEx</sub> =0 or 5.5V                                               | -0.5                         | -    | 0.5       | μА   |    |

## **Electrical Characteristics**

Unless otherwise specified, these specifications apply over V $_{\rm IN}=$ V $_{\rm EN}=$ 5V, R $_{\rm FAULT}=$ 10k $\Omega$ , R $_{\rm IILIM\_LO}=$ 210k $\Omega$ , R $_{\rm IILIM\_HI}=$ 20k $\Omega$ , MODE1=MODE2=low, MODE3=high, and T $_{\rm A}=$  -40 to 85°C. Typical values are at T $_{\rm A}=$ 25°C.

| Symbol                 | Baramatar                                                                                | Tost Conditions                                                                                                                                                                                                                      |      | APL3524 |      | Unit |

|------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|------|------|

| Symbol                 | Parameter                                                                                | Test Conditions                                                                                                                                                                                                                      | Min  | Тур     | Max  | Unit |

| THERMAL                | SHUTDOWN                                                                                 |                                                                                                                                                                                                                                      | •    | •       |      |      |

|                        | Thermal Shutdown Threshold                                                               |                                                                                                                                                                                                                                      | 130  | 140     | 150  | °C   |

|                        | Thermal Shutdown Threshold<br>Hysteresis                                                 |                                                                                                                                                                                                                                      | -    | 20      | -    | °C   |

| HIGH BAN               | IDWIDTH ANALOG SWITCH                                                                    |                                                                                                                                                                                                                                      |      |         |      |      |

| R <sub>HS_ON</sub>     | DP, DM High Speed Switch On                                                              | V <sub>DP/DM_OUT</sub> =0V, I <sub>DP/DM_OUT</sub> =+30mA                                                                                                                                                                            | -    | 2       | 4    | Ω    |

| THS_ON                 | Resistance                                                                               | $V_{DP/DM\_OUT}$ =2.4V, $I_{DP/DM\_OUT}$ =-15mA                                                                                                                                                                                      | -    | 3       | 6    | Ω    |

|                        | On Resistance Match Between                                                              | V <sub>DP/DM_OUT</sub> =0V, I <sub>DP/DM_OUT</sub> =+30mA                                                                                                                                                                            | -    | 0.05    | 0.15 | Ω    |

|                        | Channels DP/DM Switch                                                                    | V <sub>DP/DM_OUT</sub> =0V, I <sub>DP/DM_OUT</sub> =+30mA                                                                                                                                                                            | -    | 0.05    | 0.15 | Ω    |

|                        | DM/DP Off State Capacitance                                                              | $V_{EN}$ =0V, $V_{DP/DM\_IN}$ =0.3V, $V_{AC}$ =0.6 $V_{PK-PK}$ , f=1MHz                                                                                                                                                              | -    | 3       | -    | pF   |

|                        | DM/DP On State Capacitance                                                               | V <sub>DP/DM_IN</sub> =0.3V, V <sub>AC</sub> =0.6V <sub>PK-PK</sub> , f=1MHz,                                                                                                                                                        | -    | 5.4     | -    | pF   |

|                        | Off State Isolation                                                                      | $V_{\text{EN}}$ =0V, $R_{\text{L}}$ =50 $\Omega$ , f=250MHz, $T_{\text{A}}$ = -40 to 125 $^{\circ}$ C                                                                                                                                | -    | 33      | -    | dB   |

|                        | On State Cross Channel Isolation                                                         | R <sub>L</sub> =50 $\Omega$ , f=250MHz, T <sub>A</sub> = -40 to 125 $^{\circ}$ C                                                                                                                                                     | -    | 52      | -    | dB   |

|                        | Off State Leakage                                                                        | $\begin{array}{c} V_{\text{EN}}=0\text{V},  V_{\text{DM\_IN}}=V_{\text{DP\_IN}}=3.6\text{V}, \\ V_{\text{DM\_OUT}}=V_{\text{DP\_OUT}}=0\text{V}, \text{ measure } I_{\text{DM\_OUT}} \text{ and } \\ I_{\text{DP\_OUT}} \end{array}$ | -    | 0.1     | 1.5  | μА   |

|                        | Bandwidth (-3dB)                                                                         | $R_L=50\Omega$                                                                                                                                                                                                                       | -    | 2.6     | -    | GHz  |

|                        | Propagation Delay                                                                        |                                                                                                                                                                                                                                      | -    | 0.25    | -    |      |

|                        | Skew Between Opposite Transitions Of The Same Port (t <sub>PHL</sub> -t <sub>PLH</sub> ) |                                                                                                                                                                                                                                      | -    | 0.1     | -    | ns   |

| DCP SHO                | RTED MODE CHARGER INTERFAC                                                               | CE                                                                                                                                                                                                                                   | •    | •       | •    |      |

| R <sub>DPM_SHORT</sub> | DP_IN/DM_IN Shorting Resistance                                                          | MODEx configured for DCP BC1.2                                                                                                                                                                                                       | -    | 125     | 200  | Ω    |

| DIVIDER I              | MODE CHARGER INTERFACE                                                                   |                                                                                                                                                                                                                                      | 1    | •       |      |      |

| $V_{DP\_AM}$           | DP_IN Output Voltage in Divider 1                                                        |                                                                                                                                                                                                                                      | 1.9  | 2       | 2.1  | V    |

|                        | DP_IN Output Voltage in Divider 2                                                        |                                                                                                                                                                                                                                      | 2.57 | 2.7     | 2.84 | V    |

| $V_{DM\_AM}$           | DM_IN Output Voltage Divider 1                                                           | 1,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                                                                                                                                                                              | 2.57 | 2.7     | 2.84 | V    |

|                        | DM_IN Output Voltage Divider 2                                                           | MODEx configured for divider mode                                                                                                                                                                                                    | 1.9  | 2       | 2.1  | V    |

| Z <sub>OUT_DP</sub>    | DP_IN Output Impedance                                                                   |                                                                                                                                                                                                                                      | 8    | 10.5    | 12.5 | kΩ   |

| Z <sub>OUT_DM</sub>    | DM_IN Output Impedance                                                                   |                                                                                                                                                                                                                                      | 8    | 10.5    | 12.5 | kΩ   |

| 1.2V Mode              | 9                                                                                        |                                                                                                                                                                                                                                      |      |         |      |      |

|                        | DP_IN/DM_IN Output Voltage                                                               |                                                                                                                                                                                                                                      | 1.19 | 1.25    | 1.31 | V    |

|                        | DP_IN/DM_IN Output Impedance                                                             |                                                                                                                                                                                                                                      | 60   | 75      | 94   | kΩ   |

|                        | 1                                                                                        | l .                                                                                                                                                                                                                                  | 1    |         |      |      |

### **Electrical Characteristics**

Unless otherwise specified, these specifications apply over  $V_{\text{IN}} = V_{\text{EN}} = 5\text{V}$ ,  $R_{\text{FAULT}} = 10\text{k}\Omega$ ,  $R_{\text{IILIM\_LO}} = 210\text{k}\Omega$ ,  $R_{\text{IILIM\_HI}} = 20\text{k}\Omega$ , MODE1=MODE2=low, MODE3=high, and  $T_{\text{A}} = -40$  to 85°C. Typical values are at  $T_{\text{A}} = 25$ °C.

| Symbol               | <b>5</b>                                                                 | T O 177                                            |      | Unit                     |      |      |

|----------------------|--------------------------------------------------------------------------|----------------------------------------------------|------|--------------------------|------|------|

| Symbol               | Parameter                                                                | Test Conditions                                    | Min  | Тур                      | Max  | Unit |

| CDP Inter            | face                                                                     |                                                    | •    | •                        |      |      |

| V <sub>DM_SRC</sub>  | Voltage Source On DM_IN for CDP Detect                                   | V <sub>DP_IN</sub> =0.6V, MODEx configured for CDP | 0.5  | 0.6                      | 0.7  | V    |

| $V_{DAT\_REF}$       | DP_IN Rising Voltage Threshold<br>To Activate V <sub>DM_SRC</sub>        | V <sub>DP_IN</sub> =0.6V, MODEx configured for CDP | 0.25 | -                        | 0.4  | V    |

|                      | V <sub>DAT_REF</sub> Hysteresis                                          |                                                    |      | 50                       |      | mV   |

| $V_{LGC\_SRC}$       | DP_IN Rising Voltage Threshold<br>To Deactivate V <sub>DM_SRC</sub>      |                                                    | 0.8  | -                        | 1    | V    |

|                      | V <sub>LGC_SRC</sub> Hysteresis                                          |                                                    | -    | 100                      | -    | mV   |

| I <sub>DP_SINK</sub> | DP_IN Sink Current                                                       | V <sub>DP_IN</sub> = 0.4~0.8V,                     | 40   | 70                       | 100  | uA   |

| LOAD DE              | TECTION- PORT POWER MANAGE                                               | EMENT                                              | •    |                          |      |      |

|                      | I <sub>OUT</sub> Rising Load Detection Current Threshold                 |                                                    | -    | I <sub>ILIM_LO</sub> +60 | -    | mA   |

|                      | I <sub>OUT</sub> rising load detection current threshold Hyeteresis      |                                                    | -    | 50                       | -    | mA   |

|                      | Load Detection Set Time                                                  |                                                    | 140  | 200                      | 275  | ms   |

|                      | Load Detection Reset Time                                                |                                                    | 1.9  | 3                        | 4.2  | S    |

| LOAD DE              | TECTION-POWER WAKE                                                       |                                                    | •    | •                        |      |      |

|                      | Power Wale Short Circuit Current<br>Limit                                |                                                    | -    | 55                       | -    | mA   |

|                      | I <sub>OUT</sub> Falling Power Wake Reset<br>Current Detection Threshold |                                                    | 23   | 45                       | 67   | mA   |

| •                    | Power Wake Reset Time                                                    |                                                    | 10.7 | 15                       | 20.6 | s    |

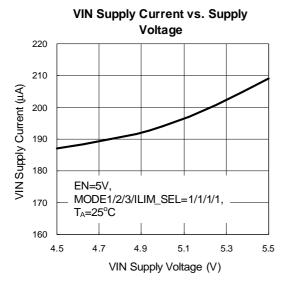

## **Typical Operating Characteristics**

### VIN Supply Current vs. Supply Voltage

# Control Logic Input Threshold Voltage vs. VIN Supply Voltage

### **Operating Waveforms**

The test condition is  $V_{IN}$ =5V,  $T_A$ = 25°C unless otherwise specified.

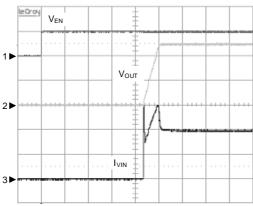

#### **Turn On Response**

$\begin{array}{l} V_{\text{IN}}\!=\!\!5\text{V}, \ R_{\text{LOAD}}\!=\!\!5\Omega, \ C_{\text{IN}}\!=\!\!4.7\text{uF/MLCC}, \ C_{\text{OUT}} \\ =\!150\mu\text{F/Electrolytic} \,, \end{array}$

CH1: V<sub>EN</sub>, 5V/Div, DC CH2: V<sub>OUT</sub>, 2V/Div, DC CH3: I<sub>VIN</sub>, 500mA/Div, DC

TIME: 2ms/Div

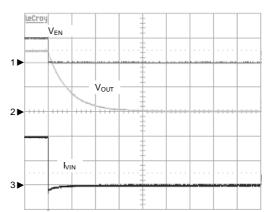

#### **Turn Off Response**

$V_{\text{IN}}$ =5V,  $R_{\text{LOAD}}$ =5 $\Omega$ ,  $C_{\text{IN}}$ =4.7uF/MLCC,  $C_{\text{OUT}}$ =150 $\mu$ F/Electrolytic ,

CH1: V<sub>EN</sub>, 5V/Div, DC CH2: V<sub>OUT</sub>, 2V/Div, DC CH3: I<sub>VIN</sub>, 500mA/Div, DC

TIME: 1ms/Div

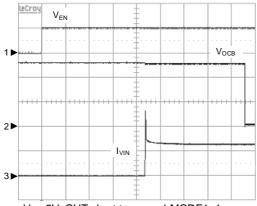

#### **Device Enabled into Short Circuit**

$V_{\text{IN}}$  =5V, OUT short to ground MODE1=1, MODE2=1, MODE3=1, ILIM\_SEL=0,

$R_{ILIM\_LO}=80.6k\Omega$

CH1:  $V_{EN}$ , 5V/Div, DC CH2:  $V_{CCB}$ , 2V/Div, DC CH3:  $I_{VIN}$ , 0.5A/Div, DC TIME:2ms/Div

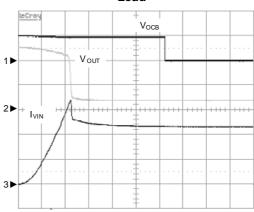

# OCB Response with Ramped Load

V<sub>IN</sub>=5V, MODE1=1, MODE2=1, MODE3=1,

ILIM\_SEL=1,  $R_{ILIM\_LO}$ =20 $k\Omega$

CH1: V<sub>CCB</sub>, 5V/Div, DC CH2: V<sub>CUT</sub>, 2V/Div, DC CH3: I<sub>VIN</sub>, 1A/Div, DC TIME:2ms/Div

## **Pin Description**

| F   | PIN      | FUNCTION                                                                                                                                                               |  |  |  |  |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NO. | NAME     | FUNCTION                                                                                                                                                               |  |  |  |  |

| 1   | VIN      | Input Voltage. Connect a 0.1μF or greater ceramic capacitor from VIN to GND as close to the device as possible                                                         |  |  |  |  |

| 2   | DM_OUT   | D- data line output. Connect this pin to USB host controller.                                                                                                          |  |  |  |  |

| 3   | DP_OUT   | D+ data line output. Connect this pin to USB host controller.                                                                                                          |  |  |  |  |

| 4   | ILIM_SEL | Logic-level input signal used to dynamically charge power switch current limit threshold; logic low selects ILIM0, logic high selects ILIM1.                           |  |  |  |  |

| 5   | EN       | Logic-level control input for turning the pow er switch and the signal switches on/off. When EN is low, the device is disabled, the signal and power switches are off. |  |  |  |  |

| 6   | MODE1    |                                                                                                                                                                        |  |  |  |  |

| 7   | MODE2    | Logic-level control inputs for controlling the charging mode and signal sw itches.                                                                                     |  |  |  |  |

| 8   | MODE3    |                                                                                                                                                                        |  |  |  |  |

| 9   | STATUS   | Active-low open drain output, asserted in load detection conditions.                                                                                                   |  |  |  |  |

| 10  | DP_IN    | D+ data line input. Connect this pin to USB peripheral.                                                                                                                |  |  |  |  |

| 11  | DM_IN    | D- data line input. Connect this pin to USB peripheral.                                                                                                                |  |  |  |  |

| 12  | OUT      | Pow er sw itch output.                                                                                                                                                 |  |  |  |  |

| 13  | OCB      | An active-low open-drain output for over current events indication, asserted during over-temperature or current limit conditions.                                      |  |  |  |  |

| 14  | GND      | Ground.                                                                                                                                                                |  |  |  |  |

| 15  | ILIM_LO  | An external resistor from this pin to ground sets the current limit threshold, recommended 16.9k $\Omega \le R_{LM} \le 750 k_{\Omega}$ .                              |  |  |  |  |

| 16  | ILIM_HI  | An external resistor from this pin to ground sets the current limit threshold; recommended $16.9k_{\Omega} \le R_{\text{LIM}} \le 750k_{\Omega}$ .                     |  |  |  |  |

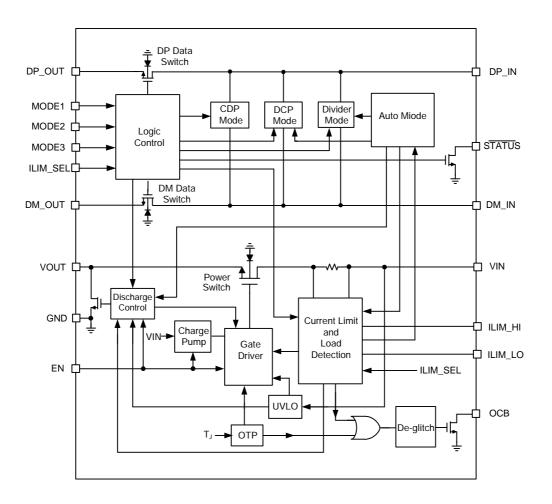

## **Block Diagram**

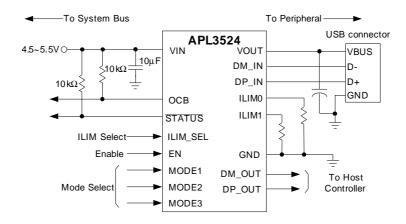

## **Typical Application Circuit**

#### Overview

As the USB ports on PC become popular for exchanging data between host and portable peripherals they become convenient places for replenishing portable devices' batteries. Many of these portable devices are with high ampere-hour batteries and thus need higher charging rate for recharging. However, not every USB port can support sufficient current for charging. In a traditional USB2.0 port, the current from it is not allowed to exceed 500mA after being enumerated. The USB3.0 port raises its supporting current to 900mA to downstream device after being enumerated. A mere 500mA or 900mA may not be adequate for charging batteries of many portable devices of nowadays. The success of USB has made the mini-USB a popular choice for wall adapter cables. A wall adapter can support current higher than 500mA/900mA. Since the USB2.0/3.0 constrains the USB port supporting current, some standards such as Battery Charging Specification Revision 1.2 (BC1.2) and Chinese Telecommunications Industry Standard YD/T 1591-2009 define some hand-shaking protocols that permit hosts and peripherals to draw current exceeding 500mA/900mA in charging. Some portable device maker such as Apple or Samsung has its own proprietary charging schemes to break the current barrier that USB2.0/3.0 has defined. The APL3524 are compliant with BC1.2 and YD/T 1591-2009 while supports most of the devices from Samsung and Apple. BC1.2 lists three different port types as listed below:

- 1. Standard Downstream Port

- 2. Charging Downstream Port

- 3. Dedicated Charging Port

BC1.2 defines a charging port as a downstream facing USB port that provides power for charging portable equipment, under this definition CDP and DCP are defined as charging ports

#### **Standard Downstream Port**

A Standard Downstream Port (SDP) is a traditional USB port that complies with the USB2.0/3.0 definition of a host or hub. An SDP expects a downstream device with a good battery to draw current up to 500mA/900mA (USB2.0/USB3.0) per port. In a SDP, USB traffic is allowed while battery charging can be in progress. The APL3524 supports SDP mode when control pins (MODE1~MODE3) are configured in SDP mode.

#### **Charging Downstream Port**

A Charging Downstream Port (CDP) is defined by USB BC1.2 and is USB 2.0/3.0 complied except that it shall support charging current up to 1.5A per port. The difference between CDP and SDP is the hand-shaking logic that follows BC1. 2. The handshaking of CDP is done in two steps. During the step one the DM\_IN outputs a voltage of V<sub>DM\_SRC</sub> when DP\_IN senses a voltage from peripheral greater than V<sub>DAT\_REF</sub> but less that V<sub>LGC\_SRC</sub>. When the step one is done. The peripheral concludes it is connected to a CDP or DCP port rather than SDP and goes for step two. In the step two, the peripheral determines if it is connected to a CDP or DCP by outputting a nominal 0.6V voltage on DM\_IN. The peripheral concludes it is a CDP port if it receives the voltage on DP\_IN is less than the nominal 0.3V and a DCP port if it receives the voltage on DP\_IN is greater than the nominal 0.3V. The APL3524 supports CDP mode when control pins (MODE1~MODE3) are configured in CDP mode.

#### **Dedicated Charging Port**

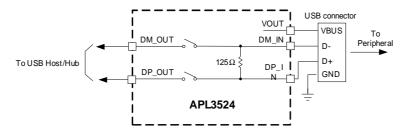

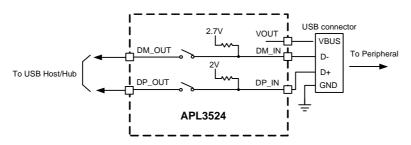

A Dedicated Charging Port (DCP) is as its name's implication that provides power for battery charging but does not support USB data communication to an upstream port. The APL3524 emulates a DCP in some charging modes: DCP Shorted, DCP Divider1 and DCP Auto. In DCP Shorted mode, the APL3524 short the DP\_IN with DM\_IN via a shorting resistor 125Ω which meets BC1.2 and Chinese Telecommunications Industry Standard YD/T 1591-2009. In DCP Divider1, the APL3524 outputs 2V and 2.7V respectively on the DP\_IN pin and DM\_IN pin. The DCP Divider1 is compliant with Apple device such as iPod and iPhone. In DCP Auto mode, the APL3524 conditionally switches modes between DCP shorted, DCP Divider1, DCP Divider2 and 1.2V mode, to support non-BC1.2 devices. When MODE1~MODE3 are configured in DCP Auto mode, it starts in Divider1 mode, however if a BC1.2/ YD/T 1591-2009 compliant is attached, the APL3524 responds by discharging OUT, turning back on the power switch and operating in 1.2V mode for a fixed period and then moving to DCP Shorted mode, it then stays in that mode until the device releases the data line, in which case it goes back to Divider1 mode. When a Divider1 compliant device is attached in DCP Auto mode, the APL3524 will stay in Divider1 mode. When a Divider2 compliant device is attached in DCP Auto mode, the APL3524 will transfer to Divider2 mode until the attached device is unattached. In Divider2, the APL3524 outputs 2.7V and 2V respectively on the DP\_IN pin and DM\_IN pin.

Figure 1. DCP Shorted mode

Figure 2. Divider1 mode

Figure 3. Divider2 mode

Figure 4. 1.2V mode

#### **High Bandwidth Data Line Switches**

The APL3524 integrates D+ and D- data lines switches for passing through data between host and peripherals without corrupting signal integrity in CDP or SDP mode. The data line switches support USB2.0 communication only. In the case of USB3.0 bus, please connect the data line directly between host and USB connector without passing through the APL3524. The data line switches operate based on these following criteria:

- 1. In any of SDP or CDP mode, the data switches are ON.

- 2. The data switches are OFF when EN or MODE1~ MODE3 are held low.

- 3. If current limit occurs in power switch, the data switches are still ON.

- 4. Data switches are OFF when power switch is in discharge state.

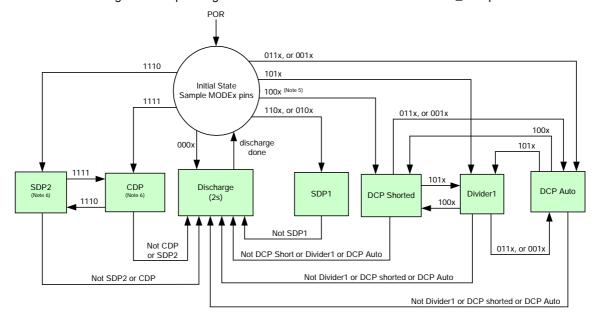

#### **Charging Mode Flow Diagram**

Below is a diagram that depicts how the APL3524 transfer charging states. Following a POR, the APL3524 enters initial state and will change state depending on the status of MODE1~ MODE3 and ILIM\_SEL pins.

Note 5: The numbers on each flow line represent the status of MODE1~ MODE 3 and ILIM\_SEL accordingly. Having "100x" for example, the first position "1" means MODE1=1, the second position "0" means MODE2=0, likewise, the third position "0" means the MODE3=0, and the forth position "x" means ILIMSEL=don't care. Please see below table for each flow line condition corresponding to charging mode.

Note 6: No OUT discharge when changing between 1111 and 1110.

|        | Flow Line | e Condition | Charging Mode |                                         |

|--------|-----------|-------------|---------------|-----------------------------------------|

| M ODE1 | M ODE2    | MODE3       | ILIM_SEL      | Charging wode                           |

| 0      | 0         | 0           | х             | Discharge                               |

| 1      | 1         | 1           | 1             | CDP                                     |

| 1      | 1         | 1           | 0             | SDP2<br>(no discharge from/to CDP)      |

| 1      | 1         | 0           | х             | SDP1<br>(discharge from/to any charging |

| 0      | 1         | 0           | х             | mode including CDP)                     |

| 1      | 0         | 0           | х             | DCP Shorted                             |

| 1      | 0         | 1           | х             | Divider1                                |

| 0      | 1         | 1           | х             | DCP Auto                                |

| 0      | 0         | 1           | х             | 20. Nuto                                |

#### Wake on USB

When system is placed in sleeping mode, or S3 mode, the data line switches are presumably put into OFF state. However, conveying wake-up signals from a low or full speed HID (human interface device like mouse/keyboard) in system sleeping state requires data lines to be connected to the host. The following MODEx changes support Wake on USB. When MODEx pins are configured in CDP or SDP the APL3524 monitors both DM\_IN and DP\_IN pin for detecting LS or FS HID device attachment. If a LS or FS HID device is attached while one of the following MODEx changes occurs, the data line switches will be continuously connected even in DCP Auto mode until they are used to wake the system.

- 1. MODE1/2/3=1/1/1 (CDP/SDP2, while system in S0) to 0/1/1 (DCP Auto, while system in S3)

- 2. MODE1/2/3=0/1/0 (SDP1, while system in S0) to 0/1/1 (DCP Auto, while system in S3)

#### **Truth Table**

The Truth Table lists all combinations for all control pins MODEx and ILIM\_SEL and their corresponding charging mode. Note that the current limit setting governed by the resistor on ILIM\_LO or ILIM\_HI or by the internal load detection threshold may change as mode changes. The column "System globe power state" provides suggestions to system designers on how to configure charging modes per system global power states(S0~S5). The power states listed in below table are suggestions rather than restrictions. System designer may have any match of charging mode and system power state. Since the APL3524 is unconscious of system global power states, the match with power state relies on system designer by routing MODEx and ILIM\_SEL with system power state control signals. For example when system is in S0 state then set MODEx and ILIM\_SEL to correspond to SDP or CDP mode. If charging is desired when system is in S3 or S4 state then system designer must set MODEx and ILIM\_SEL to correspond to DCP Auto per below table and so on.

| MODE1 | MODE2 | MODE3 | ILIM_SEL | Mode           | Current limit<br>setting refers<br>to | STATUS Output<br>(Active Low)         | Comment                                                              | System global<br>power state |

|-------|-------|-------|----------|----------------|---------------------------------------|---------------------------------------|----------------------------------------------------------------------|------------------------------|

| 0     | 0     | 0     | 0        | Discharge      | N/A                                   | High                                  | OUT baddlaw                                                          | N/A                          |

| 0     | 0     | 0     | 1        | Discharge      | N/A                                   | High                                  | OUT held low                                                         | N/A                          |

| 0     | 0     | 1     | 0        | DCP Auto       | ILIM_H1                               | High                                  | Data lines disconnected                                              | S3/S4/S5                     |

| 0     | 0     | 1     | 1        | DCP Auto       | I <sub>OS_PW</sub> & ILIM_HI          | DCP load preset,<br>held low (Note 8) | Data lines disconnected and Power Wake function active               | S4/S5                        |

| 0     | 1     | 0     | 0        | SDP1           | ILIM_LO                               | High                                  | Data lines connected                                                 | <b>S</b> 3                   |

| 0     | 1     | 0     | 1        | SDP1           | ILIM_H1                               | High                                  | Data lines connected                                                 | S3                           |

| 0     | 1     | 1     | 0        | DCP Auto       | ILIM_H1                               | High                                  | Data lines disconnected                                              | <b>S</b> 3                   |

| 0     | 1     | 1     | 1        | DCP Auto       | ILIM_H1                               | DCP load preset, held low (Note 9)    | Data lines disconnected, Port<br>Power Management function<br>active | \$3                          |

| 1     | 0     | 0     | 0        | DCP<br>Shorted | ILIM_LO                               | High                                  | Device forced to stay in BC1.2                                       | N/A                          |

| 1     | 0     | 0     | 1        | DCP<br>Shorted | ILIM_H1                               | High                                  | shorted mode                                                         | N/A                          |

| 1     | 0     | 1     | 0        | Divider1       | ILIM_LO                               | High                                  | Device forced to stay in Divider1                                    | N/A                          |

| 1     | 0     | 1     | 1        | Divider1       | ILIM_H1                               | High                                  | mode                                                                 | N/A                          |

| 1     | 1     | 0     | 0        | SDP1           | ILIM_LO                               | High                                  |                                                                      | S0                           |

| 1     | 1     | 0     | 1        | SDP1           | ILIM_H1                               | High                                  | Data lines connected                                                 | S0                           |

| 1     | 1     | 1     | 0        | SDP2           | ILIM_LO                               | High                                  |                                                                      | S0                           |

| 1     | 1     | 1     | 1        | CDP            | ILMI_HI                               | CDP load preset <sup>(Note 10)</sup>  | Data lines connected and load detect active                          | S0                           |

Note 7: The current limit setting is automatically switched between IOS\_PW and the resister value on ILIM\_HI according to the Power Wake functionality(for more details see Power Wake).

Note 8: DCP load present governed by the "Load Detection-Power Wake" limits.

Note 9: DCP load present governed by the "Load Detection-Port Power Management".

Note 10: CDP load present governed by the "Load Detection-Port Power Management" and BC1.2 primary detection.

#### **Load Detection**

The APL3524 implements 2 schemes for power management via /STATUS pin by monitoring load current at OUT pin. The 2 schemes are:

- 1. Power Wake.

- 2. Port Power Management.

#### **Power Wake**

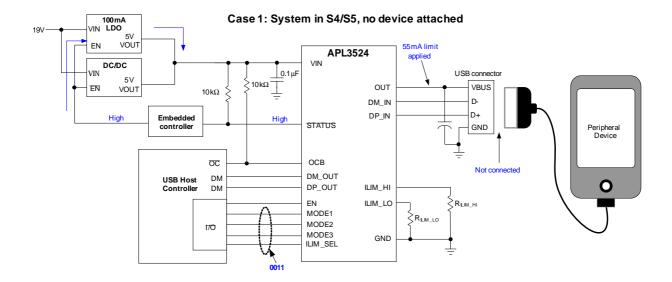

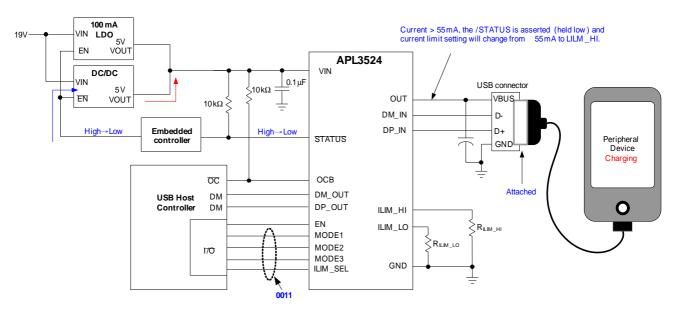

Power Wake function aims to save power for the system when system is in deep sleep state (S4/S5). In general Power Wake function is used mainly in mobile systems like a notebook where it is imperative to save battery power, and therefore battery run time is extended. When the control pins of APL3524 are configured at 0011 (see Truth Table), the Power Wake function is active. The APL3524 will monitor load current at OUT pin and provide /STATUS pin for power path control. As shown in below Case 1 diagram when system is in S4/S5 state and no device is connected to the USB port system is powered by a 100mA LDO (low IQ, high efficiency). In this state the current limit setting of APL3524 is internally fixed at 55mA regardless of ILIM\_HI and ILIM\_LO settings.

When a device is attached, as shown in below Case 2 diagram, and current drawn from OUT exceeds 55mA limitation the APL3524 will assert /STATUS to turn on the main power supply (DC/DC) and discharge VBUS for 2s(typ.). After the discharge the APL3524 will turn back on and then set the current limit at ILIM\_HI. Afterward the DC/DC converter provides the power to the system and charging current to the peripheral.

Case 2: System in S4/S5 device attached and charging

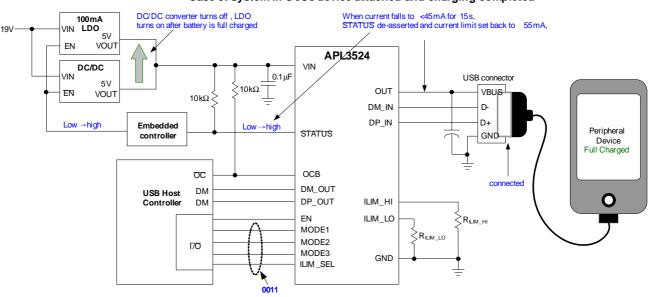

In Case 3, APL3524 will monitor the load current at OUT pin while the peripheral device is in charging state. When the charging current drops below 45mA for a continuous period of 15s, the APL3524 assumes the peripheral device is fully charged and then de-asserts /STATUS and sets the current limit back to 55mA.

Case 3: System in S4/S5 device attached and charging completed

#### **Port Power Management**

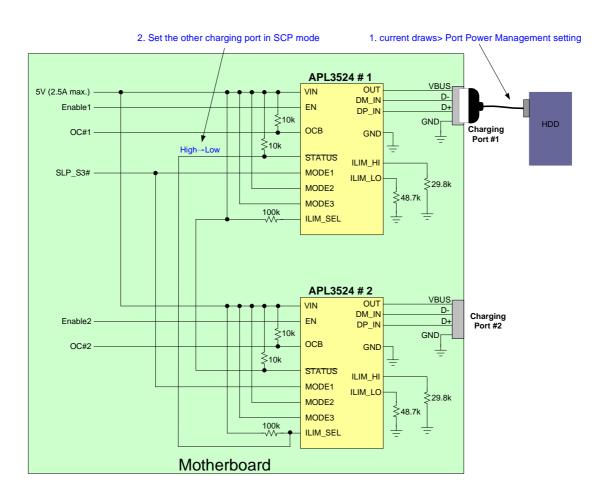

Port Power Management is for systems that deploy multiple charging ports but have load budget that forbids the ports simultaneously to draw high current. The Port Power Management functionality is active when control pins of MODEx, ILIM\_SEL are configured at 0111 or 1111(see Truth Table). When current at OUT exceeds the Port Power Management threshold, or ILIM\_LO+60mA, the /STATUS will be asserted to notify system that high current is present. When the maximum allowed number of ports assert /STATUS, the remaining ports are toggled to a non-charging port. Non-charging port are SDP ports with current limit set by ILIM\_LO. The APL3524 allows a system to toggle between charging and non-charging ports either with or without VBUS discharge. For example when a port is in SDP2 mode (1110) and its ILIM\_SEL pin is toggled to 1 due to another port releasing its high current requirements. The SDP2 port will automatically revert to CDP mode (1111) without a discharge event. This is desirable if this port was connected to a media device where it was syncing data from the SDP2 port; a discharge event would mess-up the syncing activity on the port and cause user confusion.

Figure 5 below is an example of an implementation of Port Power management. The example has two charging ports, each port with its own APL3524. Both ports are all configured at 0111(in S3 state) or 1111(in S0 state) initially, and current limit are all set by ILIM\_HI that can support 1.5A each. In the implement the system's 5V can only support 2.5A maximum, so the current drawn from each port can not reach 1.5A simultaneously. When the load in one of the two ports, in this case the port #1, exceeds ILIM\_LO+60mA for 200ms its /STATUS will be asserted and be received by the port #2. The port #2 receives /STATUS from neighborhood will then be configured in SDP mode and the current limit is set by ILIM\_LO that only supports 0.9A in this case. After the port #1 de-asserts its /STATUS (ex, HDD has been pulled out of port #1), the port #2 will be set back to a charging port. Note that the Port Power Management threshold, ILIM\_LO+60mA, is a threshold used to notify the system when the high power is present but not a current limit threshold. With the implement of Port Power Management in a system the power supply can be designed for a reasonable charging load while providing all ports the high charging capability.

In Case 3, APL3524 will monitor the load current at OUT pin while the peripheral device is in charging state. When the charging current drops below 45mA for a continuous period of 15s, the APL3524 assumes the peripheral device is fully charged and then de-asserts /STATUS and sets the current limit back to 55mA.

Figure 5. Implement of Port Power Management

#### **OCB Output**

The APL3524 provides an open-drain output to indicate that a fault has occurred.

When any of current-limit or over-temperature protection occurs for a deglitch time of  $t_{D(OCB)}$ , the OCB goes low. The OCB keeps in low until the fault has been removed. Since the OCB pin is an open-drain output, connecting a resistor to a pull high voltage is necessary.

#### Enable/Disable

The APL3524 provides an EN input pin for enable/disable control. Pulling the EN pin logic low disables the device. When IC is disabled, the power switch and data switches are all in OFF state, the OUT in discharge and the VIN supply current is educed to less than  $2\mu$ A. The enable input is compatible with both TTL and CMOS logic levels. The EN pin cannot be left floating.

#### **Power Switch**

The power switch is an N-channel MOSFET with a low RDS(ON). The internal power MOSFET does not have the body diode. When IC is off, the MOSFET prevents a current flowing from the VOUT back to VIN and VIN to VOUT.

#### VIN Under-Voltage Lockout (UVLO)

The APL3524 has a built-in under-voltage lockout circuit to keep the output shutting off until internal circuitry is operating properly. The UVLO circuit has hysteresis and a de-glitch feature so that it will typically ignore undershoot transients on the input. When input voltage exceeds the UVLO threshold, the output voltage starts a soft-start to reduce the inrush current.

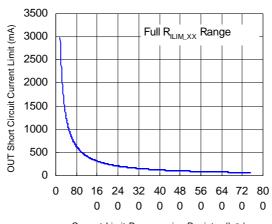

#### **Current-Limits and Settings**

The APL3524 has current limit function to limit load current at current limit threshold in over-load conditions. When device operates in current limiting, the output current is limited and the output voltage is reduced accordingly. At the instant the overload occurs, high currents may flow for microseconds before the current-limit circuit can react. The device has two independent current limit setting pins ILIM\_HI and ILIM\_LO.

Each pin with a resistor to ground sets a current limit threshold. At a time, only one current limit threshold is valid. The ILIM\_SEL input pin is used to choose either ILIM\_HI or ILIN\_LO the candidate of current limit setting. Both settings have the same relation between the current limit and the programming resistor. The following equation programs the typical current limit:

$$I_{CI}$$

(mA) typ.=50250/ $R_{II,IM,XX}$  (k $\Omega$ )

$R_{\text{ILIM\_XX}}$  corresponds to either  $R_{\text{ILIM\_HI}}$  or  $R_{\text{ILIM\_LO}}$  as ILIM\_SEL sets. Please consult the Truth Table to see how ILIM\_SEL relates to ILIM\_HI and ILIM\_LO.

$R_{\text{\tiny ILIM LO}}$  is optional and the ILIM\_LO pin may be left unconnected if the following conditions are met:

- 1. ILIM\_SEL is always set high

- 2. Load Detection Port Power Management is not used

# Typical Current Limit Setting vs. Programming Resistor

Current-Limit Programming Resistor ( $k\Omega$ )

#### **Over-Temperature Protection**

When the junction temperature exceeds  $140^{\circ}$ C, the internal thermal sense circuit turns off the power FET and allows the device to cool down. When the device's junction temperature cools by  $20^{\circ}$ C, the internal thermal sense circuit will enable the device, resulting in a pulsedoutput during continuous thermal protection. Thermal protection is designed to protect the IC in the event ofover temperature conditions. For normal operation, the junction temperature cannot exceed  $T_j=+125^{\circ}$ C.

### **Application Information**

#### **Input Capacitor**

A 1 $\mu$ F or higher ceramic bypass capacitor from VIN to GND, located near the APL3524, is strongly recommended to suppress the ringing during short circuit fault event. When the load current trips the SCP threshold in an over load condition such as a short circuit, hot plug-in or heavy load transient the IC immediately turns off the internal power switch that will cause  $V_{IN}$  ringing due to the inductance between power source and VIN. Without the bypass capacitor, the output short may cause sufficient ringing on the input to damage internal control circuitry.

Input capacitor is especially important to prevent  $V_{IN}$  from ringing too high in some applications where the inductance between power source to VIN is large (ex, an extra bead is added between power source line to VIN for EMI reduction), additional input capacitance may be needed on the input to reduce voltage overshoot from exceeding the absolute maximum voltage of the device during over load conditions.

#### **Output Capacitor**

A low-ESR 150 $\mu$ F aluminum electrolytic or tantalum between VOUT and GND is strongly recommended to reduce the voltage droop during hot-attachment of downstream peripheral. (Per USB 2.0, output ports must have a minimum 120 $\mu$ F of low-ESR bulk capacitance per hub). Higher-value output capacitor is better when the output load is heavy. Additionally, bypassing the output with a 0.1 $\mu$ F ceramic capacitor improves the immunity of the device to short-circuit transients.

#### **Layout Consideration**

The PCB layout should be carefully performed to maximize thermal dissipation and to minimize voltage drop, droop and EMI. The following guidelines must be considered:

- 1. Please place the input capacitors near the VIN pin as close as possible.

- 2. Output decoupling capacitors for load must be placed near the load as close as possible for decoupling high frequency

ripples.

- 3. Locate APL3524 and output capacitors near the load to reduce parasitic resistance and inductance for excellent load transient performance.

- 4. The traces routing the R<sub>ILIM\_XX</sub> resistors should be a sufficiently low resistance as to not affect the current-limit accuracy.

- 5. The negative pins of the input and output capacitors and the GND pin must be connected to the ground plane of the load.

- 6. Keep VIN and VOUT traces as wide and short as possible.

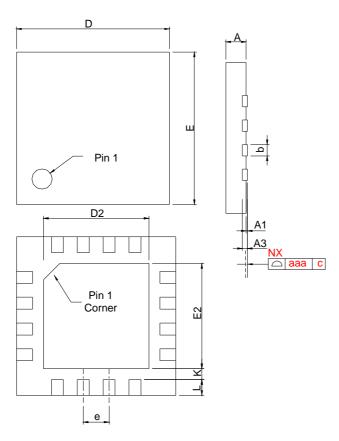

## Package Information

#### TQFN3x3-16

| Ş               | TQFN3*3-16 |        |        |        |  |  |

|-----------------|------------|--------|--------|--------|--|--|

| %> <u>ZmO</u> _ | MILLI      | METERS | INCHES |        |  |  |

| 2               | MIN.       | MAX.   | MIN.   | MAX.   |  |  |

| Α               | 0.70       | 0.80   | 0.028  | 0.031  |  |  |

| A1              | 0.00       | 0.05   | 0.000  | 0.002  |  |  |

| АЗ              | 0.20       | REF    | 0.00   | 8 REF  |  |  |

| b               | 0.18       | 0.30   | 0.007  | 0.012  |  |  |

| D               | 2.90       | 3.10   | 0.114  | 0.122  |  |  |

| D2              | 1.50       | 1.80   | 0.059  | 0.071  |  |  |

| Е               | 2.90       | 3.10   | 0.114  | 0.122  |  |  |

| E2              | 1.50       | 1.80   | 0.059  | 0.071  |  |  |

| е               | 0.50       | ) BSC  | 0.02   | 20 BSC |  |  |

| L               | 0.30       | 0.50   | 0.012  | 0.020  |  |  |

| K               | 0.20       |        | 0.008  |        |  |  |

| aaa             | 0          | .08    | 0.     | 003    |  |  |

Note: Follow JEDEC MO-220 WEED-4.

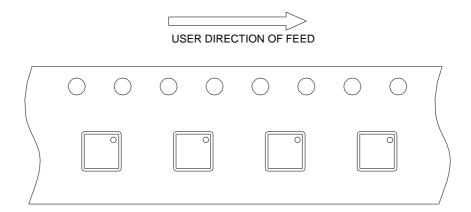

## **Carrier Tape & Reel Dimensions**

| Application | Α        | Н        | T1                 | С                  | d        | D                 | W         | E1        | F         |

|-------------|----------|----------|--------------------|--------------------|----------|-------------------|-----------|-----------|-----------|

|             | 330±2.00 | 50 MIN.  | 12.4+2.00<br>-0.00 | 13.0+0.50<br>-0.20 | 1.5 MIN. | 20.2 MIN.         | 12.0±0.30 | 1.75±0.10 | 5.5±0.05  |

| TQFN3x3-16  | P0       | P1       | P2                 | D0                 | D1       | T                 | A0        | В0        | K0        |

|             | 4.0±0.10 | 8.0±0.10 | 2.0±0.05           | 1.5+0.10<br>-0.00  | 1.5 MIN. | 0.6+0.00<br>-0.40 | 3.30±0.20 | 3.30±0.20 | 1.00±0.20 |

(mm)

### **Devices Per Unit**

| Package Type | Unit        | Quantity |

|--------------|-------------|----------|

| TQFN3x3-16   | Tape & Reel | 3000     |

## **Taping Direction Information**

#### TQFN3x3-16

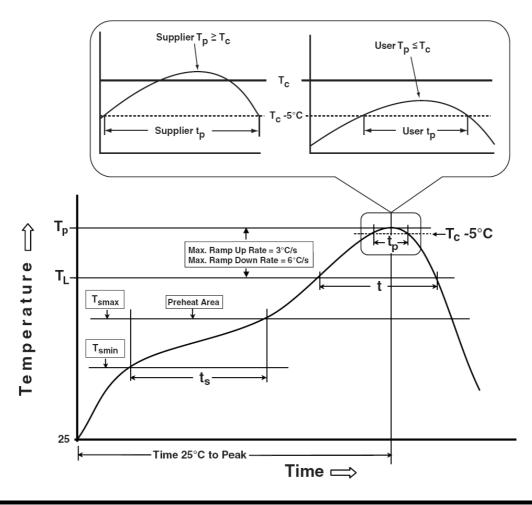

### **Classification Profile**

### **Classification Reflow Profiles**

| Profile Feature                                                                                                                                           | Sn-Pb Eutectic Assembly            | Pb-Free Assembly                   |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------|--|

| Preheat & Soak Temperature min (T <sub>smin</sub> ) Temperature max (T <sub>smax</sub> ) Time (T <sub>smin</sub> to T <sub>smax</sub> ) (t <sub>s</sub> ) | 100 °C<br>150 °C<br>60-120 seconds | 150 °C<br>200 °C<br>60-120 seconds |  |

| Average ramp-up rate (T <sub>smax</sub> to T <sub>P</sub> )                                                                                               | 3 °C/second max.                   | 3 °C/second max.                   |  |

| Liquidous temperature (T <sub>L</sub> )<br>Time at liquidous (t <sub>L</sub> )                                                                            | 183 °C<br>60-150 seconds           | 217 °C<br>60-150 seconds           |  |

| Peak package body Temperature (T <sub>p</sub> )*                                                                                                          | See Classification Temp in table 1 | See Classification Temp in table 2 |  |

| Time (t <sub>P</sub> )** within 5°C of the specified classification temperature (T <sub>c</sub> )                                                         | 20** seconds                       | 30** seconds                       |  |

| Average ramp-down rate (T <sub>p</sub> to T <sub>smax</sub> )                                                                                             | 6 °C/second max.                   | 6 °C/second max.                   |  |

| Time 25°C to peak temperature                                                                                                                             | 6 minutes max.                     | 8 minutes max.                     |  |

| * Tolerance for peak profile Temperature (Tp) is defined as a supplier minimum and a user maximum.                                                        |                                    |                                    |  |

Table 1. SnPb Eutectic Process - Classification Temperatures (Tc)

| Package   | Volume mm <sup>3</sup> | Volume mm <sup>3</sup> |

|-----------|------------------------|------------------------|

| Thickness | <350                   | <sup>3</sup> 350       |

| <2.5 mm   | 235 °C                 | 220 °C                 |

| ≥2.5 mm   | 220 °C                 | 220 °C                 |

Table 2. Pb-free Process – Classification Temperatures (Tc)

| Package<br>Thickness | Volume mm <sup>3</sup><br><350 | Volume mm <sup>3</sup><br>350-2000 | Volume mm <sup>3</sup> >2000 |

|----------------------|--------------------------------|------------------------------------|------------------------------|

| <1.6 mm              | 260 °C                         | 260 °C                             | 260 °C                       |

| 1.6 mm – 2.5 mm      | 260 °C                         | 250 °C                             | 245 °C                       |

| ≥2.5 mm              | 250 °C                         | 245 °C                             | 245 °C                       |

## **Reliability Test Program**

| Test item     | Method             | Description                            |

|---------------|--------------------|----------------------------------------|

| SOLDERABILITY | JESD-22, B102      | 5 Sec, 245°C                           |

| HOLT          | JESD-22, A108      | 1000 Hrs, Bias @ T <sub>j</sub> =125°C |

| PCT           | JESD-22, A102      | 168 Hrs, 100%RH, 2atm, 121°C           |

| TCT           | JESD-22, A104      | 500 Cycles, -65°C~150°C                |

| НВМ           | MIL-STD-883-3015.7 | VHBM≥2KV                               |

| MM            | JESD-22, A115      | VMM≥200V                               |

| Latch-Up      | JESD 78            | 10ms, $1_{tr} \ge 100 \text{mA}$       |

<sup>\*\*</sup> Tolerance for time at peak profile temperature (tp) is defined as a supplier minimum and a user maximum.

### **Customer Service**

#### **Anpec Electronics Corp.**

Head Office:

No.6, Dusing 1st Road, SBIP, Hsin-Chu, Taiwan, R.O.C. Tel: 886-3-5642000 Fax: 886-3-5642050

#### Taipei Branch:

2F, No. 11, Lane 218, Sec 2 Jhongsing Rd., Sindian City, Taipei County 23146, Taiwan

Tel: 886-2-2910-3838 Fax: 886-2-2917-3838